R / 2nR DAC:バイナリ加重入力デジタル-アナログコンバータ

R / 2nR DAC回路とは何ですか?

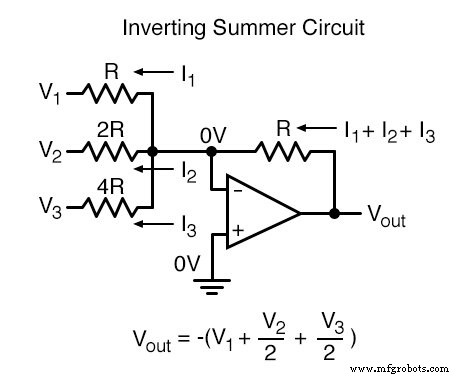

R / 2nR DAC回路、別名バイナリ加重入力 DACは、反転加算オペアンプ回路のバリエーションです。 (「合計」回路は「夏」回路と呼ばれることもあることに注意してください。)

思い出してください。古典的な反転加算回路は、制御されたゲインに負帰還を使用するオペアンプであり、複数の電圧入力と1つの電圧出力を備えています。出力電圧は、すべての入力電圧の逆(反対の極性)の合計です:

単純な反転加算回路の場合、すべての抵抗は同じ値である必要があります。入力抵抗のいずれかが異なる場合、入力電圧は出力に異なる程度の影響を及ぼし、出力電圧は真の合計にはなりません。

例:複数の入力抵抗値を持つR / 2nR DAC

ただし、意図的に入力抵抗を異なる値に設定することを検討してみましょう。入力抵抗値を、すべて同じ値Rではなく、R、2R、および4Rの2の累乗に設定するとします。

V 1 から開始 そしてV 3 を通過します 、これにより、各入力電圧は、その前の電圧のちょうど半分の出力への影響を与えます。つまり、入力電圧V 1 入力電圧V 2 に対して、出力電圧に1:1の影響(ゲイン1)があります。 出力にその半分の影響(1/2のゲイン)があり、V 3 その半分(1/4のゲイン)。

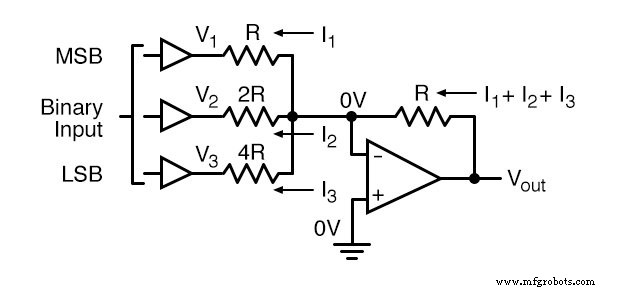

これらの比率は任意に選択されたものではありません。これらは、2進記数法の場所の重みに対応する同じ比率です。この回路の入力をデジタルゲートで駆動して、各入力が0ボルトまたは完全供給電圧になるようにすると、出力電圧はこれら3ビットのバイナリ値のアナログ表現になります。

この回路に入力されたバイナリビット(000〜111)の8つの組み合わせすべての出力電圧をグラフ化すると、次の電圧の進行が得られます。

-------------- |バイナリー|出力電圧| ----------- | 000 | 0.00 V | -------------- | 001 | -1.25 V | ------------------ | 010 | -2.50 V | -------------- | 011 | -3.75 V | ------------------ | 100 | -5.00 V | -------------- | 101 | -6.25 V | ------------------ | 110 | -7.50 V | -------------- | 111 | -8.75 V | ------------------

バイナリカウントシーケンスの各ステップで、出力に1.25ボルトの変化が生じることに注意してください。

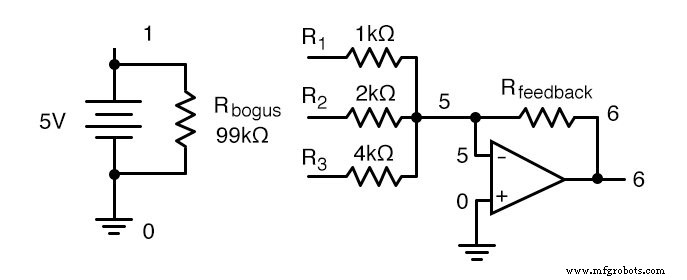

この回路は、SPICEを使用して非常に簡単にシミュレートできます。次のシミュレーションでは、110のバイナリ入力を使用してDAC回路を設定しました(抵抗R 1 の最初のノード番号に注意してください)。 、R 2 、およびR 3 :ノード番号「1」はそれを5ボルトのバッテリーのプラス側に接続し、ノード番号「0」はそれをアースに接続します)。

出力電圧は、シミュレーションのノード6に表示されます:

バイナリ加重dacv1 1 0 dc 5 rbogus 1 0 99k r1 1 5 1k r2 1 5 2k r3 0 5 4k rfeedbk 5 6 1k e1 6 0 5 0 999k .endノード電圧ノード電圧ノード電圧(1)5.0000 (5)0.0000(6)-7.5000

この回路の抵抗値を調整して、バイナリ入力に直接対応する出力電圧を取得できます。たとえば、フィードバック抵抗を1kΩではなく800Ωにすると、DACはバイナリ入力001に-1ボルト、バイナリ入力100に-4ボルト、バイナリ入力111に-7ボルトなどを出力します。

(フィードバック抵抗を800オームに設定)------ |バイナリー|出力電圧| ---------------- | 000 | 0.00 V | ------------ | 001 | -1.00 V | ---------------- | 010 | -2.00 V | ------------ | 011 | -3.00 V | ---------------- | 100 | -4.00 V | ------------ | 101 | -5.00 V | ---------------- | 110 | -6.00 V | ------------ | 111 | -7.00 V | --------------------------------

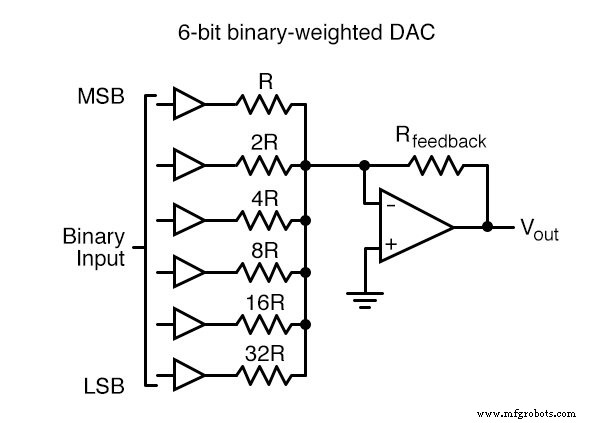

このDACの分解能を拡張したい場合(入力にビットを追加したい場合)、必要なのは、同じ2の累乗の値のシーケンスを保持したまま入力抵抗を追加することだけです。

「ハイ」状態では、すべての論理ゲートがまったく同じ電圧を出力する必要があることに注意してください。 1つのゲートが「ハイ」に対して+5.02ボルトを出力し、別のゲートが+4.86ボルトしか出力しない場合、DACのアナログ出力に悪影響があります。

同様に、すべての「低」電圧レベルはゲート間で同一である必要があり、理想的には正確に0.00ボルトです。 CMOS出力ゲートを使用し、各ゲートがソースまたはシンクする必要のある電流量を最小限に抑えるように入力/フィードバック抵抗値を選択することをお勧めします。

産業技術