高速デジタル回路の PCB 設計におけるインピーダンス制御

インピーダンス制御技術は、高速 PCB の優れた性能を確保するために効果的な方法を採用する必要がある高速デジタル回路設計において非常に重要です。

PCB 上の高速回路伝送ラインのインピーダンス計算とインピーダンス制御

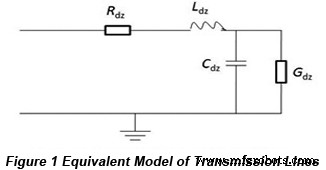

• 送電線の等価モデル

図 1 は、タンデムおよび複数のコンデンサ、抵抗器、およびインダクタ (RLGC モデル) を含む構造である PCB 上の伝送線路の等価効果を示しています。

タンデム抵抗の典型的な値は 0.25 から 0.55 オーム/フィートの範囲であり、複数の抵抗器の抵抗値は通常非常に高いままです。 PCB 伝送ラインに寄生抵抗、キャパシタンス、およびインダクタンスが追加されると、伝送ラインの全体的なインピーダンスは特性インピーダンス (Z0) と呼ばれます。 )。特性インピーダンスの値は、線路の直径が大きい場合、線路が電源/グランドに近い場合、または誘電率が高い場合に比較的小さくなります。図 3 は、長さ dz の伝送線路の等価モデルを示しています。これに基づいて、伝送線路の特性インピーダンスを式として推定できます。  .この式では、L は伝送線路の各単位長のインダクタンスを表し、C は伝送線路の各単位長の静電容量を表します。

.この式では、L は伝送線路の各単位長のインダクタンスを表し、C は伝送線路の各単位長の静電容量を表します。

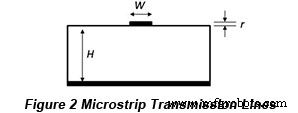

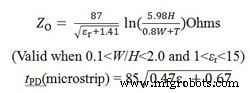

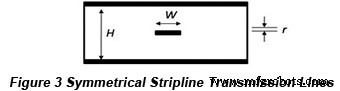

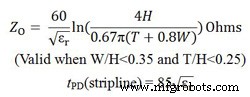

• PCB 上の伝送線路のインピーダンスと遅延の計算式

| PCB 上の伝送ライン | インピーダンスと遅延の計算式 |

|  |

|  |

上記の式では、Z0 インピーダンス (オーム) を指し、W はラインの幅 (インチ) を指し、T はラインの厚さ (インチ) を指し、H は地面までの距離 (インチ) を指し、基板の比誘電率を指します。そしてPD 遅延時間 (ps/インチ) を指します。

• 送電線のインピーダンス制御配置規則

上記の分析に基づくと、インピーダンスと信号の単位遅延は、信号の周波数とは無関係ですが、基板構造、基板材料の比誘電率、配線の物理的属性に関連しています。この結論は、高速 PCB を理解し、高速 PCB 設計を行う上で非常に重要です。さらに、外層の信号伝送ラインの伝送速度は内層よりもはるかに速いため、これらの要素を考慮してキー ライン レイアウトを配置する必要があります。

信号伝送を実現する上で、インピーダンス制御は大前提です。ただし、基板構造と伝送線路のインピーダンス計算式によると、インピーダンスは PCB 材料と PCB 層構造にのみ依存し、同じ線路の線幅と配線機能は変更されません。したがって、ラインのインピーダンスは、高速回路設計では許可されていない、PCB のさまざまな層で変化しません。

高密度の高速 PCB がこの記事用に設計されており、ボード上のほとんどの信号にはインピーダンス要件があります。たとえば、CPCI 信号ラインのインピーダンスは 65Ω、差動信号は 100Ω、その他の信号はすべて 50Ω にする必要があります。 PCB 配線スペースに従って、少なくとも 10 層の配線を使用する必要があり、16 層の PCB 設計計画が決定されます。

ボードの全体の厚さが 2mm を超えることはできないため、いくつかの問題を考慮して積み重ねるという点でいくつかの困難があります:

1)。各信号層には、インピーダンスと信号品質を保護するために隣接するイメージ プレーンがあります。

2)。各電源プレーンの隣には完全なグランド層があり、電源のパフォーマンスを十分に確保できます。

3)。ボードの積み重ねにはバランスが必要で、ボードの反りは避けてください。

媒体の誘電率は 4.3 に設定されます。上記のスタッキング設計に基づいて、信号インピーダンスの要件を確保するために、計算結果に従ってライン幅とライン間の距離を設定する必要があります。線幅は次の結果として得られます:

1)。表面層の信号線の幅は 5 ミルで、インピーダンスは 58.7 オームです。

2)。表層の CPCI 信号線の幅は 4.5 ミルで、インピーダンスは 61.7 オームです。

3)。内層の信号線の幅は 4.5 ミルで、インピーダンスは 50.2 オームです。

4)。内層と表層の BGA 領域のライン幅は 4 ミルで、表層インピーダンスは 64.6 オーム、内層インピーダンスは 52.7 オームです。

5)。内層のマイクロストリップ差動ラインの幅は 5 ミルで、ライン間の距離は 6 ミル、インピーダンスは 100.54 オームです。

6)。内層のストリップライン差動ラインの幅は 4.5 ミルで、ライン間の距離は 10 ミル、インピーダンスは 96.6 オームです。

行間の距離は次のように設定されます:

1)。表層の信号線間の距離 (5 ミル) は 5.0 ミルです。

2)。表層の CPCI 信号線 (4.5 ミル) 間の距離は 9.0 ミルです。

3).. 内層の信号線 (4.5 ミル) 間の距離は 7.0 ミルです。

4)。表層と内層のライン間の距離は 4.0 ミルです。

5)。内層の差動信号ライン間、およびそれらと他の信号ライン間の距離は、少なくとも 25mils に保つ必要があります。

6)。表層の差動信号ライン間、およびそれらと他の信号ライン間の距離は、少なくとも 20mils に保つ必要があります。

PCB 印刷後、テスト ボードのインピーダンスを POLAR-Cits500 インピーダンス テスターでテストし、結果を次の表に示します。このデータは、高速 PCB の設計と製造の過程で、インピーダンスを 50Ω%、60Ω%、100Ω% の範囲で制御する必要があることを示しています。

| プリセット インピーダンス (オーム) | 実用インピーダンス (オーム) |

| 50 | 47.52-52.33 |

| 60 | 57.65-61.35 |

| 100 | 93.65-106.35 |

PCB 上の LVDS とそのインピーダンス制御

•LVDS

LVDSは、高速シリアル信号伝送レベルの一種であり、高速伝送速度、低消費電力、強力な干渉防止能力、長い伝送距離、および実現可能なマッチングという利点があります。 LVDS の応用分野には、コンピュータ、通信、および消費が含まれます。

• LVDS のインピーダンス設計

LVDS は、わずか 350MV の電圧スイングで、最長伝送距離は 10 メートルを超えます。伝送線路を信号が伝送される過程で、信号が反射信号の影響を受けないようにするために、伝送線路のインピーダンスは、単線インピーダンス 50 Ω、差動インピーダンス 100 Ω に制御する必要があります。実際のアプリケーションでは、合理的なスタッキングの厚さと媒体パラメータを設定し、ライン幅とライン間の距離を調整し、いくつかの高速シミュレーション解析ツールを使用して単一ラインと差動ラインのインピーダンスを計算することにより、インピーダンスを制御できます。

ただし、ほとんどの場合、単線インピーダンスと差動インピーダンスの要件を満たすことは比較的困難です。一方では、線幅 W と線間距離 S の調整範囲は、物理的な設計空間によって制御されます。たとえば、BGA または DIP を使用したマージン コネクタの配線と線幅は、パッドのサイズと距離の影響を受けます。一方、W と S の変化は、単線インピーダンスと差動インピーダンスの結果に影響を与えます。これまでのところ、事前に設定された線幅と線の距離の関係を把握するのは簡単で便利です。

• LVDS ルーティング ルール

一般的に、差動信号ルーティングは、LVDS の品質を確保できるインピーダンス設計ルールに従って実装されます。実際の配線では、LVDS は次の規則に従う必要があります。

1)。差動ペアはできるだけ短くし、ラインをまっすぐにし、スルー ホールの数を減らす必要があります。差動ペアの信号線間の距離は同じでなければなりません。これらのルールはすべて、長いルーティングと多数のターンオフを回避するのに役立ちます。ターンオフに関しては、90 度の代わりに 45 度のターンオフを使用する必要があります。

2)。ライン間のクロストークを減らすために、差動ペア間の距離を 10 倍以上維持する必要があります。必要に応じて、グランド スルー ホールを差動ペア間に配置して絶縁することができます。

3)。 LVDS は表面全体に分割できません。 2 つの差動信号は相互の帰路となりますが、面分割により信号の帰路を削減することはできません。それにもかかわらず、伝送線路は、イメージ プレーンの欠如の結果として、インピーダンスの不連続につながる可能性があります。

4)。レイヤー間の差動信号を避けてください。 PCB 製造中、レイヤー間のスタッキング アライメント精度は、同じレイヤーでのエッチング精度にスタッキング中の中間損失を加えたものよりもはるかに低く、これらすべてが差動ペア間の差動インピーダンスの変化につながります。

5)。インピーダンス設計では、カップリング法を使用する必要があります。

6)。電圧レベル信号と LVDS 間の絶縁を確保するために、適切な PCB スタック構造を設定する必要があります。可能であれば、高速 TTL/CMOS などの信号を異なるレイヤーに設定し、グランド層と電源層によって LVDS ルーティングから分離することができます。

7)。差動信号ペアは、ルーティングの長さと互換性がある必要があります。

役立つリソース

• PCB およびソリューションの特性インピーダンスに影響を与える要素

• フレックスリジッド PCB のインピーダンス設計に関する考慮事項

• 高速 PCB 電源のインピーダンスを分析して禁止する方法

•ビアのインピーダンス制御と PCB 設計におけるシグナル インテグリティへの影響

• PCBCart のフル機能 PCB 製造サービス - 複数の付加価値オプション

• PCBCart の高度な PCB アセンブリ サービス - 1 個から開始

産業技術