組み込みアプリケーション システムにおける高速 PCB 設計に関する研究

現代の電子システムは、SLSI (超大規模集積) におけるチップの高密度化に伴い、パッケージの小型化、大規模化、高速化の傾向の中で発展しています。高速回路設計における相互接続とスタッキングの問題。現在、電子製品の無線周波数は数百または数千 MHz に達し、立ち上がりエッジと立ち下がりエッジの両方が非常に急峻になっているため、PCB レイアウト規則と基板材料の誘電率は、プロセス設計におけるシステムの電気的性能にとって非常に重要です。

現在の電子製品研究の大部分における重要なプロセスおよびステップとして、高速 PCB 設計は、タイミングの問題、ノイズ干渉、EMI (電磁干渉) などの主な問題を認識しており、その解決策はシステム設計の通常の動作に関連しています。

現在、従来の設計方法では、製品の信頼性と成功率が低くなり、組み込みアプリケーション システムにおける高速 PCB 設計の研究に対して、高い実用的価値と幅広い市場の期待がもたらされています。

システム スキームの設計

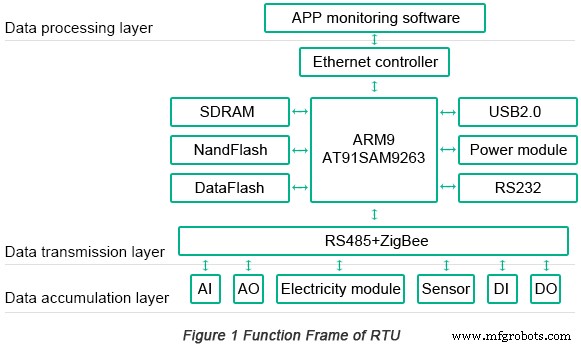

図 1 に組み込み RTU (リモート端末ユニット) の機能フレームを示します。

図1からわかるように、本システムは、電力エネルギーユニット、センサーユニット、アナログ量計測ユニットを含むデータ蓄積層と、データ蓄積層のデータを介してデータを調整するゲートウェイを含むデータ伝送層からなる垂直通信構造であることがわかります。インターネット受信エンジニア センターからのコマンドと、APP 監視ソフトウェアによって実装されるデータ処理層、データをリアルタイムで保存および分析し、ユーザー インターフェイスに面するデータ曲線を作成して、データ蓄積の柔軟性と管理効率を高めます。

RTU システム ハードウェア フレーム

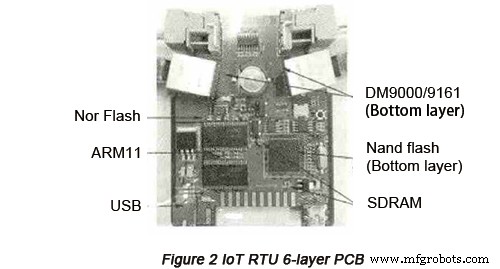

この組み込み IoT RTU システム ハードウェアは、主に USB2.0、AT91SAM9263 プロセッサ、CAN、SDRAM、Nand フラッシュ、データ フラッシュ、イーサネット コントローラ、クロック チップ、RS232/485 インターフェイス、電源管理およびデータ蓄積部品で構成されています。

Linux オペレーティング システムで動作するこの設計は、ネットワーク接続、データ通信、および構成の蓄積を担当する複雑なアルゴリズムと通信プロトコルを含むマルチミッション リアルタイム スケジューリングが実装されるように、メモリとデバイス管理のより高い機能を備えています。図 2 は、この記事で設計した RTU 回路基板です。

IPv6とIPv4のデュアルスタックに対応し、迅速性とリアルタイム性を実現したシステムです。データストレージに関しては、ローカルストレージの要件は、通信ブロックの条件下で満たすことができます。通信インターフェースに関しては、RS485、RS232、CAN などのさまざまなフィールド データ通信インターフェースを備えており、Modbus RTU 通信プロトコルをサポートし、さまざまなインターフェースとさまざまな通信速度の要件を満たしています。

RTU システムの PCB 設計

• システムの PCB スタックアップ設計

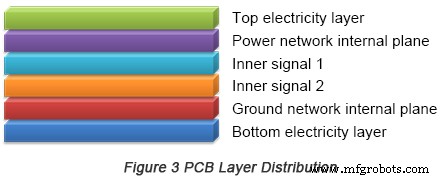

PCB の層数は、設計の難しさに基づいて、通常 2 から 32 の範囲です。この設計の 6 層 PCB は、コンポーネント パッケージ密度、小さなレイアウト ルーティング スペース、および高い信号周波数に応じて決定されます。この PCB 層の分布は、以下の図 3 に示されています。

このシステムでは、FLASH と SDRAM のストリップ ライン構成が選択され、内部信号 1 と内部信号 2 にルーティングが実装されます。

• このシステムにおける PCB 制約規則

高速 PCB 設計中、インピーダンスの連続性と EMI は、ワイヤの間隔、長さと幅、およびループの隣接処理によって大きく影響を受けます。コンポーネントのレイアウトと配線の品質は、最終設計の成功に関係するため、PCB 制約規則を合理的に制定する必要があります。

Hyper Lynx は、チャート分析に干渉する機能を備えており、IBIS モデルを適用して、損失伝送、差動信号、および周波数によって変化するスルーホール モデルを正確にシミュレートできます。メイン ネットワークは、PCB スタッキング構造とルーティング インピーダンスを改善するために Line によるルーティングの前にシミュレートされ、シミュレーション結果の前に高速 PCB ネットワークのルーティング制約ルールが設計され、設計効率が向上します。

• このシステムの PCB シミュレーション

高速 PCB 設計のプロセスでは、理想的な伝送線路モデルがフロント ターミナル シミュレーションに適用され、一度にシミュレートされる信号線は限られています。しかし、基板裏面端子の伝送線路は、実際にはスルーホールやプレーンシフトの影響を受けて基板の引き回し線となっています。この状況下で得られたシミュレーション結果は非常に信頼できます。

システムのコア回路設計の過程で、片端子信号の端子整合抵抗は40~60Ω、信号線間のクロストーク閾値は165mVが要求されます。また、DM9000 および DM9161 のネットワーク コントローラを 100Mbps の通信速度レートに自己適応させるには、差動インピーダンスが 100±5Ω のカテゴリ内にある必要があります。 PCB シミュレーションは、Mentor Graphic が開発した SDRAM、イーサネット差動回線、電源の完全性、および EMC に関する Hyper Lynx シミュレーション ソフトウェアによって実装されます。

を。 SDRAM 設計

ストリップ ラインの設計プロセスでは、クロストークとスルー ホールが時間遅延につながる主な原因です。配線シミュレーションツールで決められた配線ルール通りにPCBが完成しても、部品のピン数が多すぎたり、PCBの寸法が制限されたりすることは避けられません。したがって、ボード シミュレーション ツールを使用して複数のネットワークを適切にシミュレートする必要があります。

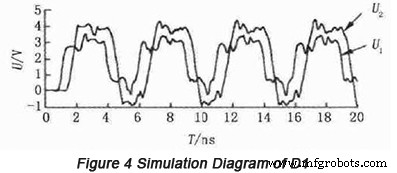

シミュレーション結果に基づくと、アナログ ネットワーク EBI_D0 および EBI_D2 のクロストーク強度は 165mV を超えています。 2 つのネットワークは、黄色のマーキング エリア内の蛇行の間隔が適切でないため、EBI_D1 を攻撃して結合場所を検索します。配線間隔を増やすと、このような問題を解消できることがわかります。しかし、私たちが本当に気にかけているのは、なぜハッキング ネットワークがこれほど強い干渉を受けるのかということです。その理由は、不整合インピーダンスにつながる不適切な抵抗の選択にある可能性があります。これまでのところ、終端抵抗の決定された抵抗値は 43.1Ω です。 220MHz 励振条件でのネットワーク EBI_D1 の解析シミュレーション波形を下図 4 に示します。

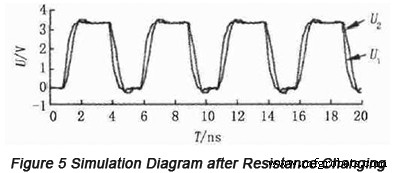

図 4 から、EMI_D1 伝送線路にインピーダンスの不連続が発生し、信号波に変形が発生します。起動のシステム障害が発生することはありませんが、製品の動作の安定性はほとんど保証されません。 EBI_D0とEBI_D1の終端抵抗を46.9Ωに変更するために、Back to Boardシミュレーション、スルーホールおよび損傷シミュレーションが適用されます。したがって、抵抗値を変更した後のクロストークのシミュレーション図を下の図 5 に示します。

この図に基づいて、ネットワーク信号が改善され、EBI_D1 で引き起こされた干渉強度が明らかに減少したことを示すことができます。

b.インターネット差動バス設計

Hyper Lynx が開発したボード シミュレーション モジュールは、高速および 3GIO 相互接続の属性を備えており、差動信号バスに基づく超高速シリアル データ パスとソース同期テクノロジを適用し、高速 PCB 設計に便利で非常に効果的な解決方法を提供します。このシステムの DM9000 と DM9161 の両方に、差動インピーダンスが 100Ω の TX+、TX- および RX+、RX- の 2 組の高速信号差動バスがあります。伝送理論により、差動インピーダンスは次の式に基づいて計算できます。  .

.

この式で、Z は各信号線の伝送インピーダンスを指し、通信距離と耐ノイズ性に重要な影響を与えます。ここで、DM9000 はネットワーク TP_E_TX+ および TP_E_TX- に差分を送信するためにピックアップされます。反射の影響を軽減するため、スルーホールを施した信号線に100Ωの抵抗を並列に配置しています。

c.このシステムのパワー インテグリティ設計

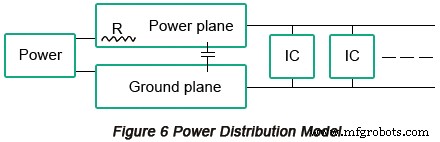

図 6 は、電流が電力層を介して各キャリアに伝送され、次に接地層に伝送される基本的な電力分布モデルです。

高速 PCB 設計のプロセスでは、各ユニットのエネルギー消費は、電力ネットワークの幅が正しく分散され、適切に増幅された回路システムで計算する必要があります。

6 層の電力の完全性は次のように要約できます。最大圧力降下は 2.1mV で、0.06% に近いです。電流の最大密度は 16.3mA/m² です。適切なカテゴリ内で、電流密度が 50 mA/m² を超えると、PCB の温度が上昇し、動作中のメイン チップと信号ラインに影響を与えます。銅幅の増加は電流密度を減少させることができ、信号リードの厚さの増加は PCB の温度の低下に役立ちます。

d.システム電磁両立性解析

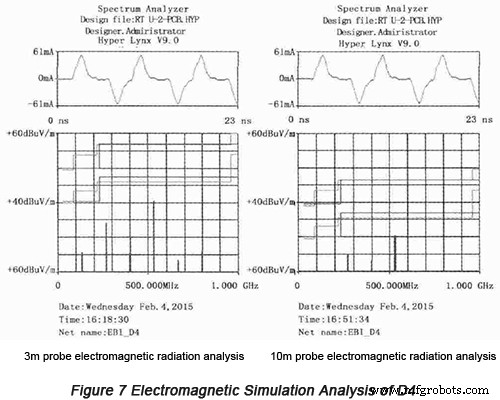

電磁干渉は通常、カップリングの途中で有用な信号を含む搬送波として送信されます。この設計では、Hyper Lynx シミュレーション ソフトウェアを適用して、予備設計後に PCB の放射強度を解析します。重要な信号線である D4 は、プローブ位置がそれぞれ 3m と 10m の ARM9 と SDRAM の間でピックアップされます。 220MHz の励起源の状況下では、FCC と CISPR の両方の国際標準シミュレーション データを取得できます。これを下の図 7 に示します。

シミュレーション結果に基づくと、PCB までの距離が短いと、回路基板からの放射が高くなり、放射は信号周波数の変化に伴って変化します。高速回路設計のプロセスでは、ノイズ放射を低減する必要がある一方で、PCB の干渉防止を最適化できます。

役立つリソース

• 高速レイアウトのヒント

• EMI の影響を軽減するための高速 PCB ルーティング テクニック

• 高速 PCB 設計に関する誤解と戦略

• コンポーネントの埋め込みPCB 製造技術

• 組み込み技術とコンポーネント組み込み PCB アセンブリ手順

• PCBCart のフル機能 PCB 製造サービス - 複数の付加価値オプション

• PCBCart の高度な PCB アセンブリ サービス - 1 個から開始

産業技術