すべての動作コードは module 内に記述されています と endmodule .したがって、どのようなデジタル デザインを作成しようとしても、module 内に配置されます。 ブロック。ポートが定義されている場合と定義されていない場合があります - 信号が input としてブロックに入ることを許可します または output としてブロックをエスケープします . モジュール 以下の例の空のモジュールは testbench と呼ばれます .任意の名前を付けることができますが、英数字にする必要があり、_ を含めることができます。 module testbench; endm

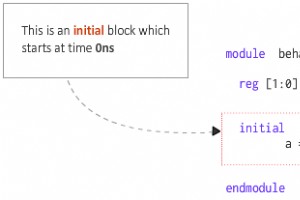

Verilog ステートメントのセットは、通常、シミュレーションで順番に実行されます。これらのステートメントはプロシージャル内に配置されます ブロック。 手続き型には主に2つのタイプがあります Verilog のブロック - 初期 そして常に 構文 initial [single statement] initial begin [multiple statements] end 最初のブロックは何に使用されますか? initial ブロックは合成できないため、デジタル要素を含むハードウェア回路図に変換できません。したがって、初期ブロックは、シミュレーショ

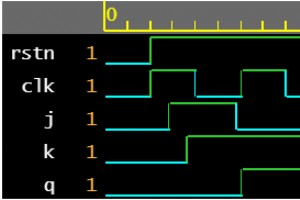

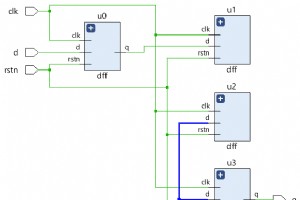

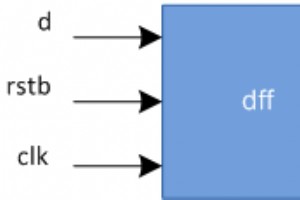

以前の記事では、 always を使用するさまざまな例を示しました 組み合わせロジックを実装するためのブロック。 always ブロックは主に シーケンシャル の実装にも使用されます 値を保持できるフリップフロップなどのメモリ要素を持つロジック。 JK フリップフロップ JK フリップフロップは、値を格納するために使用される多くのタイプのフロップの 1 つであり、リセット rstn 用とクロック clk 用に 1 つずつ、2 つのデータ入力 j と k を備えています。 JK フロップの真理値表を以下に示します。これは通常、NAND ゲートを使用して実装されます。 rstn j k q

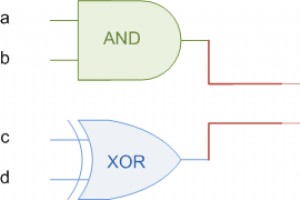

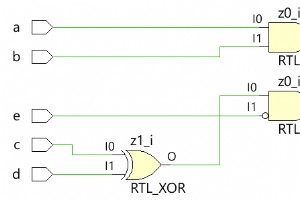

verilog の always ブロックは、シーケンシャル ロジックと組み合わせロジックの両方に使用できます。 assign を使用したいくつかの設計例を示しました。 以前の記事での発言。次に always を使用して、同じデザインのセットを調べます。 ブロックします。 例 #1 :シンプルな組み合わせロジック 以下に示すコードは、タイプ reg の z と呼ばれる出力信号を持つ単純なデジタル組み合わせロジックを実装します。 これは、感度リスト内のシグナルの 1 つがその値を変更するたびに更新されます。センシティビティ リストは、@ の後の括弧内で宣言されます。 module

always ブロックは 手続き型 の 1 つです Verilog のブロック。 always ブロック内のステートメントは順番に実行されます。 構文 always @ (event) [statement] always @ (event) begin [multiple statements] end always ブロックは特定のイベントで実行されます。イベントは機密リストによって定義されます。 機密リストとは? 感受性 list は、always ブロックをいつ実行するかを定義する式で、@ の後に指定します。 括弧内の演算子 ( ) .このリストには、値の変

連結を使用して、マルチビット Verilog ワイヤと変数をまとめて、より大きなマルチネット ワイヤまたは変数を形成できます。 演算子 { と } カンマで区切られた。連結では、ワイヤと変数に加えて、式とサイズ定数をオペランドとして使用することもできます。 連結の完全なサイズを計算するには、各オペランドのサイズを知る必要があります。 Verilog 連結の例 wire a, b; // 1-bit wire wire [1:0] res; // 2-bit wire to store a and b // res[1] follows a, and res[

処理できないデータはまったく役に立ちません。デジタル回路やコンピューター システムでは、常になんらかの計算が必要になります。合成ツールが適切なハードウェア要素を実現できるようにする Verilog の演算子のいくつかを見てみましょう。 Verilog 算術演算子 除算または剰余演算子の 2 番目のオペランドがゼロの場合、結果は X になります。累乗演算子のいずれかのオペランドが実数の場合、結果も実数になります。累乗演算子の第 2 オペランドが 0 (a0 ). 演算子 説明 a + b プラスb a - b a マイナス b a * b a に b を掛けたもの a /

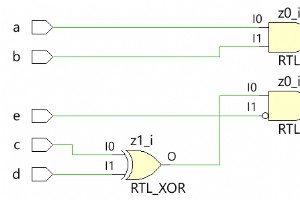

verilog の assign ステートメントは、通常、wire の信号を継続的に駆動するために使用されます。 データ型であり、組み合わせロジックとして合成されます。 assign を使用したその他の設計例を次に示します。 例 #1 :シンプルな組み合わせロジック 以下に示すコードは、assign で連続的に駆動される出力ワイヤ z を持つ単純なデジタル組み合わせロジックを実装します。 デジタル式を実現するステートメント module combo ( input a, b, c, d, e, output z); assign z = ((a & b)

タイプ wire のシグナル または同様のワイヤのようなデータ型では、値を連続して割り当てる必要があります。たとえば、ブレッドボード上の部品を接続するために使用される電線を考えてみましょう。 +5V バッテリーがワイヤの一方の端に接続されている限り、ワイヤのもう一方の端に接続されたコンポーネントは必要な電圧を取得します。 Verilog では、この概念は assign によって実現されます。 ステートメント where any wire または他の同様のワイヤのようなデータ型は、値で連続的に駆動できます。値は、定数またはシグナルのグループで構成される式のいずれかです。 構文を割り当てる

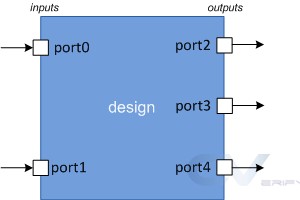

以前の記事で説明したように、より大規模で複雑な設計は、複数のモジュールを階層的に統合することによって構築されます。モジュールはインスタンス化できます これらのインスタンスの他のモジュールおよびポート内 親モジュール内の他の信号と接続できます。 これらのポート接続は、番号付きリストまたは名前で行うことができます。 番号付きリストによるポート接続 モジュールのインスタンス化にリストされているポート式と親モジュール内のシグナルとを関連付ける方法の 1 つは、順序付けられたリストを使用することです。 . mydesign は module です tb_top という別のモジュールで d0 という

ポートは、特定のモジュールへの入力および出力として機能する一連の信号であり、モジュールと通信する主要な方法です。モジュールを PCB に配置された加工済みチップと考えると、チップと通信する唯一の方法がそのピンを介することであることが明らかになります。ポートはピンのようなもので、外部からの信号を送受信するために設計によって使用されます。 港の種類 ポート 説明 入力 設計モジュールは、input を使用して外部からのみ値を受け取ることができます ポート 出力 設計モジュールは、output を使用して外部に値を送信することしかできません。 ポート インアウト 設計モジュールは

module 特定の機能を実装する Verilog コードのブロックです。モジュールは他のモジュール内に組み込むことができ、上位レベルのモジュールは、入力ポートと出力ポートを使用して下位レベルのモジュールと通信できます。 構文 モジュール module で囲む必要があります と endmodule キーワード。モジュールの名前は module の直後に指定する必要があります キーワードとオプションのポートのリストも宣言できます。ポート宣言のリストで宣言されたポートは、モジュールの本体内で再宣言できないことに注意してください。 module <name> ([port_

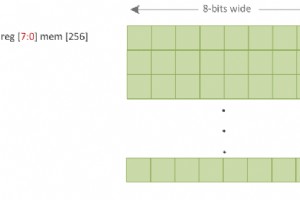

配列 ネットまたは変数の宣言は、スカラーまたはベクターのいずれかです。識別子名の後にアドレス範囲を指定することにより、任意の数の次元を作成でき、多次元配列と呼ばれます。 reg の Verilog では配列が許可されています 、 wire 、 integer そして real データ型。 reg y1 [11:0]; // y is an scalar reg array of depth=12, each 1-bit wide wire [0:7] y2 [3:0] // y is an 8-bit vector net with

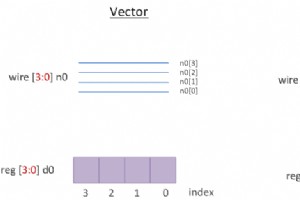

Verilog では、個々のビットとビットのグループを表す必要があります。たとえば、単一ビットの順次要素はフリップフロップです。ただし、16 ビットのシーケンシャル エレメントは、16 ビットを保持できるレジスタです。この目的のために、Verilog には scalar があります。 そしてベクトル ネットと変数。 スカラーとベクトル ネットまたは reg 範囲指定のない宣言は 1 ビット幅と見なされ、スカラーとなります .範囲が指定されている場合、net または reg ベクトルとして知られるマルチビットエンティティになります . wire o_nor;

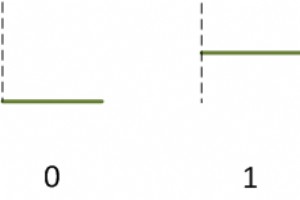

Verilog 言語のデータ型の主な目的は、フリップフロップのビットのようなデータ ストレージ要素と、論理ゲートとシーケンシャル構造の間を接続するワイヤのような伝送要素を表すことです。 変数が保持する値は? real を除いて、ほとんどすべてのデータ型は、以下に示す 4 つの異なる値のいずれかを持つことができます。 と event データ型。 0 論理ゼロまたは偽の状態を表します 1 論理 1、または真の状態を表します x 未知の論理値を表します (0 または 1 の可能性があります) z 高インピーダンス状態を表します 次の図は、これらの値がタイミング図とシミュレー

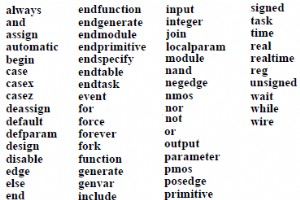

Verilog の語彙規則は、トークンのストリームを含むという意味で C に似ています。レキシカル トークンは 1 つ以上の文字で構成され、トークンはコメント、キーワード、数字、文字列、または空白になります。すべての行はセミコロン ; で終了する必要があります . Verilog では大文字と小文字が区別されます であるため、var_a と var_A は異なります。 コメント Verilog でコメントを記述する方法は 2 つあります。 一行 コメントは // で始まります Verilog コンパイラに、この時点から行末までのすべてをコメントとして扱うように指示します。 複数行 コメン

Verilog 言語の詳細を検討する前に、チップ設計における抽象化のさまざまなレイヤーを理解することをお勧めします。 最上層は、さまざまなサブブロックを定義し、機能に基づいてグループ化するシステム レベルのアーキテクチャです。たとえば、プロセッサ クラスタには、複数のコア、キャッシュ ブロック、およびキャッシュ コヒーレンス ロジックが含まれます。これらはすべてカプセル化され、入出力信号を持つ単一のブロックとして表されます。 次のレベルでは、各サブブロックがハードウェア記述言語で記述され、個々のブロックの機能が正確に記述されます。回路図やテクノロジ ライブラリなどの下位レベルの実装の詳

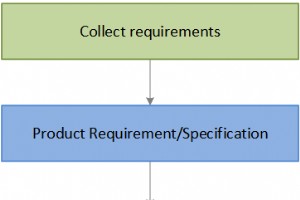

典型的な設計フローは、以下に示す構造に従い、複数のステップに分けることができます。これらのフェーズには、並行して行われるものもあれば、順番に行われるものもあります。今日の業界における典型的なプロジェクト設計サイクルがどのようになっているのかを見ていきます。 要件 通常、半導体企業の顧客は、自社のシステムまたは最終製品でチップを使用することを計画している他の企業です。したがって、顧客の要件も、チップの設計方法を決定する上で重要な役割を果たします。当然のことながら、最初のステップは、要件を収集し、最終製品の市場価値を見積もり、プロジェクトを実行するために必要なリソースの数を評価することです.

集積回路の黎明期、エンジニアは座って実際にトランジスタとその接続を紙に描いて、シリコン上で製造できるように設計する必要がありました。より大きく複雑な回路は、より多くの技術者、時間、その他のリソースを必要とし、すぐに集積回路を設計するためのより良い方法が必要になりました. VHDL エンジニアが目的のハードウェアの機能を記述し、自動化ツールがその動作を組み合わせゲートやシーケンシャル ロジックなどの実際のハードウェア要素に変換できるようにすることで、設計プロセスを強化するためにすぐに開発されました。 Verilog プロセスを簡素化し、ハードウェア記述言語を作成するために開発されました (HD

Verilog はハードウェア記述言語 (HDL) の一種です。 Verilog は、FPGA と ASIC を設計するために教育とビジネスで使用される 2 つの言語のうちの 1 つです。 FPGA と ASIC の仕組みに慣れていない場合は、FPGA と ASIC の概要についてこのページをお読みください。 Verilog と VHDL は、使用される最も一般的な 2 つの HDL です。 Java や C などの従来のソフトウェア言語と比較すると、Verilog の動作は大きく異なります。簡単な例を見てみましょう。 まず、記述する Verilog ファイルを作成します。 アンドゲート。復

Verilog