Verilog 数学関数は、定数式の代わりに使用でき、両方の integer をサポートします そして本物 数学。 整数数学関数 関数 $clog2 log2 の上限を返します 指定された引数の。これは通常、特定のサイズのメモリをアドレス指定するために必要な最小幅を計算するために使用されます。 たとえば、デザインに 7 つの並列加算器がある場合、7 つの加算器すべてを表すために必要な最小ビット数は $clog2 です。 3 を生成する 7 の module des #(parameter NUM_UNITS = 7) // Use of this syste

表示システム タスクは、主に情報メッセージとデバッグ メッセージを表示して、ログ ファイルからシミュレーションの流れを追跡するために使用され、デバッグを高速化するのにも役立ちます。値を出力できる表示タスクと形式には、さまざまなグループがあります。 タスクの表示/書き込み 構文 両方 $display と $write 引数リストに表示される順序で引数を表示します。 $display(<list_of_arguments>); $write(<list_of_arguments>); $write 改行文字 を追加しません $display の間

クロックは、異なるブロックが互いに同期できるようにするため、デジタル回路を構築するための基本です。 時計の性質 デジタル時計の重要な特性はその周波数です クロック周期を決定する 、そのデューティサイクル そしてクロックフェーズ 他の時計との関係で。 クロック周期 頻度は、特定の期間に何回のサイクルを見つけることができるかを示します。したがって、クロック周期は 1 サイクルを完了するのにかかる時間です。 クロック デューティ サイクル デューティ サイクルは、クロックがその期間と比較して高くなっている時間の長さによって定義されます。 クロック フェーズ クロックの 1 サイクルを

通常、Verilog デザインとテストベンチには、always で構成される多数のコード行があります。 または initial シミュレーション中の異なる時点でアクティブになるブロック、連続代入、およびその他の手続き型ステートメント。 Verilog モデルの信号値のすべての変化は、更新イベントと見なされます .そして always などのプロセス と assign これらの更新イベントに敏感なブロックは任意の順序で評価され、評価イベントと呼ばれます .これらのイベントはさまざまなタイミングで発生する可能性があるため、イベント キューにスケジュールすることで、より適切に管理され、正しい実行順

Verilog シミュレーションは、時間の定義方法に依存します。これは、シミュレーターが時間に関する 1 の意味を知る必要があるためです。 `timescale コンパイラ ディレクティブは、それに続くモジュールの時間単位と精度を指定します。 構文 `timescale <time_unit>/<time_precision> // Example `timescale 1ns/1ps `timescale 10us/100ns `timescale 10ns/1ns time_unit time_precision の間の遅延とシミュレーション時間

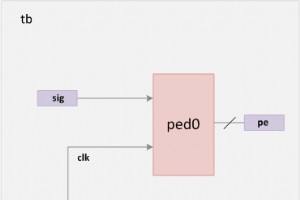

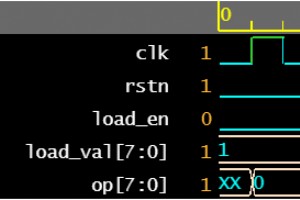

Verilog はハードウェア記述言語であり、設計者が RTL 設計を論理ゲートに変換できるようにシミュレートする必要はありません。では、シミュレートする必要があるのは何でしょうか? シミュレーションは、RTL コードが意図したとおりに動作するかどうかを確認するために、さまざまなタイミングでさまざまな入力スティミュラスをデザインに適用する手法です。基本的に、シミュレーションは、設計の堅牢性を検証するためのよく知られた手法です。また、製造されたチップが現実の世界でどのように使用され、さまざまな入力にどのように反応するかにも似ています。 たとえば、上記の設計は、出力 pe を見つけるため

nand のような標準 Verilog プリミティブ と not 複雑なロジックを表現するには、常に簡単または十分であるとは限りません。 UDP と呼ばれる新しいプリミティブ要素 または ユーザー定義のプリミティブ 組み合わせロジックまたは順序ロジックをモデル化するように定義できます。 すべての UDP には、0、1、または X のいずれかであり、Z ではない (サポートされていない) 1 つの出力があります。値 Z を持つ入力はすべて X として扱われます。 Verilog UDP シンボル Verilog ユーザー定義プリミティブは、module と同じレベルで記述可能 module

Verilog はトランジスタ レベル モデリングのサポートも提供しますが、回路が複雑なため、スイッチ レベル モデリングを使用するのではなく、より高いレベルの抽象化に移行する必要があるため、最近の設計者はめったに使用しません。 NMOS/PMOS module des (input d, ctrl, output outn, outp); nmos (outn, d, ctrl); pmos (outp, d, ctrl); endmodule module tb; reg d, ctrl; wire outn, outp;

デジタル要素はバイナリ エンティティであり、0 と 1 の 2 つの値のいずれかのみを保持できます。ただし、0 から 1 および 1 から 0 への移行には移行遅延があり、各ゲート要素も入力から出力に値を伝播します。 立ち上がり、立ち下がり、ターンオフの遅延 ゲートの出力がある値から 1 に変化するのにかかる時間は、上昇と呼ばれます 遅れ。ゲートの出力がある値から 0 に変化するのにかかる時間を フォール と呼びます 遅れ。ゲートの出力がある値から高インピーダンスに変化するのにかかる時間は、ターンオフと呼ばれます 遅れます。 これらの遅延は、実際の回路ではいつでも上昇または下降する可能

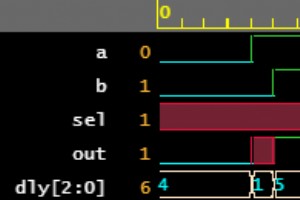

主な組み込みプリミティブのいくつかについては前の記事で説明しましたが、単純な and を使用した実用的な例をいくつか見るとよいでしょう。 、 nor と not ゲートを使用して Verilog コードを記述するには、要素の接続方法を知っている必要があることに注意してください。これは、要素の選択と接続が合成ツールに任されている動作記述とは大きく異なります。 例 #1:2x1 マルチプレクサ モジュールの出力は wire 型でなければなりません プリミティブの出力ポートに接続するため。 module mux_2x1 ( input a, b, sel, output o

ほとんどのデジタル設計は、RTL のような高レベルの抽象化で行われますが、 と のような組み合わせ要素を使用して、低レベルでより小さな決定論的回路を構築することが直感的になる場合があります。 そしてまたは .このレベルで行われるモデリングは、通常、ゲート レベル モデリングと呼ばれます。 ゲートが関係しているため ハードウェア回路図と Verilog コードの間に 1 対 1 の関係があります。 Verilog は、プリミティブと呼ばれるいくつかの基本的な論理ゲートをサポートしています 既に定義済みであるため、モジュールのようにインスタンス化できるためです。 And/Or/Xor Gates

ほとんどのプログラミング言語には、scope と呼ばれる特徴的な機能があります。 変数とメソッドに対するコードの特定のセクションの可視性を定義します。スコープは名前空間を定義します 同じ名前空間内の異なるオブジェクト名間の衝突を避けるため。 Verilog は、モジュール、関数、タスク、名前付きブロック、生成ブロックの新しいスコープを定義します。 module tb; reg signal; // Another variable cannot be declared with // an already existing name in the same scope

Verilog 遅延ステートメントでは、代入演算子の左側または右側に遅延を指定できます。 割り当て間の遅延 // Delay is specified on the left side #<delay> <LHS> = <RHS> 相互割り当て delay ステートメントには、代入演算子の LHS に遅延値があります。これは、ステートメント自体が後に実行されることを示します 遅延は期限切れになり、遅延制御の最も一般的に使用される形式です。 module tb; reg a, b, c, q; initial begin

Verilog には 2 種類のタイミング制御があります - delay そしてイベント 式。 遅延 制御は、シミュレーターがステートメントを検出してから実際に実行するまでの間に遅延を追加する方法にすぎません。 イベント式 ネットまたは変数の値の変更などのシミュレーション イベントが発生するまで、ステートメントを遅延させることができます (暗黙的なイベント ) または別の手順でトリガーされる明示的に名前が付けられたイベント。 シミュレーション時間は、次のいずれかの方法で進めることができます。 内部遅延を持つようにモデル化されたゲートとネットも、シミュレーション時間を進めます。 遅延制御

Verilog は、特定の方法でコードを処理するようコンパイラに本質的に指示するいくつかのコンパイラ ディレクティブをサポートしています。たとえば、コードの一部が特定の機能の実装を表している可能性があり、その機能が使用されていない場合は、設計にコードを含めないようにする何らかの方法が必要です。 これは条件付きで解決できます コンパイラ ディレクティブ内にコードをラップできます。これは、指定された名前付きフラグが設定されている場合に、コンパイルのためにコードを含めるか除外するかをコンパイラに指示します。 構文 条件付きコンパイルは Verilog `ifdef で実現できます そして `if

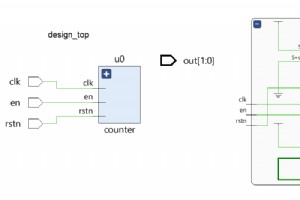

パラメーターは、モジュールを別の仕様で再利用できるようにする Verilog コンストラクトです。たとえば、4 ビットの加算器をパラメーター化してビット数の値を受け入れることができ、モジュールのインスタンス化中に新しいパラメーター値を渡すことができます。したがって、N ビットの加算器は、4 ビット、8 ビット、または 16 ビットの加算器になることができます。それらは、関数呼び出し中に渡される関数への引数のようなものです。 parameter MSB = 7; // MSB is a parameter with a constant value

function task は入力に対して何らかの処理を行い、単一の値を返すことを意図しています。 より一般的で、複数の結果値を計算し、output を使用してそれらを返すことができます そしてinout 型引数。タスクには、@ などのシミュレーションに時間がかかる要素を含めることができます 、ポージング その他。 構文 タスクは、ポート リストに引数のセットを持つ必要はありません。その場合は、空のままにすることができます。 // Style 1 task [name]; input [port_list]; inout [port_list]; output

多くの場合、特定のコードが反復的であり、RTL 内で複数回呼び出されていることがわかります。ほとんどの場合、シミュレーション時間は消費されず、さまざまなデータ値で実行する必要がある複雑な計算が含まれる場合があります。そのような場合、 function を宣言できます 繰り返しコードを関数内に配置し、結果を返せるようにします。 関数呼び出しを実行するだけなので、これにより RTL の行数が大幅に削減されます。 計算を実行する必要があるデータを渡します。実際、これは C の関数と非常によく似ています。 関数の目的は、式で使用される値を返すことです。関数定義は常にキーワード function で始

case ステートメントは、指定された式がリスト内の他の式のいずれかと一致するかどうかをチェックし、それに応じて分岐します。通常、マルチプレクサを実装するために使用されます。 if-else コンストラクトは、チェックする条件が多数あり、マルチプレクサではなくプライオリティ エンコーダに統合される場合には適していない可能性があります。 構文 Verilog ケース ステートメントは case で始まります キーワードであり、endcase で終わります キーワード。括弧内の式は 1 回だけ評価され、記述されている順序で代替のリストと比較され、代替が指定された式に一致するステートメントが実行さ

for ループはソフトウェアで最も広く使用されているループですが、主に複製に使用されます Verilog のハードウェア ロジック。 for の背後にある考え方 ループは、指定された条件が真である限り、ループ内で指定されたステートメントのセットを繰り返します。これは while に非常に似ています ループしますが、反復子が使用可能で、条件がこの反復子の値に依存するコンテキストでより多く使用されます。 構文 for (<initial_condition>; <condition>; <step_assignment>) begin // St

Verilog