VHDL でポート マップのインスタンス化を使用する方法

モジュールは、VHDL コードの自己完結型ユニットです。モジュールはエンティティを通じて外界と通信します . 港マップ モジュールのインスタンス化の一部であり、モジュールの入力と出力が接続されるローカル信号を宣言します。

このシリーズの以前のチュートリアルでは、すべてのコードをメインの VHDL ファイルに記述しましたが、通常はそうしません。シミュレーター用ではなく、FPGA または ASIC 設計で使用する目的でロジックを作成します。

シミュレータで実行するために作成された VHDL モジュールには、通常、入力信号も出力信号もありません。それは完全に自己完結型です。だからこそ、私たちのデザインの実体は空でした。 entity の間には何もありませんでした タグと end entity; タグ。

このブログ投稿は、基本的な VHDL チュートリアル シリーズの一部です。

入力信号または出力信号のないモジュールは、実際の設計では使用できません。その唯一の目的は、シミュレーターで VHDL コードを実行できるようにすることです。したがって、テストベンチと呼ばれます。 .入力信号と出力信号でモジュールをシミュレートするには、インスタンス化する必要があります テストベンチで。

多くの場合、モジュールとテストベンチはペアで提供され、別のファイルに保存されます。一般的な命名スキームは、テストベンチをモジュール名に「Tb」を追加して呼び出し、アーキテクチャを「sim」と命名することです。モジュールが「MyModule」と呼ばれる場合、テストベンチは「MyModuleTb」と呼ばれます。その結果、ファイル名は「MyModuleTb.vhd」および「MyModule.vhd」になります。

テストベンチ コードを使用して、モジュールがシミュレーション環境で正しく動作していることを確認できます。テスト対象のモジュールは、一般的に テスト対象のデバイス と呼ばれます。 (DUT).

モジュールは、他のモジュール内でインスタンス化することもできます。コードをモジュールに分割すると、複数回インスタンス化できます。同じ設計内でモジュールの複数のインスタンスを作成でき、多くの設計で再利用できます。

VHDL のポートを持つエンティティの構文は次のとおりです。entity <entity_name> is

port(

<entity_signal_name> : in|out|inout <signal_type>;

...

);

end entity;

このようなモジュールを別の VHDL ファイルでインスタンス化するための構文は次のとおりです。<label> : entity <library_name>.<entity_name>(<architecture_name>) port map(

<entity_signal_name> => <local_signal_name>,

...

);

<label> 任意の名前にすることができ、ModelSim の階層ウィンドウに表示されます。 <library_name> モジュールは、VHDL コードではなく、シミュレーターで設定されます。デフォルトでは、すべてのモジュールは work にコンパイルされます 図書館。 <entity_name> そして <architecture_name> インスタンスを作成しているモジュールと一致する必要があります。最後に、各エンティティ シグナルをローカル シグナル名にマッピングする必要があります。

VHDL でモジュールをインスタンス化する方法は他にもありますが、これは明示的なインスタンス化の基本的な構文です。

エクササイズ

このビデオ チュートリアルでは、VHDL でモジュールを作成してインスタンス化する方法を学習します。

MUX テストベンチの最終的なコード :

library ieee;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

entity T15_PortMapTb is

end entity;

architecture sim of T15_PortMapTb is

signal Sig1 : unsigned(7 downto 0) := x"AA";

signal Sig2 : unsigned(7 downto 0) := x"BB";

signal Sig3 : unsigned(7 downto 0) := x"CC";

signal Sig4 : unsigned(7 downto 0) := x"DD";

signal Sel : unsigned(1 downto 0) := (others => '0');

signal Output : unsigned(7 downto 0);

begin

-- An instance of T15_Mux with architecture rtl

i_Mux1 : entity work.T15_Mux(rtl) port map(

Sel => Sel,

Sig1 => Sig1,

Sig2 => Sig2,

Sig3 => Sig3,

Sig4 => Sig4,

Output => Output);

-- Testbench process

process is

begin

wait for 10 ns;

Sel <= Sel + 1;

wait for 10 ns;

Sel <= Sel + 1;

wait for 10 ns;

Sel <= Sel + 1;

wait for 10 ns;

Sel <= Sel + 1;

wait for 10 ns;

Sel <= "UU";

wait;

end process;

end architecture;

MUX モジュールの最終的なコード :

library ieee;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

entity T15_Mux is

port(

-- Inputs

Sig1 : in unsigned(7 downto 0);

Sig2 : in unsigned(7 downto 0);

Sig3 : in unsigned(7 downto 0);

Sig4 : in unsigned(7 downto 0);

Sel : in unsigned(1 downto 0);

-- Outputs

Output : out unsigned(7 downto 0));

end entity;

architecture rtl of T15_Mux is

begin

process(Sel, Sig1, Sig2, Sig3, Sig4) is

begin

case Sel is

when "00" =>

Output <= Sig1;

when "01" =>

Output <= Sig2;

when "10" =>

Output <= Sig3;

when "11" =>

Output <= Sig4;

when others => -- 'U', 'X', '-', etc.

Output <= (others => 'X');

end case;

end process;

end architecture;

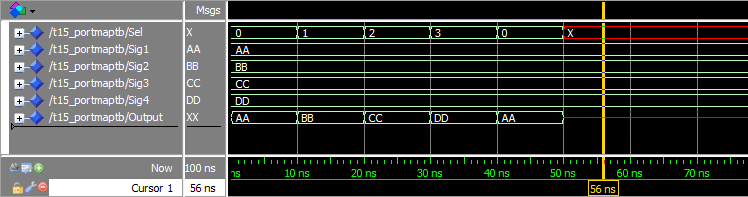

[実行] を押してタイムラインを拡大した後の ModelSim の波形ウィンドウ:

分析

波形からわかるように、マルチプレクサ (MUX) モジュールは期待どおりに動作します。波形は、モジュールを使用せずに作成した前のチュートリアルのものと同じです。

これで、デザイン モジュールとテストベンチが明確に分離されました。 MUX を含むモジュールは設計で使用するものであり、テストベンチの唯一の目的はシミュレータで実行できるようにすることです。テストベンチに wait を使用するプロセスがあります シミュレーションで人為的な時間遅延を作成するためのステートメント。設計モジュールには時間の概念がなく、外部刺激にのみ反応します。

テストベンチのアーキテクチャに sim という名前を付けました 、シミュレーション用。デザイン モジュールのアーキテクチャは rtl と名付けられました 、レジスタ転送レベルを表します。これらは単なる命名規則です。このような名前のファイルを見ると、それがテストベンチなのか設計モジュールなのかすぐにわかります。会社によって命名規則が異なる場合があります。

テイクアウト

- 入力信号と出力信号はモジュールのエンティティで指定されます

- 入出力信号のないモジュールは、テストベンチと呼ばれます 、シミュレータでのみ使用できます

- in/out シグナルを持つモジュールは、通常、シミュレーターで直接実行することはできません

次のチュートリアルに進む »

VHDL