VHDL で Case-When ステートメントを使用する方法

Case-When ステートメントにより、プログラムはシグナル、変数、または式の値に応じて、複数の異なるパスから 1 つを選択します。これは、複数の Elsif を持つ If-Then-Elsif-Else ステートメントのよりエレガントな代替手段です。

他のプログラミング言語にも同様の構造があり、switch などのキーワードを使用します。 、ケース 、または選択 .特に、Case-When ステートメントは、VHDL でマルチプレクサを実装するためによく使用されます。続きを読むか、ビデオを見て方法を確認してください!

このブログ投稿は、基本的な VHDL チュートリアル シリーズの一部です。

Case-When ステートメントの基本的な構文は次のとおりです。case <expression> is

when <choice> =>

code for this branch

when <choice> =>

code for this branch

...

end case;

<expression> 通常、変数または信号です。 Case ステートメントには、複数の when を含めることができます ただし、1 つの選択肢のみが選択されます。

<choice> "11" のような一意の値の場合があります :when "11" =>

または、5 to 10 のような範囲にすることもできます :when 5 to 10 =>

1|3|5 のような複数の値を含めることができます :when 1|3|5 =>

そして最も重要なのは、others 選択。他の選択肢が一致しなかった場合は常に選択されます:when others =>

others 選択は Else と同等です If-Then-Elsif-Else ステートメントの分岐。

エクササイズ

このビデオ チュートリアルでは、VHDL で Case-When ステートメントを使用してマルチプレクサを作成する方法を学習します。

このチュートリアルで作成した最終的なコード:

library ieee;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

entity T14_CaseWhenTb is

end entity;

architecture sim of T14_CaseWhenTb is

signal Sig1 : unsigned(7 downto 0) := x"AA";

signal Sig2 : unsigned(7 downto 0) := x"BB";

signal Sig3 : unsigned(7 downto 0) := x"CC";

signal Sig4 : unsigned(7 downto 0) := x"DD";

signal Sel : unsigned(1 downto 0) := (others => '0');

signal Output1 : unsigned(7 downto 0);

signal Output2 : unsigned(7 downto 0);

begin

-- Stimuli for the selector signal

process is

begin

wait for 10 ns;

Sel <= Sel + 1;

wait for 10 ns;

Sel <= Sel + 1;

wait for 10 ns;

Sel <= Sel + 1;

wait for 10 ns;

Sel <= Sel + 1;

wait for 10 ns;

Sel <= "UU";

wait;

end process;

-- MUX using if-then-else

process(Sel, Sig1, Sig2, Sig3, Sig4) is

begin

if Sel = "00" then

Output1 <= Sig1;

elsif Sel = "01" then

Output1 <= Sig2;

elsif Sel = "10" then

Output1 <= Sig3;

elsif Sel = "11" then

Output1 <= Sig4;

else -- 'U', 'X', '-' etc.

Output1 <= (others => 'X');

end if;

end process;

-- Equivalent MUX using a case statement

process(Sel, Sig1, Sig2, Sig3, Sig4) is

begin

case Sel is

when "00" =>

Output2 <= Sig1;

when "01" =>

Output2 <= Sig2;

when "10" =>

Output2 <= Sig3;

when "11" =>

Output2 <= Sig4;

when others => -- 'U', 'X', '-', etc.

Output2 <= (others => 'X');

end case;

end process;

end architecture;

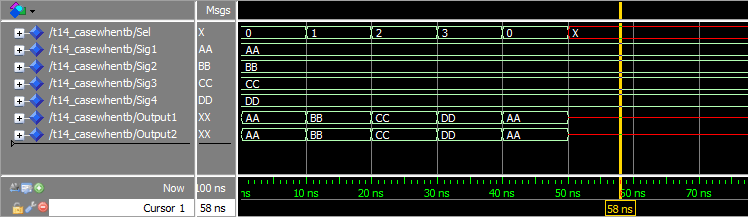

[実行] を押してタイムラインを拡大した後の ModelSim の波形ウィンドウ:

ModelSim で実行ボタンを押したときのシミュレータ コンソールへの出力:

VSIM 2> run # ** Warning: NUMERIC_STD."=": metavalue detected, returning FALSE # Time: 50 ns Iteration: 1 Instance: /t14_casewhentb # ** Warning: NUMERIC_STD."=": metavalue detected, returning FALSE # Time: 50 ns Iteration: 1 Instance: /t14_casewhentb # ** Warning: NUMERIC_STD."=": metavalue detected, returning FALSE # Time: 50 ns Iteration: 1 Instance: /t14_casewhentb # ** Warning: NUMERIC_STD."=": metavalue detected, returning FALSE # Time: 50 ns Iteration: 1 Instance: /t14_casewhentb

分析

まず、シグナル Sig1 の 1 つを転送する If-Then-Elsif-Else を使用するプロセスを作成しました。 、 Sig2 、 Sig3 、または Sig4 、セレクター信号 Sel の値に基づく .

次に、Case-When ステートメントを使用して、まったく同じことを行うプロセスを作成しました。波形から、2 つのプロセス Output1 からの出力信号であることがわかります。 と Output2 、まったく同じように動作します。

この例では、Sel signal には 4 つの有効な値しかありません。しかし、より多くの可能性があった場合、Case-When ステートメントがコードをより読みやすくするのに役立つことが容易にわかります。これは、ほとんどの VHDL 設計者がこのようなコンポーネントを作成する際に推奨する方法です。

マルチプレクサの理解 がこの演習のボーナス ポイントでした。マルチプレクサ、または略して MUX は、デジタル設計の中心的なコンポーネントです。複数の入力から 1 つを選択し、それを出力に転送する単純なスイッチです。

これは、MUX が選択された入力信号を転送する方法を示しています。

others を使用しました Sel のすべての値をキャッチする句 1でも0でもありませんでした。 std_logic チュートリアルで学んだように、これらの信号は '0' 以外の多くの値を持つことができます または '1' . 'X' を出力してこれらの値を処理することは、良い設計方法です。 .これは、この信号の値が不明であることを示しており、下流のロジックでも表示されます。

Sel 信号が赤くなりました、Output1 と Output2 "XX" にも変更 . when others => です

さらに、ModelSim のコンソール出力には、Sel が原因で警告が表示されます。 "UU" に設定されている信号 . 「** 警告:NUMERIC_STD.」=「:メタ値が検出され、FALSE を返す」というメッセージが 50 ns のシミュレーション時間に表示されます。これは信号が赤に変わる正確な時間です。

テイクアウト

- 複数の If-Then-Elsif ステートメントの代わりに Case-When を使用できます

when others =>デフォルトの選択を実装するために使用できます- マルチプレクサは Case-When ステートメントを使用して作成することをお勧めします

次のチュートリアルに進む »

VHDL