VHDL で同時実行ステートメントを作成する方法

VHDL の並行ステートメントは、アーキテクチャ内のシグナル割り当てですが、通常のプロセス構造の外側にあります。同時実行ステートメントは、同時割り当てまたは同時プロセスとも呼ばれます。

コンカレント ステートメントを作成すると、実際には、明確に定義された特定の特性を持つプロセスが作成されます。並行ステートメントは常に、シグナル割り当て演算子の右側にあるすべてのシグナルがセンシティビティ リストにあるセンシティビティ リストを使用するプロセスと同等です。

これらの簡略表記プロセスは、1 つの信号を割り当てる単純なロジックを作成する場合に役立ちます。センシティビティ リストなどを含む完全なプロセス構造を入力する代わりに、アーキテクチャでターゲット シグナルに直接割り当てることができます。

このブログ投稿は、基本的な VHDL チュートリアル シリーズの一部です。

正しく使用すると、コードの意図はかなり明確になります。反転させたいビットごとにプロセスを作成する必要はありません。

エクササイズ

このビデオでは、同時実行ステートメントを作成する方法を学びます:

このチュートリアルで作成した最終的なコード:

library ieee;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

entity T13_ConcurrentProcsTb is

end entity;

architecture sim of T13_ConcurrentProcsTb is

signal Uns : unsigned(5 downto 0) := (others => '0');

signal Mul1 : unsigned(7 downto 0);

signal Mul2 : unsigned(7 downto 0);

signal Mul3 : unsigned(7 downto 0);

begin

process is

begin

Uns <= Uns + 1;

wait for 10 ns;

end process;

-- Process multiplying Uns by 4

process is

begin

Mul1 <= Uns & "00";

wait on Uns;

end process;

-- Equivalent process using sensitivity list

process(Uns) is

begin

Mul2 <= Uns & "00";

end process;

-- Equivalent process using a concurrent statement

Mul3 <= Uns & "00";

end architecture;

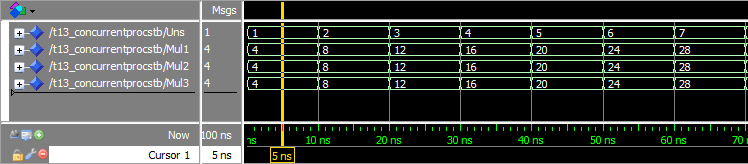

[実行] を押してタイムラインを拡大した後の ModelSim の波形ウィンドウ:

分析

波形から Mul1 であることがわかります 、 Mul2 、および Mul3 まったく同じように振る舞います。これは、concurrent ステートメントと作成した 2 つのプロセスが同等であるためです。

並行ステートメントは、プロセスと同じように機能します。 <= の右側のすべての信号 機密リストに自動的に追加されます。これは、<= の左側の信号が 評価されるシグナルの 1 つが変化するたびに更新されます。

VHDL で数値を乗算する方法は多数あります。この演習では、Uns を掛けました。 ビットシフトを使用して、信号を 4 倍にします。すべての信号は unsigned です つまり、数値で解釈されます。 2 進数の右側に 0 を追加することは、2 を掛けることと同じです。

これは、波形のカーソルで何が起こるかを示しています。

テイクアウト

- 並行ステートメントは、アーキテクチャ領域で直接シグナルを割り当てる

- 同時実行ステートメントは、センシティビティ リストで評価されたすべてのシグナルを含むプロセスと同等です

次のチュートリアルに進む »

VHDL