ソフトウェア開発者向けのCPUとFPGAの設計フロー:新しい具体的な現実

最近、Brian Baileyが円卓会議を開催し、 Supporting CPUs Plus FPGAs という2部構成の記事を作成しました。 。専門家は、FPGAとCPUに基づくシステム設計の進化する現実について話し合いました。このディスカッションでは、デザインフローの最近の開発と、新しいテクノロジを使用することで、ソフトウェア開発者がCPUとFPGAプラットフォームの市場投入までの時間を短縮するのにどのように役立つかについて説明します。

はじめに

人工知能(AI)への関心の高まり、接続されたオブジェクト(IoT)の出現、データセンターの加速傾向を見ると、3つの共通点は何ですか?

ソフトウェア開発者はこれらすべてのトレンドの中心であり、プログラミングと計算を加速することを目指しています。 FPGAとCPU間の通信遅延が少ないことや、今日のFPGAの消費電力が比較的低いことなど、最新のテクノロジの進歩により、FPGAベースおよびCPUベースのシステムが目的のパフォーマンスを実現するための正しい選択になっています。ただし、このコンバージェンスの中心にあるソフトウェア開発者は、FPGAテクノロジの根本的な複雑さによって妨げられています。

過去数年間で、高位合成(HLS)ツールは、今日のシステムの複雑さに対処し、市場投入までの時間を短縮することに関して大幅に改善されました。ただし、HLSツールは何よりもIPブロックに焦点を合わせています(つまり、IP中心です)。要件を満たすためにHLSツールでサポートできないシステムレベルの決定/最適化は幅広くあります。これらの要件には、ソフトウェアタスクとハードウェアアクセラレータの適切なバランスの発見、パイプラインと並列実行の比較、目的のデータ粒度の達成、通信メカニズムの評価などが含まれます。

これらの複雑なシステムを構築するために、ソフトウェア開発者はハードウェアとソフトウェアの両方の共同サポートを提供する設計フローを必要とします。このようなフローは、(ソフトウェア開発者フローのように)その使用とソフトウェア開発者による採用を保証するのに十分単純でなければなりません。フローは、必要なパフォーマンス目標を達成するために利用可能な最適化の選択に関する洞察に満ちたフィードバックも提供する必要があります。一部の企業は最近、ハードウェア設計フローの技術的詳細を抽象化することにより、ソフトウェア開発者のタスクを容易にする道を開いた。これらの企業は、 ESLモデルとそのアプリケーション:電子システムレベルの設計と実際の検証で説明されているシステムレベルの設計アプローチに触発されています。 。

システムレベルの設計フロー方法論を理解する

システムレベルの設計は、より高い抽象化レベルの懸念に焦点を合わせています。全体像に集中する必要がありますが、実際に開発される前に、さまざまなレベルの抽象化を使用して、システムのさまざまな部分を検証、検証、改良、および統合します。エンジニアリングコミュニティは使用する共通言語に同意していませんが、設計エンジニアの大多数はアルゴリズムレベルから始めます。設計者は、C / C ++ / SystemC、MATLAB、Simulink、およびLabVIEW環境で記述された実行モデルを作成することにより、非機能および機能システムの仕様を検証します。これらの高級言語は、システム全体の動作をモデル化するために使用されます。

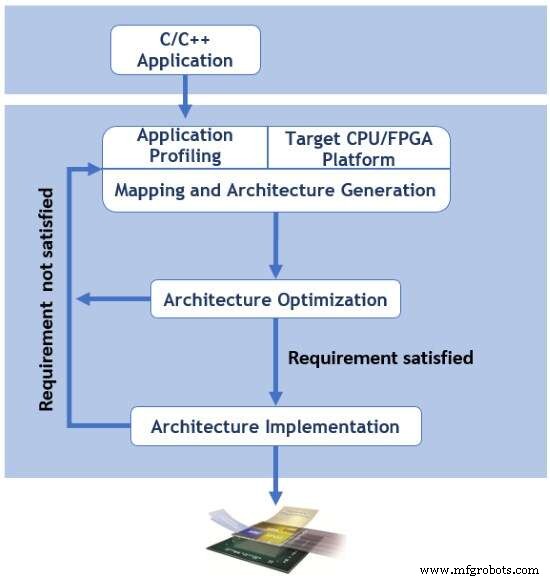

この説明では、C / C ++仕様に基づくシステムレベルの設計フローに焦点を当てました(図1)。最初のブロックは3つのステップに分かれています。これらのステップの最初のステップは、C / C ++コードの一部(関数、ループなど)がハードウェア(FPGA)に移動されたと見なされるアプリケーションプロファイリング(つまり、ハードウェアとソフトウェアのパーティショニング)を表します。次のステップは、CPU / FPGAプラットフォーム(ARM53 / FPGA、POWER8 / FPGAなど)の仕様とハードウェアプラットフォーム要素(システムクロック、プロセッサキャッシュ、相互接続など)の構成です。次のステップは、ハードウェアとソフトウェア(つまり、ハードおよび/またはソフトCPU)間で(プロファイルされたアプリケーションに基づいて)アプリケーションタスクをマッピングし、最後に実行可能アーキテクチャを生成することです。

図1.CPU / FPGAの一般的なシステムレベルの設計フロー

(出典:Space Codesign Systems、Inc。)

図1の2番目のブロックには、アーキテクチャの最適化(アーキテクチャの調査またはパフォーマンスの検証とも呼ばれます)が含まれます。これについては、図2で詳しく説明しています。

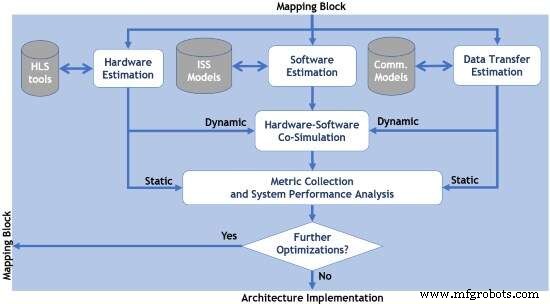

図2.アーキテクチャの最適化プロセス

(出典:Space Codesign Systems、Inc。)

アーキテクチャ最適化プロセスは、次の見積もりに対応しています。

- ハードウェアの見積もり ハードウェアパーティショニングのメトリックを評価します(つまり、FPGA上で移動されたC / C ++コード)。これは、リソース、パフォーマンス(ループ遅延など)、および電力見積もりによって分類できます。ハードウェアの見積もりは、HLS(高位合成)ツールによって実行されます。

- ソフトウェア見積もり CPU(つまり、ハードおよび/またはソフトCPU)で実行されているC / C ++パーティションコードのメトリックを評価します。このプロセスは、ハードウェア見積もりステップを補完するものです。パフォーマンスメトリックの例としては、プロセッサの負荷、タスクの切り替え、キャッシュミスなどがあります。

- データ転送の見積もり ハードウェアとソフトウェアが通信するためのインターフェイス(つまり、メモリマップトインターフェイスとストリーミングインターフェイス)のモデリングで構成されます。収集された指標の例としては、バスのパフォーマンス(レイテンシやスループットなど)、キュー、メモリ使用量などがあります。

これらの見積もりはデータベースに集約され、システムの要件が満たされているかどうかを評価するために、システムパフォーマンス分析が開発者に提示されます。要件を満たすアーキテクチャは、アーキテクチャの実装プロセスに進みます。それ以外の場合は、追加のシステムレベルの最適化の試行が処理されます。

図1の最後のブロックは、特定の物理プラットフォームで実行される最終的かつ完全なシステム生成のために、ザイリンクスVivadoやIntel Quartus Primeなどの実装ツールを使用してシステムアーキテクチャをビットストリーム(FPGA実装用)に変換するアーキテクチャ実装に関連しています。このステップでは、高品質のコードを生成する必要があり、ソフトウェア開発者にとって透過的である必要があります。

システムレベルの最適化

アーキテクチャを最適化するための自動化ツールの欠如は、FPGAベースのコンピューティングの主な弱点として長い間認識されてきました。このようなツールの開発は、複雑さと課題が伴うため困難でした。

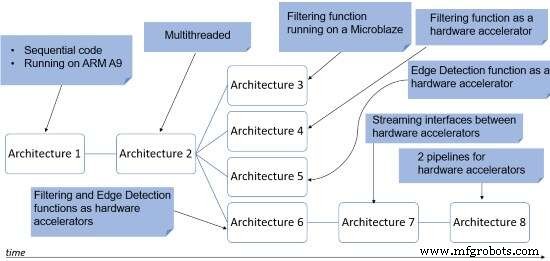

これらの課題を説明するために、図3は、Zynq-7000プラットフォームに実装される6つの関数(C / C ++コードの一部)で構成される画像処理アプリケーションのアーキテクチャ探索中の典型的なシステムレベルの最適化プロセスを示しています。ここでは、プラットフォームに実装できる8つの潜在的なアーキテクチャをリストします。市場投入までの時間では各アーキテクチャを実装できないため、実装するのに最適なアーキテクチャを迅速に決定する必要があります。この一連の最適化は、経験豊富なハードウェア設計者にとっても困難な場合があります。

図3.システムレベルの決定を青で示したアーキテクチャの調査

(出典:Space Codesign Systems、Inc。)

SDSoC / SDAccel(ザイリンクス)、Merlinコンパイラ(Falcon Computing Solutions)、SpaceStudio(Space Codesign Systems)などのFPGAソフトウェア開発ツールは、ソフトウェア開発者がシステムレベルの最適化を実現しながらFPGA / CPUシステムの設計を支援する商用ソリューションです。これらのツールは、図1および2で説明したのと同様のフローを採用しており、それによって、さまざまなアプローチを備えた新世代のシステムレベルのツールの存在を示しています。

SDSoCは、2段階のアプローチでシステムパフォーマンスを見積もります。最初に、SDSoCは、対象となる物理プラットフォームとその通信インターフェイスのハードウェア機能(HLSツールから)および内部特性評価(つまり、データ転送)の遅延を推定します。後で、この見積もりは、物理プラットフォームで実行されているアプリケーションのソフトウェアのみのバージョンと比較されます。

Merlinコンパイラはソースからソースへの変換を提案します。ソースからソースへの変換の目標は、ソフトウェア/アルゴリズム開発と既存のHLS設計フローとの間の設計抽象化のギャップを削減または排除することです。 Merlinコンパイラは、特定のFPGAデザインを推測するために4つのプラグマに依存しています。明示的なプラグマによってトリガーされる4つの主要な最適化に加えて、Merlinコンパイラには、パイプラインと並列化の結果を改善するためにプラグマとともに実行されるさまざまな暗黙的な最適化(つまり、コンパイラの変換パス)も含まれています。

>SpaceStudioは、アーキテクチャ候補ごとに実行可能な仮想プラットフォーム(VP)をシームレスに生成します(マッピング)。一般的なVPは、さまざまなモデルのバス、メモリコントローラ、およびその他のデータ周辺機器モデルに接続されたプロセッサコアシミュレータで構成されています。これは、アプリケーションに合わせて特別に調整された協調シミュレーション環境でのデータ転送とともに、対象となるプラットフォームをモデル化します。これは、実行可能VPにより、アプリケーションのより正確なパフォーマンス予測とアルゴリズム検証が可能になることを意味します。また、ハードウェア機能とソフトウェアタスクの両方の非侵入型パフォーマンスプロファイリングのための監視および分析機能を統合します。 VPは、ハードウェア推定機能をHLSツールに依存していますが、ハードウェアにマップされた関数の遅延(レイテンシーなど)には、シミュレーションプロセスの精度を高めるために自動的に注釈が付けられます。 VPは、ソフトウェア開発者が検査して、最適化タスクがどのように実装されているかを理解できます。このようなフィードバックは、ソフトウェア開発者が特定の適用された最適化のために意図された設計を達成するのに役立ちます。

商業エコシステムを表示する1つの方法

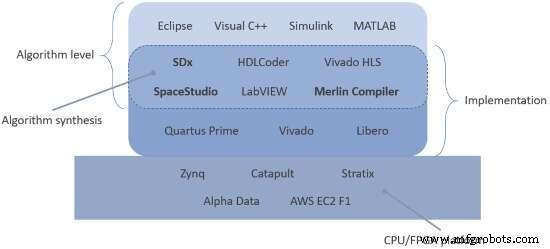

図4は、CPUとFPGAのプラットフォームベースの設計の世界で注目を集めている商用エコシステムのビューを示しています。最初の(上の)ボックスは、アルゴリズムレベルでの主要な設計エントリを示しています。 2番目のボックスには、アルゴリズム合成をサポートする環境が含まれています(つまり、アルゴリズムから実装まで)。太字でマークされたツールは、C / C ++デザインエントリをサポートし、システムレベルの最適化を実行します。 3番目のボックスは、アーキテクチャの実装を実現するために使用されるツール、主に低レベルの合成とビットストリーム生成を実行するFPGAベンダーのツールを表しています。図の下部には、CPU / FPGAプラットフォームの例が示されています。

図4.CPU / FPGAプラットフォームの商用エコシステム

(出典:Space Codesign Systems、Inc。)

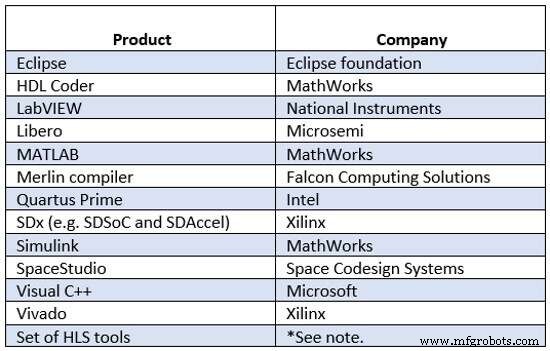

さらに、表1に、CPU / FPGAプラットフォームの設計で使用される主な商用ツールの一部を示します。

表1.商用自動化ツール(*注:このレビューではリストが提案されています)

結論

最終的な目標は、CPUとFPGAプラットフォームの開発を、ソフトウェア開発者コミュニティなどのより多くのユーザーに民主化することです。プログラミング言語の例えを見ると、プログラミング言語がPythonや最近ではSwiftなどの使いやすい言語に進化するまでにIT業界は50年以上かかりました。同様の進化プロセスがFPGAプログラミング業界で起こっています。 HLSツールの受け入れは、システム設計者によって承認されるまでに少し時間がかかりました。今日、ソフトウェア開発者向けのシステムレベルのソリューションの出現により、私たちは新しいフェーズに入っています。 SpaceStudio、SDSoC、Merlinコンパイラなどの商用ツールは、この受け入れプロセスの証です。それでも、CPUとFPGAプラットフォームを対象とするコンパイラ全体で完全に自動化され最適化されたプロセスを実現するには、まだ多くの作業が必要です。

Guy Bois、Ing。、PhD Space Codesign Systemsの創設者であり、モントリオール理工科大学のソフトウェアおよびコンピューター工学科の教授です。 Guyは、STMicroelectronics、Grass Valley、PMC Sierra、Design Workshops Technologies、Cadabra Systemsなどの業界リーダーと協力して多くのR&Dプロジェクトに参加してきました。ハードウェア/ソフトウェアコードサインの分野におけるGuyの研究の専門知識は、ソリューションの商品化とSpace Codesign SystemsInc。からのSpaceStudioの開始につながりました。

埋め込み

- 専門家のインタビュー:3D印刷用の自動トポロジー最適化ソフトウェアについて修正

- 専門家インタビュー:3D印刷用のシミュレーションソフトウェアに関するAltairのRavi Kunju

- Bosch SoftwareInnovatonsの新CEOであるStefanFerberへの5つの質問

- プロジェクトは、IoTセキュリティの信頼できる設計と検証のフローを調査します

- 新しいMLベースのツールは、自動化されたチップ設計フローの最適化を提供します

- エンベデッドビジョンMIPIカメラ用FPGAアクセラレータ

- ケイデンスとUMCは、28HPC +プロセスのアナログ/ミックスドシグナルフローの認証で協力しています

- 自動化:低コストロボット用の新しいハードウェアとソフトウェア

- クールなIoTのユースケース:ネットワーク化された自動車の新しいセキュリティメカニズム

- オムロンが移動ロボット向けの新ソフトウェアを発売

- 製造業の新しい現実への適応