スムーズな低電圧/過電圧ロックアウトのためのしきい値ヒステリシスの追加

抵抗膜式分割器は、高電圧を、低電圧回路がオーバードライブしたり損傷したりすることなく対応できるレベルまで減衰させます。電力経路制御回路では、抵抗性分周器は、電源の低電圧および過電圧のロックアウトしきい値を設定するのに役立ちます。このような供給電圧認定回路は、自動車システム、バッテリー駆動の携帯機器、データ処理および通信ボードに見られます。

低電圧ロックアウト(UVLO)は、下流の電子システムが異常に低い電源電圧で動作するのを防ぎ、システムの誤動作を引き起こす可能性があります。たとえば、デジタルシステムは、電源電圧が仕様を下回ると、動作が不安定になったり、フリーズしたりする可能性があります。電源が充電式バッテリーの場合、低電圧ロックアウトにより、ディープ放電によるバッテリーの損傷を防ぎます。過電圧ロックアウト(OVLO)は、システムを損傷を与えるほど高い電源電圧から保護します。低電圧と過電圧のしきい値はシステムの有効な動作範囲に依存するため、抵抗分割器を使用して、同じ制御回路でカスタムしきい値を設定します。供給ノイズまたは抵抗が存在する場合でも、スムーズでチャタリングのないロックアウト機能を得るには、しきい値ヒステリシスが必要です。簡単なUVLO / OVLO回路について説明した後、この記事では、デフォルト値が不十分な場合に必要となるしきい値ヒステリシスを追加するための簡単な方法をいくつか紹介します。

低電圧および過電圧ロックアウト回路

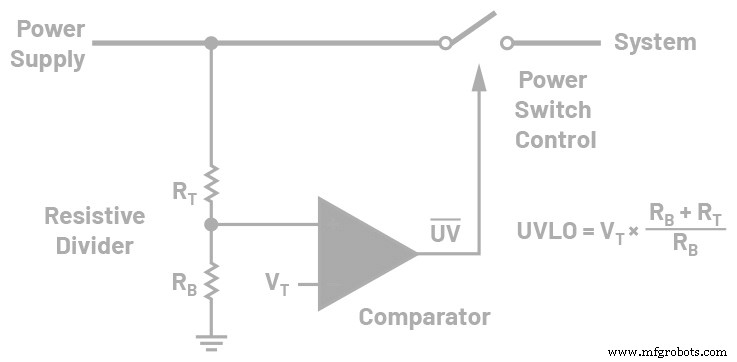

図1に、低電圧ロックアウト回路を示します(現時点ではヒステリシスなし)。正の基準電圧(V T )負の入力で。コンパレータは、電源入力とダウンストリーム電子システム間のパスを開閉する電源スイッチを制御します。コンパレータの正の入力は、入力から抵抗分圧器に接続します。電源がオンになり、0 Vから上昇し始めると、コンパレータ出力は最初はローになり、電源スイッチはオフのままになります。コンパレータ出力は、正の入力がV T に達するとトリップします。 。この時点で、下部の抵抗の電流はV T です。 / R B 。同じ電流がR T に流れます コンパレータに入力バイアス電流がない場合。したがって、コンパレータがトリップしたときの供給電圧はV T です。 + R T ×V T / R B =V T ×(R B + R T )/ R B 。これは、抵抗分割器によって設定された電源UVLOしきい値です。たとえば、V T 1VおよびR T =10×R B 11 VのUVLOしきい値を生成します。このしきい値を下回ると、コンパレータ出力が低くなり、電源スイッチが開きます。このUVLOしきい値を超えると、スイッチが閉じられ、電源が流れてシステムに電力が供給されます。 R B の比率を変更することで、しきい値を簡単に調整できます。 およびR T 。抵抗の絶対値は、分圧器に割り当てられたバイアス電流の量によって設定されます(これについては後で詳しく説明します)。 OVLOしきい値を設定するには、コンパレータの2つの入力を交換するだけです(たとえば、図2の下部のコンパレータを参照)。入力が高くなると、コンパレータの出力が強制的に低くなり、スイッチが開きます。

図1.抵抗分圧器、コンパレータ、および電源スイッチを使用した電源の低電圧ロックアウト。 (出典:Analog Devices)

この記事の焦点ではありませんが、スイッチはNチャネルまたはPチャネルのパワーMOSFETで実装できます。前の説明では、ゲート電圧が低い(たとえば、0 V)ときに開く(高抵抗)NチャネルMOSFETスイッチを想定しています。 NチャネルMOSFETを完全に閉じる(低抵抗)には、ゲート電圧が電源より少なくともMOSFETのしきい値電圧だけ高くなければならず、チャージポンプが必要です。 LTC4365、LTC4367、LTC4368などの保護コントローラは、コンパレータとチャージポンプを統合して、低静止電流を消費しながらNチャネルMOSFETを駆動します。 PチャネルMOSFETはチャージポンプを必要としませんが、ゲート電圧の極性が逆になります。つまり、低電圧は閉じ、高電圧はPチャネルMOSFETスイッチを開きます。

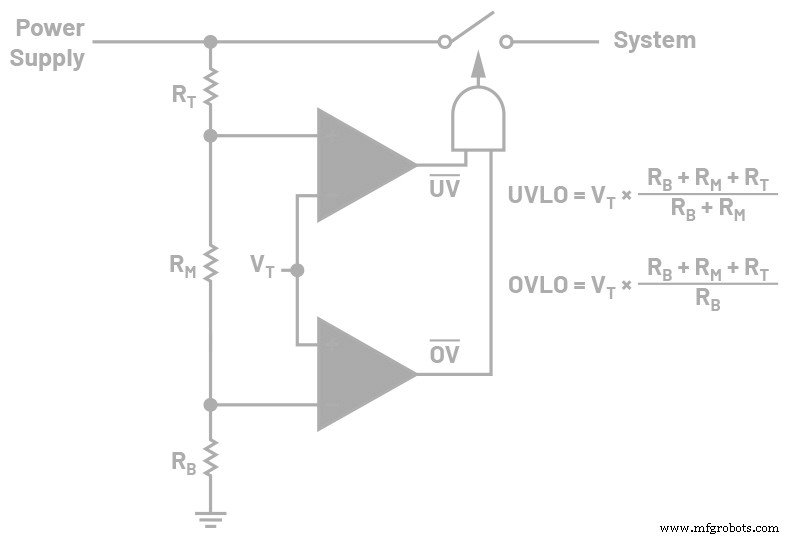

抵抗性分周器に戻る:3抵抗ストリングは、低電圧と過電圧の両方のロックアウトしきい値を設定し(図2)、2つの別々の2抵抗ストリングを使用する場合と比較して1つの分周器のバイアス電流を節約します。 UVLOしきい値はV T です ×(R B + R M + R T )/(R B + R M )OVLOしきい値がV T である間 ×(R B + R M + R T )/ R B 。 ANDゲートは、2つのコンパレータの出力を結合してから電源スイッチに送信します。したがって、入力電圧が低電圧と過電圧のしきい値の間にある場合、電源スイッチが閉じてシステムに電力が供給されます。それ以外の場合は、スイッチが開いており、システムから電源が切断されています。分周器の消費電流が問題にならない場合は、低電圧分周器と過電圧分周器を分離することで、各しきい値を互いに独立して調整する際の柔軟性が高まります。

図2.単一の抵抗分割器を使用した低電圧および過電圧のロックアウト。 (出典:Analog Devices)

ヒステリシスによる低電圧および過電圧のロックアウト

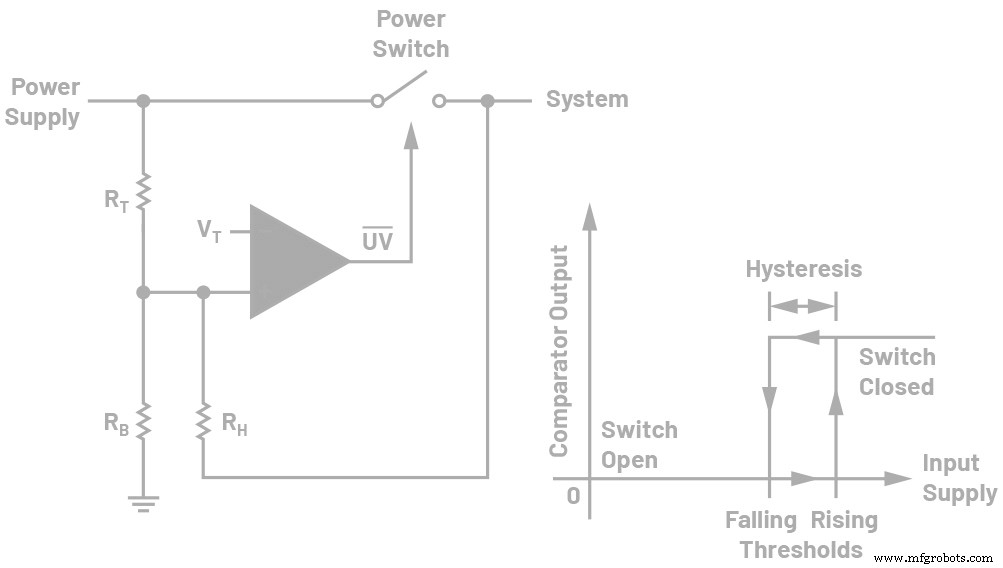

図1では、電源がゆっくりと上昇してノイズが発生する場合、または電源に負荷電流とともに電圧が低下する固有の抵抗がある場合(バッテリの場合など)、コンパレータの出力は入力としてハイとローを繰り返し切り替えます。 UVLOしきい値を超えています。これは、コンパレータの正の入力がV T を繰り返し上下するためです。 入力ノイズによるしきい値、または電源抵抗を流れる負荷電流によるドロップ。バッテリ駆動の回路の場合、これは終わりのない発振になる可能性があります。ヒステリシスのあるコンパレータを使用すると、このチャタリングがなくなり、スイッチの遷移がスムーズになります。図3に示すように、ヒステリシスコンパレータは上昇に対してさまざまなしきい値を示します(たとえば、V T + 100 mV)対立ち下がり入力(たとえば、V T – 100 mV)。コンパレータレベルのヒステリシスは、R B によってスケールアップされます。 およびR T 〜200 mV×(R B + R T )/ R B 供給レベルで。電源入力でのノイズまたはドロップがこのヒステリシスを下回る場合、チャタリングは解消されます。コンパレータによって提供されるヒステリシスがないか不十分な場合は、ヒステリシスを追加または増加する方法があります。これらの方法はすべて、分周器タップで正帰還を使用します。たとえば、コンパレータ入力が上昇すると、コンパレータがトリップすると高くジャンプします。簡単にするために、次の式はコンパレータに固有のヒステリシスがないことを前提としています。

図3.分圧器タップから電源スイッチ出力への抵抗を使用して、低電圧ロックアウトしきい値ヒステリシスを追加します。 (出典:Analog Devices)

ディバイダから出力への抵抗(図3):

抵抗を追加します(R H )分周器タップ(コンパレータの正の入力)から電源スイッチ出力まで。電源が0Vから上昇し始めると、コンパレータの正の入力はV T を下回ります。 コンパレータ出力はローで、電源スイッチはオフのままです。システム負荷のため、スイッチ出力が0Vであると想定します。したがって、R H R B と並列です 入力しきい値の計算用。上昇する入力低電圧しきい値はV T です。 ×((R B || R H )+ R T )/(R B || R H )、ここでR B || R H =R B ×R H /(R B + R H )。スイッチはこのしきい値を超えるとオンになり、電源をシステムに接続します。立ち下がり入力低電圧しきい値を計算するには、R H R T と並列です スイッチが閉じているため、立ち下がり入力低電圧しきい値は次のようになります。V T ×(R B +(R T || R H ))/ R B 、ここでR T || R H =R T ×R H /(R T + R H )。コンパレータ自体にヒステリシスがある場合は、V T に置き換えてください。 前の式のコンパレータしきい値の上昇または下降を使用します。 V T を使用した図1の例を思い出してください。 =1VおよびR T =10×R B 、コンパレータヒステリシスまたはR H がない場合、立ち上がりしきい値と立ち下がりしきい値の両方が11Vです。 。 R H を追加する =100×R B 、図3のように、11.1Vの上昇しきい値と10.09Vの下降しきい値が得られます。つまり、ヒステリシスは1.01 Vです。入力が上昇すると電源スイッチがオフになり、R H が発生するため、この方法はOVLOでは機能しません。 コンパレータ入力を高くするのではなく、低くする(スイッチを再びオンにする)。

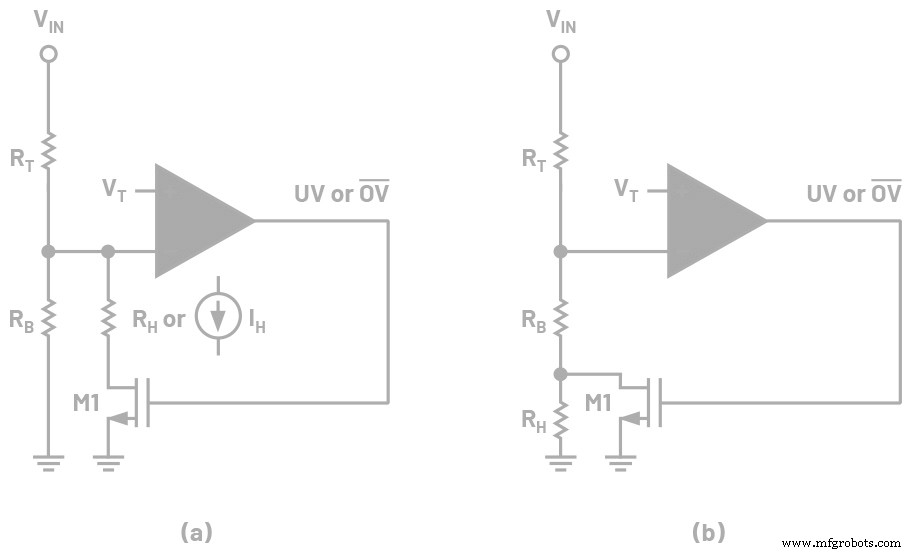

抵抗器の切り替え(図4):

ヒステリシスを追加する別の方法は、下部の抵抗の実効値を変更する抵抗を切り替えることです。スイッチド抵抗は、並列(図4a)または直列(図4b)にすることができます。図4aを検討してください:V IN の場合 がロー(たとえば0 V)である場合、コンパレータの出力(UVまたはOVノード)がハイであり、NチャネルMOSFET M1がオンになり、R H が接続されます。 R B と並行して 。 M1のオン抵抗は、R H と比較して無視できると仮定します。 またはR H に含まれています の値。入力しきい値の上昇は、図3と同じです。V T ×((R B || R H )+ R T )/(R B || R H )。一度V IN がこのしきい値を超えると、コンパレータ出力が低くなり、M1がオフになり、R H が切断されます。 仕切りから。したがって、立ち下がり入力しきい値は図1と同じです。V T ×(R B + R T )/ R B 。 V T で例を続けます =1 V、R T =10×R B 、およびR H =100×R B 、立ち上がり入力しきい値は11.1 V、立ち下がりしきい値は11Vです。つまり、R H 100mVのヒステリシスが得られます。この方法と次の方法は、コンパレータ出力が電源スイッチをどのようにオンにするかによって目的が異なるため、低電圧または過電圧のロックアウトに使用できます(図には示されていません)。

図4.(a)シャント抵抗または電流、および(b)直列抵抗を切り替えて、低電圧または過電圧のロックアウトしきい値ヒステリシスを追加します。 (出典:Analog Devices)

図4bの構成では、上昇する入力しきい値がV T として示されています。 ×(R B + R T )/ R B そして、V T としての立ち下がり入力しきい値 ×(R B + R H + R T )/(R B + R H )。 R H =R B 図4の/ 10は、上昇入力しきい値として11 V、下降しきい値として10.091 V、つまり909mVのヒステリシスを与えます。これは、図4bの構成に必要なR H がはるかに小さいことを示しています。 はるかに大きなヒステリシスを生成します。

電流の切り替え(図4a):

抵抗R H 図4aの電流源I H に置き換えることができます 。この方法は、LTC4417およびLTC4418の優先コントローラーで使用されます。 V IN の場合 が低い場合、コンパレータの高出力によりI H が有効になります。 。入力しきい値が上昇すると、コンパレータの負の入力はV T になります。 。したがって、R T の電流 I H です + V T / R B 、V T として上昇しきい値を生成します +(I H + V T / R B )×R T =V T ×(R B + R T )/ R B + I H ×R T 。一度V IN このしきい値を超えている場合、I H コンパレータの低出力によってオフになります。したがって、下限しきい値は図1と同じです。V T ×(R B + R T )/ R B 、および入力しきい値ヒステリシスはI H です。 ×R T 。

抵抗膜方式のバイアス電流

前の式は、コンパレータ入力の入力バイアス電流がゼロであると想定していますが、例では、絶対値ではなく抵抗比のみを考慮しています。コンパレータ入力には、両方の入力オフセット電圧(V OS )、参照の不正確さ(V OS でクラブ化される可能性があります )、および入力バイアスまたはリーク電流(I LK )。分圧器のバイアス電流V T の場合、漏れゼロの仮定が機能します。 / R B 図1のトリップポイントでは、入力リークよりもはるかに大きくなっています。たとえば、入力リーク電流の100倍の分圧器電流は、リークによる入力しきい値エラーを1%未満に保ちます。もう1つの方法は、リークによって引き起こされるしきい値エラーをオフセット電圧からのエラーと比較することです。コンパレータの非理想性により、図1の入力低電圧しきい値の式は次のように変更されます。(V T ±V OS )×(R B + R T )/ R B ±I LK ×R T (前のヒステリシス電流方程式と同様)、これは(V T ±V OS ±I LK ×R B ×R T /(R B + R T ))×(R B + R T )/ R B 。入力リークはコンパレータのしきい値電圧のエラーとして表示され、このエラーはオフセット電圧、つまりI LK に関連して最小化できます。 ×(R B || R T )

例として、LTC4367の低電圧および過電圧保護コントローラーのUVピンとOVピンの最大リークは±10nAですが、UV / OVピンコンパレータの500mVしきい値オフセット電圧は±7.5mV(500 mVの±1.5%)です。 ±3mV(500 mVの±0.6%、または7.5 mVオフセットの半分未満)のバジェットにより、しきい値エラーが発生し、R B が発生します。 || R T <3 mV / 10 nA =300kΩ。 0.5Vのコンパレータしきい値で11Vの入力低電圧しきい値を設定するには、R T が必要です。 =R B ×10.5V / 0.5 V =21×R B 。したがって、R B || R T =21×R B / 22 <300kΩ、R B を与える <315.7kΩ。 R B の最も近い1%の標準値 は309kΩで、R T が得られます。 6.49MΩになります。トリップポイントでの分圧器バイアス電流は0.5V /309kΩ=1.62 µAであり、これは10nAのリーク電流の162倍です。この種の分析は、コンパレータの入力リーク電流によるしきい値エラーを増加させずに分圧器電流を最小化する場合に重要です。

結論

抵抗分割器により、同じコンパレータベースの制御回路で電源の低電圧および過電圧のロックアウトしきい値を簡単に調整できます。電源のノイズまたは抵抗には、電源がしきい値を超えたときに電源スイッチのオンとオフのチャタリングを防ぐためのしきい値ヒステリシスが必要です。低電圧および過電圧ロックアウトヒステリシスを実装するためのいくつかの異なる方法が示されています。基本的な原理は、コンパレータがトリップしたときに分周器のタップで正のフィードバックを得るということです。保護コントローラICのヒステリシスを追加または増加する場合、一部の方法は、IC出力ピンでのコンパレータ出力または同様の信号の可用性に依存します。抵抗値を選択するときは、コンパレータの入力リークがしきい値エラーの主な原因にならないように注意する必要があります。この記事にあるものを含む、関連する方程式の包括的なセットが、ダウンロード可能なスプレッドシートに実装されています。

>

Pinkesh Sachdev は、アナログ・デバイセズの電力システム管理のシニアアプリケーションエンジニアです。彼は彼のB.Techを受け取りました。インドのムンバイにあるインド工科大学で学位を取得し、彼のM.S.スタンフォード大学で電気工学の学位を取得しています。彼の連絡先はpinkesh.sachdev@analog.comです。

Pinkesh Sachdev は、アナログ・デバイセズの電力システム管理のシニアアプリケーションエンジニアです。彼は彼のB.Techを受け取りました。インドのムンバイにあるインド工科大学で学位を取得し、彼のM.S.スタンフォード大学で電気工学の学位を取得しています。彼の連絡先はpinkesh.sachdev@analog.comです。 >

関連コンテンツ:

- 電源の順序付けと監視の管理、パート1

- 電源の順序付けと監視の管理、パート2

- 内蔵電源の選択

- 外部電源の選択

- 低電力設計の次の課題

Embeddedの詳細については、Embeddedの週刊メールニュースレターを購読してください。

埋め込み