AI / MLプロセッサにおける信頼性検証の重要性

さまざまなアプリケーションで人工知能と機械学習が採用されているため、障害が大きな影響を与える可能性があるため、AI / MLプロセッサの信頼性検証が重要です。 AI / MLテクノロジーの有効性と正当性について。

ここ数年、さまざまなアプリケーションに人工知能(AI)と機械学習(ML)を導入する企業の数が急速に拡大しています。実際、調査によると、2019年はAIとMLを採用する企業にとって記録的な年であり、これらの企業はこれら2つの機能をビジネス戦略と目標を達成するために最も必要であると考えています。この採用の増加は、主にアルゴリズムの改善、ハードウェア設計の進歩、および情報のデジタル化によって作成されるデータ量の増加によるものです。

ただし、AI / MLの成長をサポートおよび維持するには、企業はAI / MLテクノロジーで得られる結果が信頼できることを市場に証明し続ける必要があります。その信頼は、AI / ML機能の根底にある集積回路(IC)の設計と検証から始まります。

AIとMLの分類

AI処理は、クラウド/データセンターサイトで実行されるか、エンドユーザー側で実行されるかに応じて、データセンター/クラウドベースまたは組み込みに大まかに分類できます(専用のAIチップまたはAIコプロセッサエンジンを組み込むことにより)デバイス内部またはエッジでのシステムオンチップ(SOC))。このコンテキストでのエッジとは、データセンターやクラウドよりもデバイスに近いローカルサーバーまたはマシンを指します。

ターゲットアプリケーションに関して、エッジデバイスはトレーニング(ML)または推論に分類できます。歴史的に、トレーニング部分はクラウドサイトで実行され、推論部分はクラウドまたはエッジデバイスのいずれかで処理されていました。新しい高性能エッジコンピューティングソリューションの開発により、ますます多くのトレーニングアクティビティがエッジ側に転送されるにつれて、パラダイムシフトが見られます。

AI / MLチップ設計

エッジコンピューティングソリューションのAI / MLチップ、またはローカルデバイス内に組み込まれたAI / MLチップは、エンタープライズ、自動車、産業、ヘルスケア、モノのインターネット(IoT)などの特定の環境で使用するように設計されています。これらのアプリケーションの一部は、ミッションクリティカルです。障害が発生すると、現実の世界に悲惨な結果をもたらす可能性があります。たとえば、自動車内で使用される先進運転支援システム(ADAS)について考えてみます。 ADASプロセッサがセンサーからデータを読み取り、推論を行う際に所定の遅延を超える場合、衝突が発生する可能性があります。

AI / MLアプリケーションで使用されるICは、大規模な並列処理計算ユニット、高い消費電力、および厳しい電力バジェット内で最大のパフォーマンスを提供できる複雑な回路を特徴としています。一部の企業はAI関連のタスクに従来の中央処理装置(CPU)を採用していますが、一部の業界専門家は、最先端のAIアルゴリズムの分散性のため、CPUの使用はあまり効率的ではないと主張しています。これらのアルゴリズムは、グラフィックスプロセッシングユニット(GPU)によって提供されるような並列コンピューティングソリューションに適しています。再構成可能な性質により、フィールドプログラマブルゲートアレイ(FPGA)も、AIチップのアクセラレータとしての使用に関心を集めています。

AI / MLアプリケーションのASIC

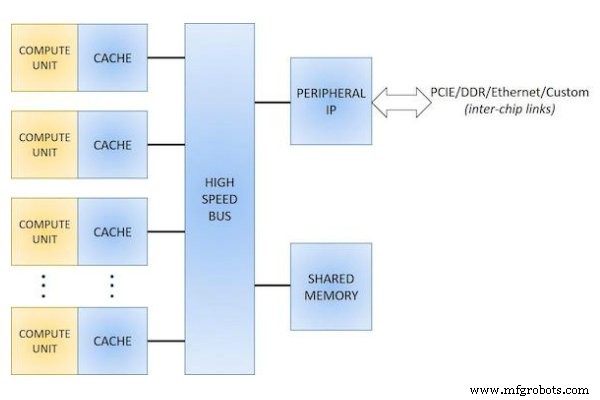

全体として、AIとMLのトリッキーな問題は、万能の設計ソリューションには適さないというコンセンサスが高まっています。この問題に対処するために、多くの企業が独自のアプリケーション固有のIC(ASIC)を開発し、ソフトウェアスタックと組み合わせて最適化して、特定のAI / MLアプリケーションに最高の価値を提供します(図1)。

図1。 ASICAIチップ設計のブロック図。

これらの企業は、これらのASICの使用によるさまざまなメリットを主張しています。たとえば、パフォーマンスの向上、サイクルあたりの操作数の増加、CPUやGPUと比較した場合のシンプルで決定論的な設計、面積の節約( CPU)、消費電力の削減、開発時間の短縮。

ヘテロジニアスコンピューティング

ヘテロジニアスコンピューティングの使用も増加しています。これは、さまざまな機能の最良のものを組み合わせるために、さまざまなコンピューティングコアタイプの組み合わせを使用するシステムです。たとえば、CPUとGPUを組み合わせて使用するシステムでは、並列タスクをGPUにオフロードすることでヘテロジニアスコンピューティングが有益になりますが、CPUはプロセス制御などのタスクを処理します。これは本質的にシリアルです。

異なるクラスのAIプロセッサに共通する側面の1つは、高性能と低遅延に最適化されており、多くの場合、1秒あたりのテラオペレーション(TOPS)パフォーマンスの乗数を提供することです。この非常に競争の激しい市場で優位に立つために、電力効率(ワットあたりのパフォーマンスで測定)は、生のスループットと同じくらい重要になっています。電力効率は、多くの場合、電力とクロックゲーティング、動的な電圧と周波数のスケーリング、マルチVt設計など、1つ以上の設計手法を組み合わせて使用することで実現されます。

これらのチップの回路障害は、テクノロジーの有効性とそれらが提供する結果の正当性に大きな影響を与える可能性があるため、これらの複雑なICの信頼性の高い設計と検証を保証することは重要です。

AI / MLICの信頼性検証

AI / MLチップでは、これらの設計のサイズと複雑さのために、信頼性の検証は大きな課題であり、トランジスタの数は数百万、場合によっては数十億にもなります。たとえば、NVIDIAのTESLA P100 GPUは153億の驚異的なトランジスタ数を誇っていますが、IntelのLoihiICには128のニューロモルフィックコアと3つのX-86コアがあり、20.7億のトランジスタがあります。また、使用環境ごとに信頼性要件が異なるため、設計者は該当する一連の要件を理解し、明確に定義された信頼性要件仕様に対して設計をテストして、それらが満たされていることを確認する必要があります。

設計の信頼性検証方法

従来、設計者は、主に設計チームの専門知識と経験に依存して、手動検査やシミュレーション技術など、設計の信頼性を確保するためにさまざまな方法を使用していました。ただし、手動検査は、時間がかかり、人為的エラーが発生しやすく、十分なカバレッジを提供することが事実上不可能であるため、これらの大規模で複雑なAI / MLチップの実行可能なアプローチではありません。従来のSPICEのようなシミュレーションアプローチは、大規模な設計ではスケーラビリティが不足しているため、これらのICでも実用的ではありません。

容量とランタイムの問題を克服するために、多くの設計チームは手動で設計を分割し、シミュレーションまたは従来のツールを使用してさまざまな知的財産(IP)ブロックを個別に検証します。ただし、設計内の異なるIPブロック間(たとえば、異なるコンピューティングコアとバスまたはリンクまたは高帯域幅メモリ間)には多くの相互作用があり、インターフェイス間の相互作用は、手動のパーティショニングプロセス中に見落とされる傾向があります。従来のIC検証ツールは、これらの複雑な設計を検証するために非常に長いランタイムに苦労し、大規模な設計を検証するのに数日かかることが多く、市場投入までの時間を遅らせる可能性があります。

これらの各プロセスの欠陥は、複数のCPUとデバイスの計算能力を同時に活用できる包括的な自動電子設計自動化(EDA)ソリューションの必要性を浮き彫りにします。自動化された認定済みの信頼性検証により、製品設計および検証チームは信頼性の検証と修正に迅速に集中でき、全体的なターンアラウンドタイム(TAT)を数日から数時間に短縮できます。

CalibrePERC信頼性プラットフォーム

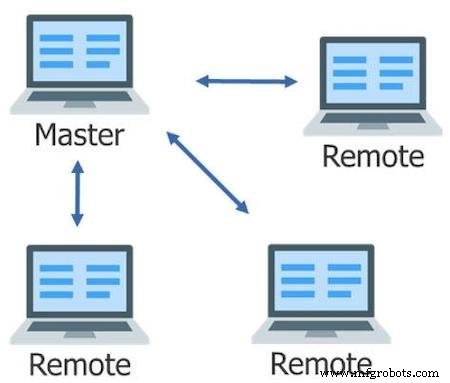

過去数年にわたって、これらのプロセスの問題を解決する新しいクラスのIC信頼性検証ツールが登場しました。 Calibre™PERC™信頼性プラットフォームなどのツールは、豊富な機能セットを活用して、ファウンドリ認定の高速な信頼性検証を提供します。たとえば、Calibre PERC信頼性プラットフォームは、Calibreプラットフォームのマルチスレッド(MT)およびマルチスレッドフレキシブル(MTflex)スケーリングを利用して、タスクを複数のCPUやリモートマシンに分散し、検証プロセスを高速かつ効率的に実行します。 AI / ML ICのような大きくて複雑なチップ上(図2)。

図2。 マルチスレッドで柔軟なスケーリングにより、タスクが複数のリモートに分散され、全体的な実行が高速化されます。

Calibre PERC信頼性プラットフォームは、これらの基本的で不可欠なメカニズムに加えて、設計からのネットリストとレイアウト情報の両方を組み合わせて、潜在的な信頼性の問題を迅速かつ正確に評価する革新的な処理を提供します。設計者が効率的かつ自信を持ってパフォーマンスや運用上の障害に対する設計の影響を受けにくくすることで、高度な信頼性検証へのこのアプローチは、信頼できるAI / MLテクノロジーの継続的な成長と採用をサポートするのに役立ちます。

トランジスタレベルの信頼性

ML / AI設計の大部分は、アナログIPにクリーンでノイズのない電源を提供する、チップの特定の領域に電力をゲートまたはシャットオフする機能を有効にする、スケーリングなど、さまざまな目的で複数の電力ドメインを使用します選択したIPに対して個別に電圧を上げたり下げたりするか、複数の電圧レギュレータを使用して高電流の需要に対応します。たとえば、IntelのSkylakeプロセッサには9つのプライマリパワードメインが含まれています。

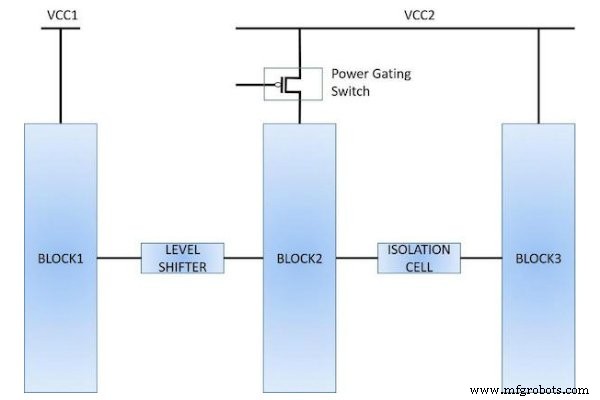

マルチパワードメイン設計を実装するには、電圧レギュレータ、ヘッダーおよびフッタースイッチ、レベルシフター、アイソレーションセル、状態保持セルなどの特別な回路要素を使用する必要があります。これらの要素は、信頼性の検証に固有の一連の課題を提示します。たとえば、設計者は、各ドメインインターフェイスで適切なレベルシフターまたは分離セルが使用されていること、およびそれらが正しく接続されていることを確認する必要があります(図3)。

図3。 低電力設計内で特殊な要素(レベルシフター、アイソレーションセル、パワーゲーティングスイッチなど)を使用するには、特殊な検証技術が必要です。

また、高電圧供給用の厚い酸化物デバイスなど、さまざまな電力ドメインで適切なタイプのデバイスを使用していることを確認する必要があります。これらの条件を確認するには、非常に具体的な知識とプロセスが必要です。

ユニファイドパワーフォーマットテクニック

ユニファイドパワーフォーマット(UPF)は広く使用されている手法であり、設計者はデザインフロー全体でパワーインテントの一貫した記述を使用できます。ただし、従来のUPFベースの検証フローは、ロジックまたはゲートレベルでIPを検証するために使用されますが、最終的なトランジスタレベルの実装、特にウェル接続とバルク接続を検証する機能がありません。

Calibre PERC信頼性プラットフォームは、設計用のUPFファイルを読み取り、UPF情報を活用して、欠落または誤って接続されたレベルシフター、電気的過大応力(EOS)状態、フローティングウェルなどを特定するなど、トランジスタレベルでさまざまな分析を実行できます。 。 Calibre PERC信頼性プラットフォームをUPFデータと組み合わせて使用することにより、設計者はデバイスの相互作用をプログラムで評価して、再現性のある決定論的な信頼性検証を提供できます。

AI / MLチップの生涯信頼性

運用上の安全性は、ほとんどのAI / MLチップにとって重要な側面であり、設計されたライフタイムを通じて、グリッチや障害なしに動作することが期待されています。バイアス温度不安定性(BTI)やEOSなどの一部の電気的信頼性の問題は、即時の障害としては現れない場合がありますが、製造前に修正しないと、時間の経過とともに急速な劣化と経年劣化を引き起こす可能性があります。信頼性検証は、ポイントツーポイント抵抗、正および負のBTI、電流密度、エレクトロマイグレーション(EM)などのさまざまな問題をチェックすることにより、長期間にわたって堅牢な動作を保証するのに役立ちます。これらはすべて、パフォーマンスの低下や壊滅的な障害を引き起こす可能性があります。

高電圧ドメインデバイスが、高電圧を処理する定格のない薄い酸化物デバイスを駆動している場合を考えてみます。設計中に、設計者は高低レベルのシフターを挿入できません。この状態は、最初は必ずしも機能に影響を与えるとは限りませんが、時間の経過とともに薄い酸化物デバイスにストレスを与え、最終的には障害を引き起こします。実際の故障時間は、電圧値、電源がオンとオフの時間、およびプロセスパラメータによって異なります。

EM(電流による導体内の原子の移動)は、AI / MLICで使用される相互接続の長期的な堅牢性に影響を与えるもう1つの大きな問題です。この移行により、ワイヤ上にボイドとヒロックが形成されます。ボイドは抵抗の大幅な増加を引き起こしますが、ヒロックは短絡を引き起こす可能性があり、どちらも回路障害につながります。 EM効果は、金属線の長さと幅、相互接続材料、動作温度、一方向電流と双方向電流など、多くの要因に依存します。

ファウンドリは、製品の予想される使用条件に基づいて、ワイヤが処理できる最大電流のEM制限を設計会社に提供します。たとえば、携帯電話の内部で使用されるICのEM制限は、産業環境で使用されるICの場合よりもかなり低くなります。一部の企業には、ファウンドリと積極的に連携して適切な仕様を定義し、テスト構造を作成し、EM耐性の製品認定を実行する専任チームがあります。明らかに、複数の環境で使用できる製品に対してこれらの制限を定義することは難しいため、設計者は通常、最悪の場合の動作条件に対してこれらのチップを設計します。いずれの場合も、ファウンドリが定義したEM制限に対して設計をテストし、設計がEMの影響に耐えられることを検証することが重要です。

プレシリコン検証フェーズでさまざまな信頼性の問題を見つけて修正しなかった場合、複数のテープアウトスピン、製品の市場投入の遅れ、顧客の信頼の喪失、重大な市場の否定的な反応など、さまざまな影響が生じる可能性があります。製品のリコール、さらには身体的損傷や人命の損失などの壊滅的な結果。テープアウトの前に信頼性違反を特定して修正することで、コストがかかることが判明する可能性のある回路の誤動作や障害の可能性を最小限に抑えます。

AI / MLの信頼性の分析と管理は非常に重要です

AI / ML機能の最近の成功と拡張は、主に半導体技術の進歩に基づいています。これらの新しい設計が開発されると、ハードウェア設計コミュニティは、ターゲット環境、動作条件、信頼性基準など、設計の信頼性の側面を分析および管理する必要性を認識する必要があります。対応するように設計された強力なEDA信頼性検証ツールこれらの大きくて複雑なチップの特定の信頼性の問題と要件は、設計会社が設計された寿命を通じて製品が意図したとおりに機能することを保証するのに役立ちます。これは、より広範な市場でAI / MLアプリケーションを使用することで達成された結果に自信を持ち、その継続的な使用と拡張をサポートすることを意味します。

業界記事は、業界パートナーが編集コンテンツに適さない方法でAll About Circuitsの読者と有用なニュース、メッセージ、テクノロジーを共有できるようにするコンテンツの形式です。すべての業界記事は、読者に有用なニュース、技術的専門知識、またはストーリーを提供することを目的とした厳格な編集ガイドラインの対象となります。業界記事で表明されている見解や意見はパートナーのものであり、必ずしもAll AboutCircuitsやそのライターのものではありません。

モノのインターネットテクノロジー