純粋なCMOSロジックプロセスによる自己抑制抵抗スイッチング負荷を備えたRRAM統合4TSRAM

要約

このホワイトペーパーでは、低電力/高速SRAMアプリケーション向けの自己抑制データストレージメカニズムを備えた、新しいフルロジック互換の4T2R不揮発性スタティックランダムアクセスメモリ(nv-SRAM)について報告します。コンパクトなセル領域と完全なロジック互換性を備えたこの新しいnv-SRAMには、4TSRAM内に埋め込まれた2つのSTI-ReRAMが組み込まれています。データは、高速アクセス速度を維持するために、クロスカップル揮発性構造を介して読み取り/書き込みできます。データは、抵抗変化型メモリ(RRAM)負荷への独自の自己抑制操作により、新しいSRAMセルに不揮発性に保存でき、データ保持中の静的電力をゼロにします。

背景

近年、ポータブルデバイスやIOTアプリケーションのコンピューティングシステムのニーズを満たすために、さまざまな低電力の静的ランダムアクセスメモリが開発されています[1,2,3,4,5,6]。 CMOSテクノロジがナノメートル領域にスケールダウンすると、オフ状態のリーク電流が大幅に増加し、揮発性メモリモジュールの静的消費電力が悪化します[7、8]。ナノスケールトランジスタのリーク電流によって発生する静的消費電力は、低電力SRAMの進歩にとって重要な課題の1つになっています。 [9、10、11]。長年にわたり、SRAMの消費電力を最小限に抑えるために、さまざまなセル構造または動作技術[12、13、14、15、16]が提案されてきました。新たに提案されたセルの一部には、抵抗変化型メモリ(RRAM)や磁気抵抗変化型メモリ(MRAM)などの不揮発性ストレージ要素が組み込まれており[17、18、19、20]、低動作を維持しながらゼロ保持力を実現します。揮発性データの処理における電力と高速アクセス速度。ただし、ロジックベースのSRAMアレイに不揮発性ストレージ要素を追加するには、通常、標準のロジックプラットフォームに追加のレイヤーやプロセスが必要です[21、22、23]。これにより、開発のプロセスが必然的に複雑になります。さらに、これらのバックエンドベースのRRAMおよびMRAMには、SRAMセルへのビアと金属のマルチスタックで構成される大規模な接続構造が必要です。これらのブリッジ構造は、SRAMデータストレージノードへの寄生容量を増加させ、これらの不揮発性SRAMセルのアクセス速度に影響を与えます[24、25]。以前の研究[26]では、4TSRAMの浮体式貯蔵ノードの隣にSTI側壁RRAMを配置した新しいゼロスタティックパワー4Tnv-SRAMが最初に提案されました。このレターでは、不揮発性データストレージ、ゼロ保持力、高速アクセス速度を備えたこの4T2R nv-SRAMをさらに分析し、組み込みNVMアプリケーション向けに最適化します。

メソッド

STI-ReRAMセル構造

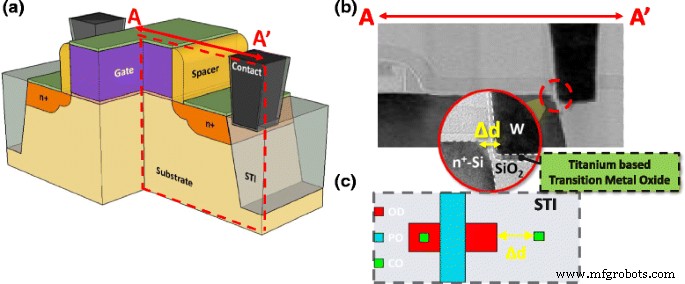

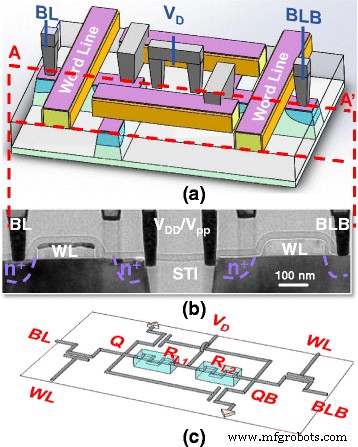

図1aの3DSTI-RRAM構造では、抵抗変化型ストレージノードは2つの電極間の遷移金属酸化物(TMO)、それぞれ左側と右側のN +領域とタングステンプラグで構成されています。図1bのTEM写真と図1cのレイアウトに示されているように、接点をSTI領域にN +領域まで適切な距離で配置することにより、残りのSiO 2 タングステンプラグの下のバリア層はTMOフィルムになり、抵抗スイッチング品質を備えています。

a n +ジャンクションのすぐ隣にSTI-ReRAMを備えた1T1Rセルの3D図。 b 特別に配置された接点と選択トランジスタのn +領域の間に形成された、遷移金属酸化物で構成される抵抗性ストレージノードの対応するTEM画像。 c レイアウト

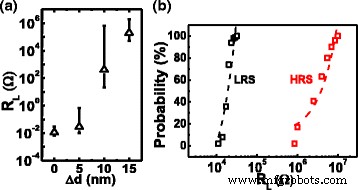

TMOの厚さは、接点とN +拡散領域の間の適切な間隔Δdを選択することで制御できます。図2aの測定に基づくと、初期抵抗レベルと引き込み距離Δdの間には正の相関関係があり、それぞれSTI領域と接触領域を定義するマスクによって決定されます。次の研究では、形成電圧が低く、R L が好ましいため、Δdが10nmに等しいRRAMを選択します。 図2bに要約されているように、低抵抗状態(LRS)と高抵抗状態(HRS)の両方での分布。セット/フォーミング操作中の適切なワードライン(WL)電圧制御により、セット電流を選択トランジスタによってローカルにクランプできるため、耐久性能が向上します。

a △dが異なるSTI-RRAMサンプルの測定された初期抵抗。 b 高抵抗状態と低抵抗状態の両方でのSTI-RRAMのリセット/セット後の負荷抵抗の累積確率

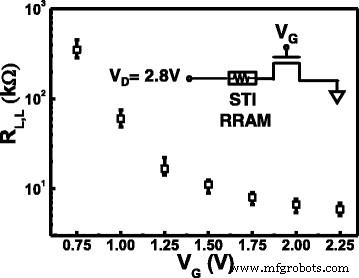

図3のデータは、LRSの読み取り電流レベルがゲート電圧V G によって適切に制御できることをさらに示しています。 。 V D での成形中 =2.8V、デバイスがLRSに設定された後、選択トランジスタはSTI-RRAMを通過する最大電流を制限します。その後のLRS状態の抵抗レベルは、さまざまなTaOベースのRRAMデバイスで見られる局所的にクランプされた電流に反比例します[27、28]。

負荷抵抗レベル間の相関関係、R L、L 、およびセット中に印加されるゲート電圧。データは、異なるR L、L を示唆しています 選択ゲート電圧の異なるレベルを設定することで取得できます

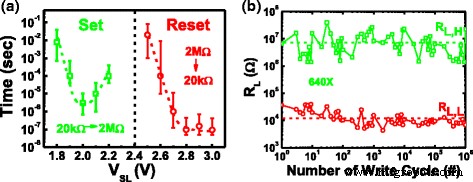

STI-RRAMの抵抗スイッチング特性を確認するために、図4aに示すように、セットまでの時間とリセットまでの時間がテストされます。 V SL の場合、セットとリセットの操作を最適化できます。 =2および2.8V、それぞれ。 RRAM耐久性テストは図4bに要約されています。インクリメンタルステップパルスプログラミングアルゴリズムを使用することにより、その読み取りウィンドウは100万サイクル後も安定した状態を維持できます。

a 要約されたセットまでの時間とリセットまでの時間とV PP 。 b インクリメンタルステップパルスプログラミングアルゴリズムを使用したSTI-RRAMの100万サイクルの耐久性テスト結果

不揮発性SRAMの概念

図5の3D図は、新しく提案された4T2R nv-SRAMセル構造と、AAのカットラインに沿った対応する断面TEM画像を示しています。 2つのSTI-RRAMは、不揮発性ストレージノードと負荷抵抗の両方として機能します。これらはQおよびQB N +拡散領域と、適切な間隔でSTIエッジに密接に着地した接点の間に挟まれています。 TEM写真は、分離領域の左側と右側の両方に整形式のSTI-RRAMを示しており、トランジスタの同じレベルにこれらの近接して配置された不揮発性ストレージノードを備えたかなりコンパクトなセルになります。

a 提案された4T2Rnv-SRAMセル構造と b の3D図 対応する断面TEM画像。 c SRAMセルの回路図は、ロードデバイスとして2つのRRAM抵抗を使用して示されています

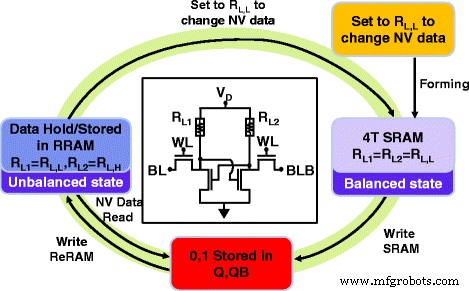

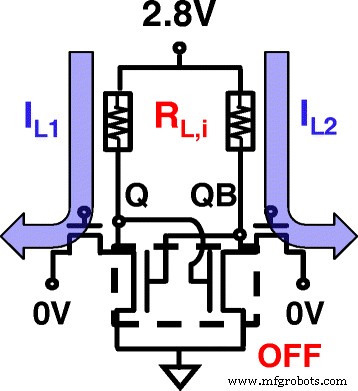

提案されている4Tnv-SRAMは、揮発性モードと不揮発性モードで動作させることができます。その4つの異なる状態とその操作スキームを図6に示します。

nv-SRAMセルの回路図と揮発性SRAM操作と不揮発性SRAM操作を切り替えるための対応するフローチャート

初期状態では、STI-RRAMは通常10 8 の抵抗レベルを持ちます。 Ω、TMOフィルムは無傷です。ブランケット形成操作により、nv-SRAMセルはV D でブロックごとに同時に初期化できます。 =2.8V。両方のR L1 およびR L2 (それぞれ左と右の負荷抵抗)はR L、L に初期化されます 。最終的なR L、L 成形作業中に異なるWL電圧を与えることにより、20〜370kΩのレベルを制御できます。その後、セルは平衡状態に達します。これは、2つの負荷抵抗が同じ状態にあることを意味します。この状態で、このセルは通常の4T2R SRAMとして機能し、クロスカップリングされたラッチにデータを保存することにより、従来の方法で揮発性データを処理できます。

データを非揮発性で保存するために、このセルに継承される自己抑制メカニズムによって、補完的なラッチデータをRRAMに保存できます。データがRRAMペアに正常に保存されると、永続的なデータ保持のために電源をオフにすることができます。保存された状態にアクセスするには、V DD を再適用するだけです。 アレイに。不揮発性データはQノードとQBノードに自動的に復元され、従来のSRAM読み取りモードでアクセスできます。最後に、不揮発性データを更新するために、SRAMアレイにブランケットセット操作が適用され、アレイがバランス状態に戻ります。

結果と考察

電気分析

異なるステージ間の遷移の動作条件を表1にまとめています。

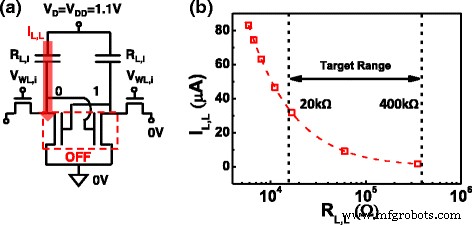

<図>異なるR L、L レベルは、ブロックまたはアレイの初期化中に異なるWL電圧を設定することで取得できます。安定性と動作電圧を考慮して、R L、L この研究では、20〜400kΩの範囲のレベルが最初に調査の対象になります。図3に示すように、0.75〜1.25 Vの対応するWL電圧では、結果として生じる負荷抵抗はかなり直線的に減少します。予想どおり、R L、L は低くなります。 レベルはより高いスタンバイ電流につながります。図7を参照してください。ただし、R L、L 2つの抵抗状態の間でデータウィンドウを大きく拡大できるように、十分に低く保つ必要があります。ターゲットのR L、L をさらに最適化するには、静的、動的、および不揮発性の両方のデータウィンドウを考慮する必要があります。 、初期化条件で設定されます。

a ホールド状態の4T2RSRAMセル。 b 予想通り、負荷抵抗レベル、I L、L より高いR L、L を選択することにより、ホールド中を効果的に下げることができます。

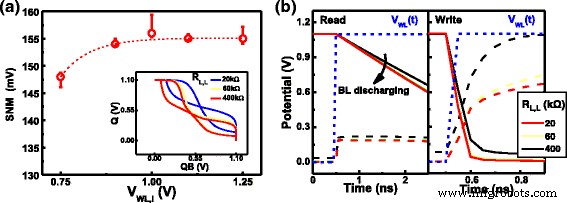

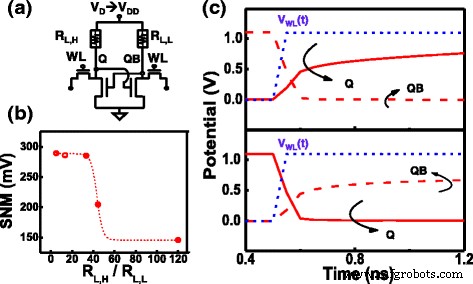

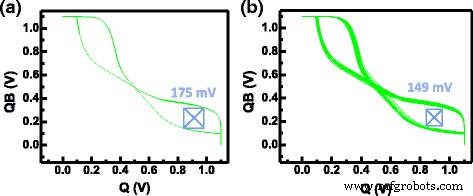

バランス状態のnv-SRAMの静的および動的特性は、さまざまな条件で初期化されたセルを考慮して、最初に調査されます。図8では、異なるWL電圧によって初期化されたセルの複数のバタフライ曲線によって得られた静的ノイズマージン(SNM)。データは、R L、L 負荷抵抗がターゲット範囲内にある場合、レベルは平衡セルの読み取りマージンに最小限の影響しか与えません。異なる初期化条件下での平衡状態にある複数のセルのSNM分布を図8aに要約します。全体的なSNMはセル間でかなり安定していますが、V DD より低いWL電圧で妥当な読み取りマージンを確立できます。 、これは低電力アプリケーションに有益です。平衡状態でのこのセルの動的な読み取りおよび書き込み特性を調査するために、書き込み「1」および「0」の過渡応答を図8bに要約します。 R L、L が高いことがわかります Q、QBノードへのプルアップ速度を低下させます。これにより、読み取り操作と書き込み操作の両方で過渡時間がわずかに長くなる可能性があります。ただし、応答速度はまだ期待範囲内です。上記のデータは、バランス状態で、この4T2Rnv-SRAMが従来のSRAMとして揮発性データを処理できることを示しています。

a 初期化中に異なるWL電圧を持つ提案されたSRAMセルの読み取り静的ノイズマージン(SNM)。合理的なSNMは、かなり広い範囲のR L、L 内に維持できます。 20〜400kΩの。 b 平衡負荷状態でのセルの動的な読み取りおよび書き込み特性は、ナノ秒以内の良好な応答時間を示しています。より高いR L、L 書き込み操作中のプルアップ速度がわずかに低下します

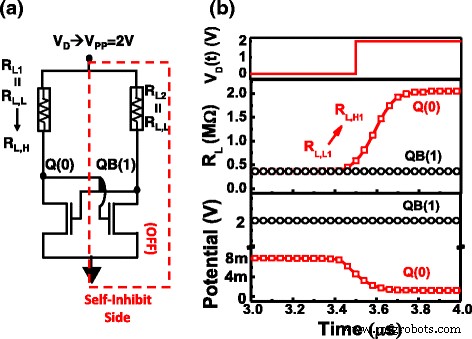

STI-RRAMペアにデータを保存するために、このセルは、負荷抵抗ペアのRRAMの1つのみを自己選択的にリセットできるようにします。これにより、より高いV pp セルブロックへの供給ノードへの電圧を均一に。ラッチデータがQおよびQBノードに保存されると、図9aに示すように、RRAMとのクロスカップル構造の自己抑制メカニズムによって不揮発性書き込みが実現されます。 Qノードで低電圧のRRAMの片側のみがR L、H にリセットされます 。プルダウントランジスタが低いV Q によってオフになるため、もう一方のブランチの電流はほぼゼロになります。 。

a 2つのRRAMの片側をリセットすることによる不揮発性データ書き込み中の自己抑制メカニズムの図。 b R L の動的変化 およびQ、QBの可能性は、RRAMへのラッチデータの自己抑制書き込みを検証します

データはV PP としてRRAMペアに保存されます パルスが供給ノードに適用されます。不揮発性データを書き込む場合、R L の動的スイッチング Q、QB電位の過渡応答を図9bにまとめています。測定データは、片側でSTI-RRAMを選択的にリセットするには、V pp で300nsのパルスを使用することを提案しました。 =2Vで十分です。図10aのように、セルが不均衡な状態にある場合でも揮発性の動作に影響を与えないようにするために、R L、H が異なるセルのSNM分布 / R L、L 比率は図10bに要約されています。状態間の低抵抗比はホールドSNMを低下させないことがわかります。負荷が不均衡なセルを確保するために、そのようなセルへのデータの動的書き込みが特徴付けられます。データは、図10cに示すように、2 M / 400 kの初期不平衡抵抗比を克服して、両方の状態を正常に書き込むことができることを示しています。

a 不平衡負荷時のクロスカップル構造。 b 初期化中の異なるWL電圧での静的ノイズマージン。 c 2つの異なるデータ状態の動的書き込み。不均衡R L、L =400kΩも書くことができます

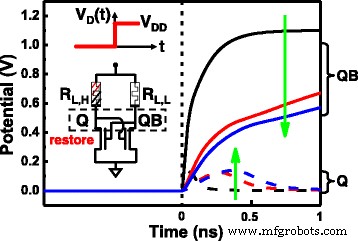

以前にRRAMに保存された揮発性データをロードするために、V DD を適用するだけです。 図11に示すように、電源ノードへのRRAMの不平衡負荷は、QおよびQBのラッチノードに自己復元されます。

不平衡RRAMロード状態からQおよびQBに保存された不揮発性データの復元。 QノードとQBノードの両方の可能性は、ナノ秒以内に電源がオンになった後に復元できます

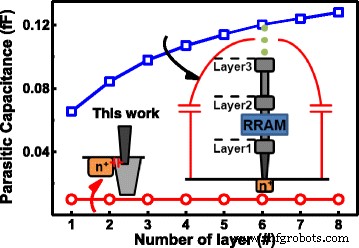

寄生効果と比較

完全なロジック互換のSTI-RRAMをこの新しいSRAMセルに組み込むことにより、このセルは、マスキング層やプロセスステップを追加することなく、ほとんどの標準的なロジックプロセスで簡単に実装できます。この機能は、多くのICシステムで必要とされるさまざまな不揮発性メモリIPモジュールでのアプリケーションと柔軟性を大幅に向上させることができます。さらに、提案された4T2R nv-SRAMは、バックエンドオブライン(BEOL)不揮発性コンポーネントを必要とする他の以前に報告されたnv-SRAM [29、30、31]と比較してはるかに小さい寄生容量を特徴としています。 Siの表面からこれらのBEOLRRAMまたはMRAMにQおよびQBノードを接続するには、金属の複数のスタックとビア層が必要です。これらの大きなブリッジ構造は、重大な寄生RC効果をもたらします。 SRAMセル内の内部ノードに導入される大きな寄生容量は、デバイスの応答時間に重大な影響を与える可能性があります。

これらに対する寄生効果を比較するために、レイアウト後のシミュレーションの推定に基づいてnv-SRAMが調査されます。すべてのセルが同じ標準CMOSテクノロジによって実装されていると仮定すると、大きなブリッジ構造を必要とするセルの金属層の数が増えると、ラッチノードの寄生容量が増加します。 STI-RRAMを使用する新しいnv-SRAMの場合、ラッチされたノードの全体的な容量の増加はほとんどありません。さらに、特定の回路に適合した金属層の数とは無関係です。 SRAM速度の寄生容量の影響をさらに調査するために、[29,30,31]で提案されたSRAMセルのシミュレートされた動的応答とこの作業を図12で比較します。

参考文献[30]のnv-SRAMセルのラッチノードの寄生容量と、40 nm CMOSテクノロジに基づくこの作業から、金属層の数が増えるにつれて寄生容量の大幅な増加が見られます

。この組み込みnv-SRAMの寄生容量がはるかに小さいと、SRAMセルでの動的読み取り動作中の応答時間が短縮される可能性があります。これにより、接続ブリッジの大きな内部容量がロジックベースのSRAMアレイの応答時間に与える影響を防ぎます。

表2は、バックエンドRRAMまたはMRAMに組み込まれた以前に報告された不揮発性SRAMの主な機能とこの動作を比較しています。状態スイッチング電圧が高いにもかかわらず、STI-RRAMベースのnv-SRAMは、SRAMセル内の内部ラッチノードの寄生容量がはるかに小さく、完全なロジック互換性があります。

<図>変動による静的ノイズマージンの低下

プロセスの変動、RRAM抵抗レベルの変動、およびトランジスタのしきい値電圧V T の影響を受けるセルで、安定したSNMを確保するため 、は次の調査で考慮されます:V T の不一致 スケーリングされたテクノロジーによってSRAMのSNMシフトを引き起こすことが知られています[32、33]。さらに、異なるセットコンプライアンス電流を引き起こす可能性もあり、その結果、2つのR L、L の抵抗レベルの変動が大きくなる可能性があります。 。図13に示すように、異なるV T STI-RRAMセルで異なる初期化コンプライアンス電流が発生し、R L、L でさらに不一致が発生します 。 V T の影響を分析するには SNMのバリエーションでは、V T を想定しています。 以前の報告[34]に基づく平均と変動を持つガウス確率変数である。モンテカルロシミュレーションにより、R L、L の変動を受けるバタフライカーブの分布 図14aに要約されています。 R L、L の両方のバリエーションが とVTを考慮すると、図14bに示すように、SNMウィンドウの大幅な狭まりが観察されます。 nv-SRAMの変動性の増加は、将来の研究で対処する必要があります。

V T バリエーションにより、初期化コンプライアンスが異なりますI L、1 およびI L、2

a によって引き起こされるSNM劣化を比較するモンテカルロシミュレーションによるバタフライカーブ R L、L の変動 初期化後および b 両方のR L、L のバリエーション およびV T

結論

CMOSロジックプロセスと完全にロジック互換性のある新しい4T2RSTI-RRAMベースの不揮発性SRAMは、追加のマスクやステップなしで、40nmテクノロジノードの純粋なCMOSロジックプロセスで正常に実証されました。このnv-SRAMセルは、不揮発性データの自己抑制、自己復元メカニズム、ラッチノードの小さな寄生容量、およびデータ保持中のゼロ静的電力を特長としています。これらの優れた特性により、STI-RRAMベースのnv-SRAMは、将来の低電力/高速ロジック不揮発性メモリアプリケーション向けの有望なソリューションになります。

ナノマテリアル

- デジタル集積回路の紹介

- 集積回路

- フィードバック付きデジタルロジック

- ダイオードスイッチング回路

- 抵抗性および反応性AC回路の電力

- 実用的な力率補正

- 自己整流スイッチ特性を備えたTaO / HfOxおよびTaO / AlO xRRAMの保持モデル

- 原子層堆積によって製造されたPtおよびTiNコーティング基板上のHfO2 / TiO2 / HfO2三層構造RRAMデバイスのバイポーラ抵抗スイッチング特性

- コンプライアンスフリーのZrO2 / ZrO2 − x / ZrO2抵抗変化型メモリと制御可能な界面マルチステートスイッチング動作

- 窒化処理を施したHfO2ベースのRRAMの伝導メカニズムと耐久性の向上

- 分子動力学法によるアブレシブナノメートル切削プロセスに及ぼす衝撃方向の影響の研究