デュアルゲートトンネリングトランジスタに基づくコンデンサレスDRAMのためのスペーサーエンジニアリングの最適化

要約

デュアルゲートトンネリングFET(DGTFET)に基づくDRAMには、コンデンサのない構造と高い保持時間という利点があります。この論文では、DGTFET DRAMのスペーサーエンジニアリングの最適化をSilvaco-Atlasツールによって体系的に調査し、読み取り「0」電流の削減や保持時間の延長など、パフォーマンスをさらに向上させます。シミュレーション結果は、ソース側とドレイン側のスペーサーがそれぞれlow-kとhigh-kの誘電体を適用する必要があることを示しています。これにより、読み取り「1」電流が増加し、読み取り「0」電流が減少します。この最適化されたスペーサーエンジニアリングを適用することで、DGTFET DRAMは最適なパフォーマンスを実現します。つまり、読み取り値が非常に低い「0」電流(10 -14 )です。 A /μm)と長い保持時間(10秒)により、静的消費電力と動的リフレッシュレートが低下します。また、読み取り値が低い「0」電流は、その電流比(10 7 )も向上させます。 )「1」を読んでから「0」を読んでください。さらに、スケーラビリティに関する分析により、固有の欠点が明らかになり、DGTFETDRAMのさらなる調査の方向性が示されます。

背景

デバイスの形状が縮小するにつれ、1トランジスタ(1T)–1コンデンサ(1C)ダイナミックランダムアクセスメモリ(DRAM)は、コンデンサのサイズを小さくすることが難しいため、スケールダウンが困難になりました[1,2,3] 。メモリ業界は、新しい材料や新しいデバイス構造など、高密度メモリをパッケージ化するためのいくつかの効果的な方法を提案しています[4、5]。コンデンサレス構造の1TDRAMは、90年代初頭に最初に報告され[6、7]、ますます注目を集めています。 1T DRAMでは、状態1(キャリアストレージ)は、衝突電離[8]、バイポーラ接合トランジスタ[9]、バンド間トンネリング(BTBT)[10]、およびゲートトンネリング[11]の4つの方法で実現されます。

BTBTに基づくトンネル電界効果トランジスタ(TFET)は、スイッチング比が高く、オフ状態電流が非常に低いため、MOSFETの代替電位と見なされてきました[12、13、14]。 TFETの利点(オフ状態電流が低く、温度依存性が弱い)は、DRAMにとって非常に有益です。特に、オフ状態の電流が少ないと、読み取り値の「0」電流と静的消費電力を減らすことができます。現在、TFETDRAMの調査に取り組んでいるグループがいくつかあります[15、16、17、18、19、20]。 TFET DRAMは、読み取り値の「0」電流が低く、保持時間(RT)が長いと報告されています。これらのTFETDRAMの中で、デュアルゲートTFET(DGTFET)DRAMが最も顕著です[19、20]。 DGTFET DRAMでは、書き込み操作と読み取り操作の両方がBTBTに基づいています。調査によると、DGTFETDRAMの読み取り電流は1nA /μmに達する可能性があり、これは従来の1T1CDRAMよりもはるかに少ない値です。また、2秒のRTは、コンピューティングシステムで動的リフレッシュ時間に通常設定されている64ミリ秒の目標値よりもはるかに優れています[21]。 DGTFET DRAMのRTは、温度を85°Cに上げても300ミリ秒を超えています。これは、過酷な条件での実用性を示しています。さらに、DGTFET DRAMでは、より大きなサイズのコンデンサを排除することで、高密度パッケージングでも競争力を発揮します。これらの利点は、DGTFETDRAMを研究する必要があることを完全に示しています。これらの研究により、DGTFETは従来の1T1C DRAMよりも優れたパフォーマンスを発揮することが実証されていますが、DGTFETのデバイス構成が最適化されていないため、結果(RTおよび読み取り値「0」電流)は最適ではありません。

この論文では、DGTFETのスペーサーエンジニアリングは、DGTFETが最適な性能を得られるように最適化されています。 TFETでは、スペーサー誘電体がBTBTに強い影響を及ぼします[22、23]。 DGTFETでは、ソース側とドレイン側のスペーサーがトンネリングジャンクションに閉じているため、DGTFETDRAMのパフォーマンスに大きく影響します。この論文では、各スペーサーのスペーサー誘電体(low-kまたはhigh-k誘電体)がDGTFET DRAMに与える影響を体系的に分析し、最適化されたスペーサーエンジニアリングを提案します。スペーサーエンジニアリングの最適化により、読み取り値の「0」電流は10 -14 に低下します。 A /μm、RTは10秒に達する可能性があります。最後に、最適化されたスペーサーエンジニアリングを使用したDGTFETDRAMのスケーラビリティについてもこの作業で説明します。

デバイスの構造とシミュレーション方法

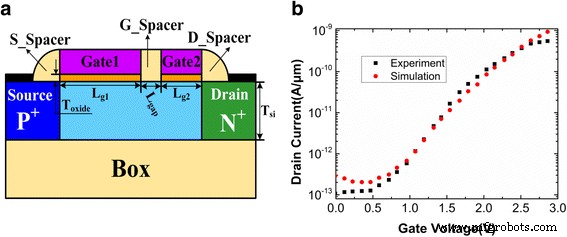

P-I-N構成のDGTFETを図1aに示します。ソース領域とドレイン領域はP + です。 ドーピング(10 20 / cm 3 )およびN + ドーピング(10 20 / cm 3 )、 それぞれ。固有のチャネル領域は2つの部分に分けられます:N + を持つGate1領域 P + のポリシリコンとGate2領域 ポリシリコン。 Gate1とGate2の間には短いギャップがあります。 P + ポリシリコンGate2は、電荷蓄積のための物理的ウェルを作成および維持し、P + を利用する従来のTFETベースのDRAMを置き換えることができます。 収納エリアとしてのポケット領域。 N + の場合 ポリシリコンGate1、Gate1とGate2の間のアンダーラップ領域の正孔濃度は低く、読み取り操作に役立ちます。したがって、P + ポリシリコンGate2は、N + でありながら、より長い保持時間を促進できるより深いストレージ領域を作成するように選択されています。 ポリシリコンGate1は、読み取り操作中にトンネリングメカニズムを制御するために選択されます[20]。図1aでは、S_SpacerとD_Spacerは、それぞれソース側とドレイン側のスペーサーを指します。 G_spacerは、Gate1とGate2の間のスペーサーを指します。スペーサーのデフォルトの材料はSiO 2 です。 。デフォルトのデバイスパラメータは次のとおりです。シリコン膜の厚さ(T si )は20 nm、Gate1の長さ(L g1 )は400 nm、Gate2の長さ(L g2 )は200 nm、ゲートギャップの長さ(L ギャップ )は50 nmで、ゲート酸化物HfO 2 の厚さ (T 酸化物 )は3nmです。

a デュアルゲートTFET(DGTFET)DRAMセルの概略図。 b シミュレートされた伝達特性とSOITFETの実験結果との比較[25]

DGTFET DRAMのシミュレーションは、非ローカルBTBTモデルを使用してSilvacoAtlasで実行されます。非局所BTBTトンネリングモデルは、エネルギーバンドの空間的変動と反対のキャリアタイプの生成/再結合を考慮に入れています[24]。トンネリングモデルのパラメータは、SOITFETの実験結果[25]に従って較正されます。電子と正孔のトンネル質量は0.22m 0 になるように調整されます および0.52m 0 、それぞれ、ここでm 0 電子の残りの質量です。 SOI TFETのシミュレートされた伝達特性は、この論文で適用されたモデルを承認する図1bに示すように、実験結果と一致しています。ソース領域とドレイン領域での高濃度ドーピングのため、バンドギャップ狭小化モデルとフェルミディラック統計も考慮されます。さらに、Shockley-Read-Hallの再結合、ドーピング、電界依存の移動度モデルも適用されます。すべてのモデルパラメータは[19、20]のパラメータと一致しています。キャリア寿命は、保持動作中のキャリア生成/再結合を支配するため、DGTFTETDRAMのRTに影響を与えます。 [26,27,28]で1μsから10nsの間で変化するさまざまなキャリア寿命に従って、電子と正孔の寿命は100nsに設定されます。 Scharfetter関係モデルとSchenkモデルは、それぞれドーピングと寿命の温度依存性を含めるために使用されます。

結果と考察

操作メカニズム

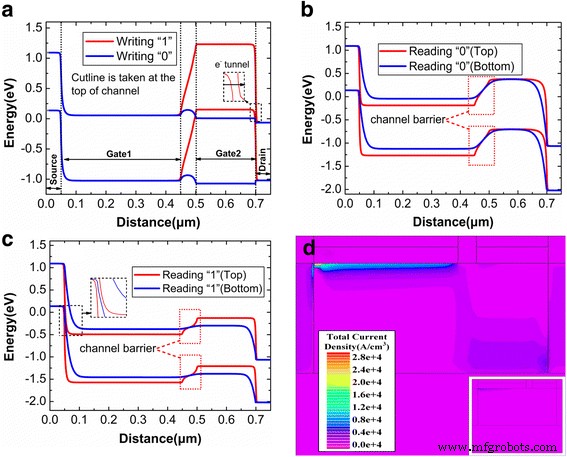

DGTFET DRAMでは、書き込み操作と読み取り操作は、それぞれドレインとソースのトンネリングジャンクションでBTBTによって制御されます。図2は、さまざまな操作中のエネルギーバンドを示しています。図2aに示すように、「1」の書き込み中に、負のバイアスを持つGate2は、Gate2の下のチャネルのエネルギー帯域を大幅に上回り、ドレイン側に非常に小さなトンネル障壁が作成されます。したがって、図3aに示すように、電子はドレイン側にトンネルし、正孔は深ポテンシャル井戸(1.2 V)に蓄積されます。 「0」を書き込んでいる間、正のバイアスを持つGate2は、正孔をこのポテンシャルからうまく排出させ、ドレイン側で再結合させます[29]。図2b、cは、それぞれ「1」と「0」を読み取った後のエネルギーバンドを示しています。図2bは、Gate1とGate2の間にチャネルバリアがあることを示していますが、これはチャネルの下部には存在しません。また、ソース側のトンネリング距離は、チャネルの上部で小さくなっています。これは、「1」の読み取り中に傾斜した伝導経路(Gate1の前面インターフェースからGate2の背面インターフェースへ)が形成されることを示しています。これは、図2dの電流密度によっても示されます。 「0」の読み取り中に、明らかなチャネルバリアが図2cに見られます。これは、「0」の読み取り電流を抑制します。図2dの挿入図は、ソース領域からトンネリングする電子がこのチャネルバリアを通過して、より高い読み取り値の「0」電流を形成できないことを示しています。

ソースからドレインまでのエネルギーバンド。 a 負のGate2バイアスで「1」を書き込んだ後、および正のGate2バイアスで「0」を書き込んだ後のエネルギーバンド。 b 「1」を読み取った後のチャネルの上部と下部のエネルギーバンド。 c 「0」を読み取った後のチャネルの上部と下部のエネルギーバンド。 d 「1」を読み取った後の総電流密度

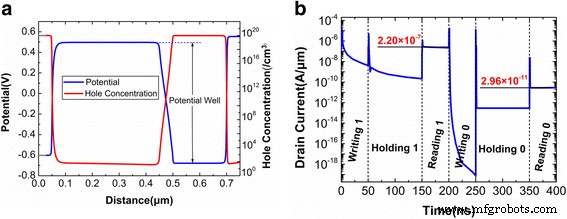

a 「1」を書き込んだ後のチャネル表面の電位と正孔の濃度。 b 表1で動作するDGTFETDRAMのドレイン電流の過渡応答

DGTFET DRAMには、適切なプログラミング条件が重要です。 「1」の書き込み中に飽和BTBTが誘導されるように、Gate2にはより大きな負のバイアスを適用する必要があります。 「1」を保持している間、Gate2に小さな負のバイアスが適用され、ポテンシャル井戸に穴を長期間保持します。読み取り操作の場合、Gate1バイアスが高いと、「1」の読み取り中にBTBTが強化されますが、「0」の電流の読み取りには悪影響があります。適切なバイアスを持つGate2は、読み取り値の「1」電流を増加させるだけでなく、読み取り値の「0」電流を弱めることもできます。表1の最適化されたプログラミング条件を適用して、デフォルトのパラメータを使用したDGTFETDRAMの過渡応答を図3bに示します。書き込み時間と読み取り時間、および保持時間は、それぞれ50nsと100nsに設定されています。得られた「1」の読み取り値と「0」の読み取り値の現在の比率は、約10 4 です。 、これは[17、19、20]と同じです。

<図>スペーサー誘電体の影響

DGTFET DRAMでは、3つのスペーサー(S_Spacer、G_Spacer、およびD_Spacer)でlow-kまたはhigh-k誘電体を使用すると、その性能に影響します。この設計では、low-kおよびhigh-k誘電体がSiO 2 を選択します。 およびHfO 2 、 それぞれ。各スペーサーがSiO 2 を使用する場合 またはHfO 2 、スペーサーエンジニアリングの組み合わせは全部で8つあります。より包括的な分析のために、「1」( I )の読み取りを含む、各組み合わせでのDGTFETDRAMのパフォーマンスプロパティ 1 )および「0」( I 0 )電流と流動比率( I 1 / 私 0 )は、表2に示すように、過渡応答から抽出されます。RTを評価するために、これらのパラメータは、保持時間が2秒に増加したときにも抽出されます。これについては、次のセクションで説明します。表2で、文字「S」と「H」はSiO 2 を表します。 およびHfO 2 、それぞれ、および各略語の3文字は、それぞれS_Spacer、G_Spacer、およびD_Spacerを表します。

<図>表2から、最適なスペーサーエンジニアリングを選択できます。 私 1 約10 -7 A /μmおよび10 -9 SiO 2 の場合のA /μm およびHfO 2 それぞれS_Spacerで使用されます。 D_SpacerがHfO 2 を適用するとき 、 I 0 低いから約10 -14 A /μm。したがって、DGTFET DRAMの最適なスペーサー構成は、ソース側とドレイン側でlow-kおよびhigh-k誘電体を使用することです。具体的な理由は、次のセクションで体系的に分析されます。

S_Spacer誘電体の影響

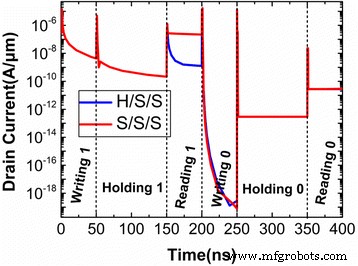

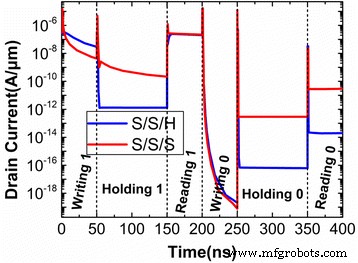

S_Spacerの影響を分析するために、H / S / SとS / S / Sのドレイン電流の過渡応答を図4で比較します。「1」電流の読み取り値が約2改善されていることがわかります。 SiO 2 の場合は桁違い S_Spacer誘電体として選択されています。

表1で動作するH / S / SおよびS / S / Sのドレイン電流の過渡応答

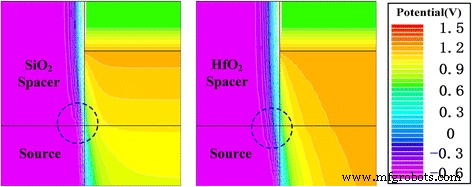

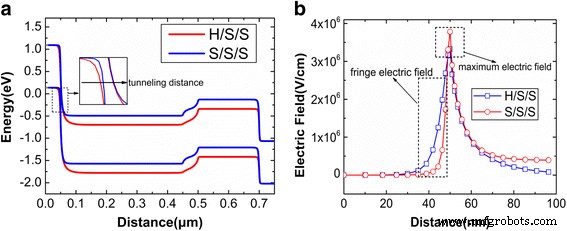

図5は、S / S / SとH / S / Sの潜在的な等高線を示しています。ソーストンネル接合では、図5の円に示すように、H / S / Sの表面空乏領域がS / S / Sの表面空乏領域に比べて明らかに拡張されています。拡張された表面空乏領域は、トンネル障壁の幅を広げます。図6aは、「1」を読み取った後のエネルギーバンドを示しています。この図の局所的な拡大領域に示されているように、H / S / Sのトンネリング距離(矢印を参照)は、拡張された表面空乏領域によって引き起こされるS / S / Sのトンネリング距離よりも明らかに大きくなっています。また、「1」を読み取った後のソーストンネリング接合部上部の電界を図6bに示します。 H / S / Sのフリンジ電場はS / S / Sのフリンジ電場よりも大きいことがわかり、これが表面空乏領域の拡大の主な理由です。一言で言えば、high-k(HfO 2 )誘電体は、より大きなフリンジ電界を生成するため、ソーストンネリング接合部の表面空乏領域が拡張され、電子のトンネリング距離が増加し、読み取り値の「1」電流が減少します。さらに、図6bから、S / S / Sの最大電界がH / S / Sの最大電界よりも大きいこともわかります。 BTBTレートと電界の間の指数関数的な関係により、S / S / Sのトンネル電流はH / S / Sのトンネル電流よりもはるかに大きくなります[30]。したがって、low-k誘電体(SiO 2 )を備えたS_Spacer )「1」電流を読み取るのに役立ちます。

「1」を読んだ後のS / S / S(左)とH / S / S(右)の潜在的な輪郭

a ソースからドレインまでのエネルギーバンドと b ソーストンネリングジャンクションの上部の電界

図6aでは、S_Spacer誘電体もチャネル領域のエネルギー帯域に影響を与えます。図6bでは、S / S / Sの電界はチャネル領域で大きいため、そのチャネル電位はH / S / Sの電界よりも小さくなっています。その結果、S / S / Sでより高いエネルギーレベルを見つけることができます。しかし、これはトンネル障壁と「1」電流の読み取りに影響を与えることはできません。

D_Spacer誘電体の影響

続いて、D_Spacerもこの論文で調査されます。一定のS_SpacerとG_Spacer(SiO 2 これらの2つのスペーサーで使用されます)、異なるD_Spacer誘電体によって引き起こされる異なる過渡ドレイン電流を図7に示します。「1」の読み取りと「0」の書き込みを除いて、他の操作はD_Spacer誘電体に明らかに依存しています。これは、D_Spacerが読み取り「1」伝導パス(Gate2の下のチャネルの下部)から遠く離れているためです。以前の操作メカニズムから、書き込みおよび保持操作はGate2によって制御されるため、D_Spacer誘電体がこれら2つの操作に影響を与える可能性があることがわかります。

表1で動作するS / S / HおよびS / S / Sのドレイン電流の過渡応答

保持動作中、「1」の書き込み中に蓄積された穴はポテンシャル井戸から除去され、ドレイン側で再結合されます。したがって、保持「1」電流は主にSRH再結合電流に由来します。 S / S / Sのチャネルに対するGate2の制御性が高いため、S / S / Sの再結合率は高く、「1」電流を保持します。ただし、「1」の読み取り中のBTBT電流よりもはるかに小さいため、「1」電流の読み取りに高い保持「1」電流を反映することはできません。

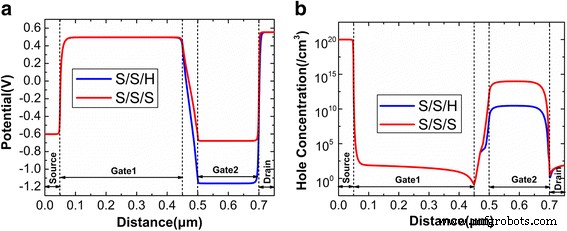

「1」の書き込み中、D_Spacer誘電体はポテンシャル井戸の深さに大きく影響します。図8aの等高線は、HfO 2 を備えたD_Spacerを示しています。 誘電体はより深いポテンシャルを生み出します。これは、ドレインとチャネル間の有効なBTBTがより深いチャネル領域に拡張されることを意味します。したがって、S / S / Hの書き込み「1」電流はS / S / Sの書き込み電流よりも高くなります。 「0」を保持している間、ゲート2に小さな負のバイアス(− 0.2 V)が適用されますが、ゲート2の下にチャネルのエネルギー帯域を設定することもできます。これにより、ドレイン側にBTBTが誘導されます。以前の分析を通じて、SiO 2 を使用したD_Spacerであることがわかります。 誘電体は、「0」を保持している間、ドレイントンネリング接合部でBTBTを強化します。これは、図8bに示すように、S / S / Sの正孔濃度が高いことで証明できます。したがって、SiO 2 を使用したD_Spacer 誘電体は、より高い保持「0」電流になります。

a 「1」を書き込んだ後の潜在的な輪郭。 b 「0」を保持した後の正孔濃度

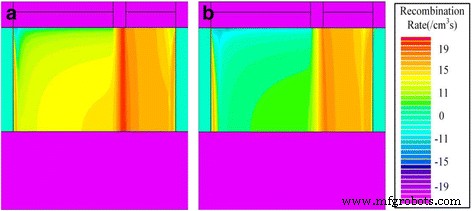

「0」の読み取り中、Gate1とGate2の間のチャネルバリアが電子のドレイン側への流れを妨げるため、S / S / HとS / S / Sの「0」電流の読み取りの違いは主に再結合電流によって引き起こされます。 。 S / S / Sの保持「0」の間に蓄積される正孔が増えるため、図に示すように、エネルギーバンドの低下により、S / S / Sの再結合率が「0」の読み取り中のS / H / Sの再結合率よりも大きくなります。その結果、D_SpacerがSiO 2 を使用する場合 、より高い読み取り値の「0」電流は、「0」を保持している間に蓄積されたより多くの正孔によって引き起こされるより高い再結合電流に起因するはずです。

a の組換え率 S / S / Sおよび b 「0」を読んだ後のS / S / H

要約すると、DGTFET DRAMの最適なスペーサーエンジニアリングは、ソース側とドレイン側のスペーサーがそれぞれlow-kとhigh-kの誘電体を適用することです。表2から、他のスペーサーが変更されていない場合、G_SpacerはDGTFETDRAMに影響を与えないことがわかります。これは、書き込みおよび読み取り操作を支配するBTBTがG_Spacerの影響を受けないためです。

保持時間

前に説明したように、「1」と「0」を保持している間の正孔の再結合と生成は、それぞれ状態「1」と「0」を劣化させます。そのため、より長い保持時間でのDGTFETDRAMの性能低下を検討する必要があります。表2では、 I 1 および私 0 保持時間の増加とともに大幅に劣化します。すべてのデバイスで、 I 1 / 私 0 まだ10 4 より大きい 保持時間が2秒に上昇したときに最適なスペーサーエンジニアリング(S / S / HおよびS / H / H)を備えたデバイスの場合。

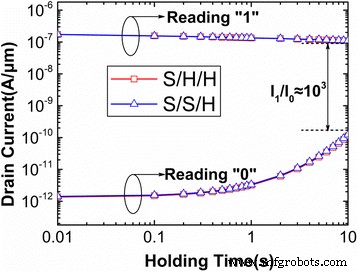

一般に、最大センスマージン( I 間の差)を減らすために必要な保持時間 1 および私 0 )50%がRTとして評価されます。この設計では、より厳密なRTは、 I の最大保持時間として定義されています。 1 / 私 0 10 3 より高い 。図10は、S / S / HおよびS / H / Hの保持時間による読み取り電流の変化を示しています。 S / H / SとS / H / Hの流動比率は10 3 と高いことがわかります。 保持時間が10秒に上昇したとき。その結果、最適なスペーサーエンジニアリングを備えたDGTFETDRAMのRTは10秒に達する可能性があります。これは、目標値の64ミリ秒よりもはるかに高くなっています。表3は、この作業のパフォーマンスプロパティを[17,18,19,20]のパフォーマンスプロパティと比較しています。 [19、20]では、流動比率はわずか10 2 です。 、RTは10秒よりはるかに小さいです。さらに、この作業での「0」電流の読み取り値は、[19、20]の読み取り値よりも2桁低くなっています。 FD-SOI TFET DRAMに関する実験結果も、読み取り値の「0」電流とRTがこの作業よりも劣っていることを示しています。この優れた性能は、DGTFETが低電力DRAMの代替品であることを示しています。スペーサーエンジニアリングの最適化により、DGTFET DRAMは低い読み取り値の「0」電流と高いRTを取得します。これは、静的および動的な消費電力の削減に役立ちます。

S / S / HおよびS / H / Hの保持時間による読み取り電流の変化

DGTFETDRAMのスケーラビリティ

DGTFET DRAMは、大きなサイズのコンデンサを排除することでメモリセル密度の問題を解決しますが、そのスケーラビリティを検討する必要があります。スケーラビリティの目標は、RTを2秒より高く保つことです。表4は、 L の減少に伴うS / S / Hのパフォーマンスプロパティを示しています。 g1 、 L g2 、および L ギャップ 。表4では、各略語の3つの数字は L を表しています。 g1 、 L ギャップ 、および L g2 。

<図>表4から、 I 1 L g1 の場合、極端に減少します 200nmから100nmに減少します。 L g1 のスケーリング 100 nmを超えると、n型に起因するバリアが狭くなり、ゲートの可制御性が低下し、 I が低下します。 1 。 私 0 L の減少に伴い、大幅に増加します g1 および L g2 。 L の削減 g2 Gate1とGate2の間のチャネルバリア幅を狭くします。これにより、電子の一部がバリアを通過して、より高い I を形成します。 0 。さらに、 L の継続的なスケールダウン g1 「0」の読み取り中にチャネルの表面でトンネル電子を制限するGate1の機能を弱めます。表4では、 L ギャップ I に明らかな影響はありません 1 、しかし私 0 L の減少に伴い、わずかに増加します ギャップ 。 L を減らす ギャップ 20 nm未満では、Gate2へのより高いトンネリングが可能になり、状態が「0」に低下するため、保持時間が短縮されます。

I を確実にするために 1 / 私 0 保持時間が10 2 より大きい と2秒、それぞれ最小の L g1 、 L g2 、および L ギャップ それぞれ200、150、20nmと見なされます。この最小デバイスサイズは、表3に示すように、[17,18,19,20]の最小サイズよりもわずかに小さくなります。ただし、DGTFET DRAMの最小サイズは、20 nm / 18nmノードの1T1CDRAMの最小サイズよりも大きくなります[31 ]、これはDGTFETDRAMに固有の欠点です。しかし、スペーサーエンジニアリングの最適化の助けを借りて、コンデンサーレス、低電力、および高RTの利点を無視することはできません。 DGTFETDRAMのサイズを100nmを超えて縮小することが、今後の作業の焦点になります。

結論

この論文では、DGTFETDRAMのスペーサーエンジニアリングの最適化をSilvaco-Atlasツールで研究しています。ソース側とドレイン側のスペーサーは、DGTFETDRAMのパフォーマンスに主な影響を及ぼします。 HfO 2 を使用したソーススペーサーによる拡大フリンジ電界 ソーストンネリングジャンクションで表面空乏領域が拡張され、読み取り値の「1」電流が減少します。 SiO 2 の場合 ドレインスペーサーに誘電体が使用されているため、BTBTが強いほど、「0」を保持している間により多くのホールが誘導され、「0」を読み取る際の再結合電流が増加します。したがって、最適なスペーサーエンジニアリングは、ドレインスペーサーとソーススペーサーにそれぞれlow-kとhigh-kの誘電体を使用することです。スペーサーエンジニアリングの最適化により、DGTFET DRAMは、他の関連する作業と比較して、読み取り「0」電流が非常に低く、保持時間(10秒)が長いという顕著な利点が得られます。さらに、スケーラビリティに関する分析では、最小デバイスサイズが最新の20 nm / 18nmノード1T1CDRAMよりも大きいことが明らかになっています。この固有の欠点は、DGTFETDRAMのサイズを100nmを超えて縮小することが、将来のDGTFETDRAMの作業の焦点になることを示しています。

略語

- DGTFET:

-

デュアルゲートトンネル電界効果トランジスタ

- DRAM:

-

ダイナミックランダムアクセスメモリ

ナノマテリアル