不揮発性メモリのスイッチング特性に及ぼす二分子膜CeO2-x / ZnOおよびZnO / CeO2-xヘテロ構造と電鋳極性の影響

要約

二層CeO 2-x を備えたメモリデバイス / ZnOおよびZnO / CeO 2-x Ti上部電極とPt下部電極の間に挟まれたヘテロ構造は、室温でのRFマグネトロンスパッタリングによって製造されました。 N型半導体材料は両方のデバイスヘテロ構造で使用されましたが、興味深いことに、ヘテロ構造と電鋳極性の変化により、抵抗スイッチング(RS)特性に大きな変動が生じました。結果は、電鋳極性が両方のCeO 2-x に大きな影響を与えることを明らかにしました。 / ZnOおよびZnO / CeO 2-x 電鋳電圧、良好なスイッチングサイクル間耐久性などのヘテロ構造性能(〜10 2 )、およびON / OFF比。 CeO 2-x を備えたデバイス / ZnOヘテロ構造は、上部と下部の界面にショットキー障壁が形成されるため、良好なRS性能を示します。高抵抗状態(HRS)の支配的な伝導メカニズムは、高電界領域でのショットキー放出でした。低抵抗状態とHRSの温度依存性の性質から、RSは酸素空孔からなる導電性フィラメントの形成と破壊によって引き起こされることが確認されました。

背景

従来のフラッシュメモリは物理的および実用的な限界に直面しているため、不揮発性メモリアプリケーションの新しい候補を探すことが非常に必要になっています。これに関して、次世代の不揮発性メモリ候補として、いくつかの新しいメモリタイプが提案されています[1、2]。これらの中で、抵抗変化型メモリ(RRAM)は、高いスケーリング機能、長いメモリ保持時間、小さなデバイスサイズ、高速スイッチング速度、低エネルギー使用率などの独自の機能により、従来のメモリの代替として最適な候補と見なされています。 、非揮発性、および単純な構造[3]。 RRAMのメモリセルは、コンデンサのような金属酸化物金属(MOM)構造です。抵抗膜の低抵抗状態(LRS)と高抵抗状態(HRS)の2つの抵抗状態間のバイポーラ抵抗スイッチング(BRS)とユニポーラRS(URS)の動作は、適切な大きさの外部電圧を印加することによって実現できます。極性[4,5,6]。

RSデバイスのスイッチング性能は、LRSおよびHRSでのSET電圧、RESET電圧、および電流レベルの均一性に依存します[7]。これらのスイッチングパラメータは、フィルム誘電体、電極材料、および製造/操作技術の影響を受けます。これらのパラメータに対するスイッチング特性の依存性を説明するために、これまでに多数のモデルが提案されてきました。スイッチング動作は、バルク制限またはインターフェイス制限のいずれかに分類できます[8]。バルク制限タイプのスイッチングの場合、スイッチングパラメータは誘電体膜の誘電率に強く依存します[9]。ただし、電極制限スイッチングは、金属-誘電体界面での電子相関と電極材料の仕事関数によるものです[10]。アノードと誘電体膜の間の界面も、メモリデバイスのRSパラメータに影響を与える可能性があります[10、11]。

いくつかの酸化物の中で、セリア(CeO 2 )は、誘電率が大きく(〜26)、ギブズの自由エネルギーが低く(− 1024 kJ / mol)、2つの酸化(Ce + 4 )があるため、RSメモリデバイスアプリケーションの有望な材料であることがわかっています。 Ce + 3 へ )状態、および非化学量論的パターンでの空孔(特に酸素空孔)の分布[12、13]。一方、酸化亜鉛(ZnO)は、その優れた特性により、さまざまな用途で広く使用されています。 ZnOは、その光学的透明性、ワイドバンドギャップ、化学的安定性、および高抵抗率(10 5 )により、誘電体として利用されていることに注意してください。 Ω-cm)[14]。最近、電鋳および/またはSET / RESET電圧の低減、スイッチングの均一性の向上、長期耐久性、および自己コンプライアンスの点で、単層ベースのデバイスよりも優れた特性を示すために、2層RSメモリ構造が提案されています[15]。 Xu etal。 [16] ZrO 2 のRSの動作を調査しました およびZnO二重層スタックは、酸素空孔の移動が酸化物界面バリアの高さに依存することを示しています。二分子膜MnO / CeO 2 で観察されたRSの挙動 構造は、CeO 2 の酸化および還元反応によるものであると提案されました。 Huらによって報告されたように。 [17]。ヤンら。 [18]は、単層ZnOベースのデバイスと比較して、2層CuO / ZnOデバイスの優れた抵抗スイッチング特性を明らかにしました。 Park etal。 [19]は、Pt / TiO x で観察されたより信頼性と再現性のあるRS動作を示しました / ZnO / Ptメモリセルは、Pt / ZnO / Ptメモリセルに記載されているものよりも優れています。 Hsieh etal。 [20]は、Ni / ZnO / HfO 2 / Niデバイスは、RESETプロセス中にマルチレベル特性を備えたバイポーラ抵抗スイッチング動作を示しました。このような改善されたRS特性はすべて、ZnO / CeO 2 のいずれかとして二重層の詳細な調査を動機付けました。 またはCeO 2 として / ZnOヘテロ構造。これらのスタックに関する研究はなく、RS特性とメモリ性能に対する形成極性の影響はまだ報告されていません。

この作業では、ZnO / CeO 2-x のRS特性に対する、二重層ヘテロ構造と電鋳極性の影響を報告しました。 およびCeO 2-x / ZnOベースのメモリデバイス。結果は、正に電鋳されたCeO 2-x / ZnOデバイスおよび負の電鋳ZnO / CeO 2-x デバイスは、より低い電鋳電圧とはるかに優れたサイクル間スイッチング耐久性を示します(〜10 2 ) パフォーマンス。反対のバイアス極性を持つこれらの二重層デバイスのLRSおよびHRS抵抗の温度依存性は、観察されたRSメカニズムが酸素空孔ベースの導電チャネルによって説明できることを示しています。

メソッド

2種類のTi / CeO 2 / ZnO / PtおよびTi / ZnO / CeO 2 / Ptヘテロ構造デバイスは、比較研究のためにこの作業で準備されました。最初のTi / CeO 2 の製造用 / ZnO / Ptヘテロ構造デバイス、ZnO薄膜(〜10 nm)の活性層が市販のPt / Ti / SiO 2 上に堆積されました ZnO(純度99.99%)セラミックターゲットを使用した高周波(RF)マグネトロンスパッタリングによる室温での/ Si(Pt)基板。堆積中、Ar:O 2 の下で75WのRF電力と約10mTorrの圧力 (6:18)混合物(流量=24sccm)を維持しました。次に、CeO 2 層(5 nm)は、同じ条件下でRFマグネトロンスパッタリングによってZnO / Pt上に堆積され、2層CeO 2 を形成しました。 / ZnOヘテロ構造。最後に、Pt / Ti上部電極(TE)は、金属シャドウマスクを使用した順次直流(DC)マグネトロンスパッタリングによって、これらのヘテロ構造の両方に堆積されました。この手法により、直径150μmの円形デバイス(メモリセル)が生成されました。ここでは、酸化からTiTEを保護するための保護層としてPtを使用しました。同様に、2番目のTi / ZnO / CeO 2 / Ptヘテロ構造デバイスも、Ti / CeO 2 で維持されているのと同じ条件下で製造されました。 / ZnO / Ptヘテロ構造。 Ti / CeO 2 の両方 / ZnO / PtおよびTi / ZnO / CeO 2 / Ptヘテロ構造メモリデバイスは、標準の2プローブ測定方法を使用したAgilentB1500A半導体パラメータアナライザによって特性評価されました。これらのデバイスの二重層構造は、クロスビュー高分解能透過型電子顕微鏡(HRTEM-JEM 2001F)を使用して特徴づけられました。

結果と考察

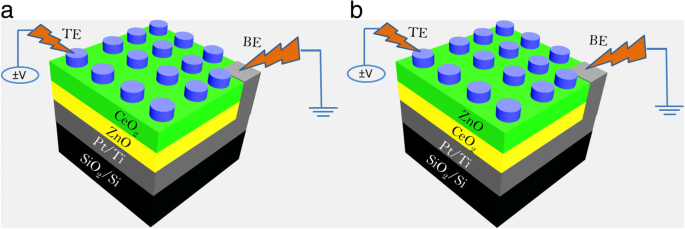

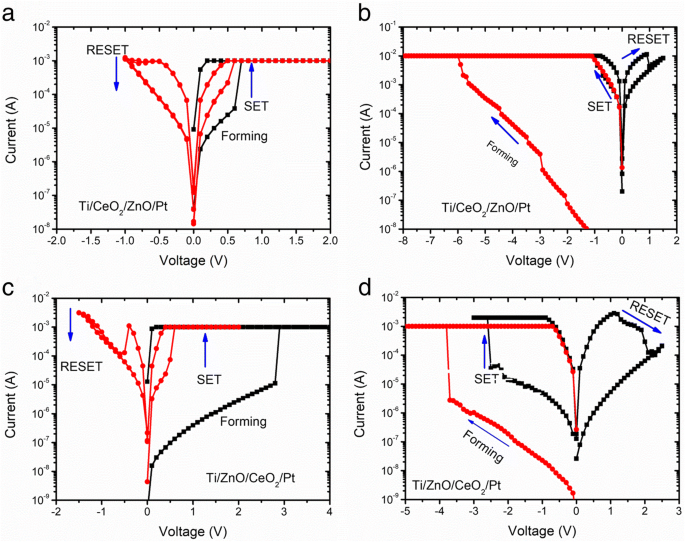

図1a、bは、二重層Ti / CeO 2 の概略構成を示しています。 / ZnO / PtおよびTi / ZnO / CeO 2 それぞれ/ Ptヘテロ構造メモリデバイス。図2a〜dは、一般的な電流-電圧( I )を示しています。 - V )Ti / CeO 2-x の曲線 / ZnO / PtおよびTi / ZnO / CeO 2-x / Ptヘテロ構造メモリデバイス。初期の電鋳プロセスも含まれ、典型的なバイポーラRS特性を示します。 + 2 Vの掃引がTEに適用された場合、0.6 Vで電流の突然のジャンプが発生し、2つの電極間に導電パスが形成されたことを示しています(図2a)。正の電鋳電圧が除去された後、デバイスはオン状態(LRS)のままでした。図2aは、デバイスが0から-1 Vまでの負の電圧スイープでHRSに正常に戻り、0から+ 1 Vまでの正の電圧スイープで再びLRSに正常に切り替わったことも示しています。反対の極性、つまり負の電鋳電圧、同じヘテロ構造メモリセルでスイッチング動作をアクティブ化/開始するためにも提供されました。この点で、TEに0〜-8 Vの掃引を加えると、デバイスの抵抗が-5.6 Vで急激に低下し、それによって負の電鋳と呼ばれるオフ状態からオンになりました(図2b)。負の電鋳後、デバイスは不可逆的な故障のため、正のRESETと負のSETに失敗しました。 RS特性を開始するには、正の電鋳電圧よりもはるかに高い負の電鋳電圧が必要であることに注意してください。ただし、負の電鋳後は、SETおよびRESET電圧の印加に関係なく、デバイスがオン状態のままであったため、スイッチングヒステリシスは観察されませんでした。この事実は、電鋳プロセス中に永久導電性フィラメントが形成されることを示しています。負の電鋳中の不可逆的な破壊は、上部電極と下部電極の仕事関数の違いによって開始されるトンネル障壁の高さが異なることに起因する可能性があります[21]。これらの結果は、Ti / CeO 2-x を備えたデバイスであることを示しています。 / ZnO / Ptヘテロ構造は、正の極性で電鋳され、その後に対応するRESETおよびSET操作の負および正の極性が続く場合にのみ、不揮発性特性に適しています。 2番目の違い(Ti / ZnO / CeO 2-x / Pt)および最初の(Ti / CeO 2-x / ZnO / Pt)デバイスは、サンドイッチヘテロ構造の絶縁層の位置です。そのため、Ti / ZnO / CeO 2-x を備えたデバイス / Ptヘテロ構造は、Ti / CeO 2-x と同様に、バイアス電位の正と負の両方の極性で電鋳することもできます。 / ZnO / Ptヘテロ構造デバイス。図2cは、一般的なバイポーラ I-V を示しています。 このような正の電鋳とその後のスイッチング動作の曲線。図2cに示すように、0〜 + 4 Vの掃引で、デバイスを電鋳してオン状態(+ 3 Vでの急激な抵抗変化)に切り替えました。次に、デバイスは、繰り返し可能なスイッチングサイクル中に、+ 2 V(正のSET)未満でオンになり、-1.5 V(負のRESET)でオフになりました。同様に、同じヘテロ構造を負に電鋳したデバイス(-3.5 V)は、図2dから明らかなように、正のRESET(+ 1.5 V)と負のSET(-2.5 V)を示しました。両方のデバイスを恒久的な故障から保護するために、電鋳およびSETプロセス中に1mAの電流コンプライアンスが適用されました。

二分子膜の概略構成 a Ti / CeO 2 / ZnO / Ptおよび b Ti / ZnO / CeO 2 / Ptデバイス

デバイスは、典型的なバイポーラ動作を示しています。 a ポジティブ(+ ve)フォーミングとそれに続くスイッチング操作および b Ti / CeO 2-x のネガティブ(-ve)フォーミングおよびスイッチング操作 / ZnO / Ptヘテロ構造。 c + veフォーミングおよびスイッチング操作と d Ti / ZnO / CeO 2-x の-veフォーミングおよびスイッチング操作 / Ptメモリデバイス。矢印は方向の切り替えを示します

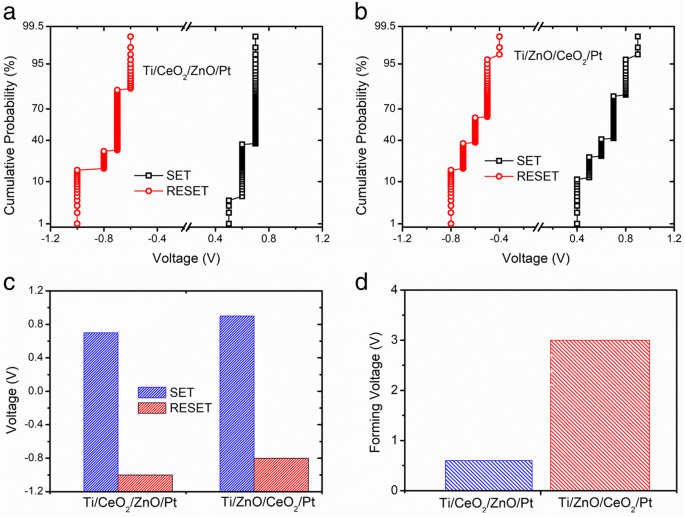

両方のヘテロ構造メモリデバイスのスイッチングパラメータの均一性を確認するために、さまざまなスイッチングサイクルで記録された動作電圧(SETおよびRESET電圧)の累積確率を図3a、bに示します。 Ti / CeO 2-x / ZnO / Ptヘテロ構造メモリデバイスは、Ti / ZnO / CeO 2-x と比較して、SETおよびRESET電圧の変動が比較的狭いことを示しています。 / Ptヘテロ構造メモリデバイス。図3c、dは、両方のヘテロ構造メモリデバイスの平均SET、RESET、および電鋳電圧の統計分析を示しています。 Ti / CeO 2-x / ZnO / Ptデバイスは、Ti / ZnO / CeO 2-x に必要な電鋳電圧と比較して、はるかに低い電鋳電圧を必要とすることがわかっています。 / Ptヘテロ構造メモリデバイスですが、SETおよびRESET電圧はわずかな変動しか示していません。両方のデバイスの動作電圧の小さな変動は、界面で発生するフィラメントの作成と破裂に関連している可能性があります。 Liu etal。 [22]は、WO x に記載されている低いSET / RESET電圧とスイッチングの均一性を示唆しています。 / NbO x 二分子層構造は、2つの酸化物層間の酸素移動と金属-絶縁体転移の複合効果に起因する可能性があります。ギブズの自由エネルギーとして、ZnOおよびCeOの酸化物形成のΔG x 約706kJ / molの大きな違いがあります(CeO 2 の場合) 、ΔG=− 1024 kJ / mol、ZnOの場合は− 318.52 kJ / mol)、局所的な加熱効果が発生すると、酸素の交換が誘導されます。 ZnO薄層は、形成エネルギーが低いために酸素空孔が多いことはよく知られています[23]。また、ZnO層に存在する多くの初期酸素空孔は、浅いトラップを介した伝導において主要な役割を果たします[24]。さらに、ZnOベースのデバイスでの形成のない現象は、ZnO結晶にすでに存在する高濃度の酸素空孔に起因する可能性があると述べられています[25]。上記のすべての事実から、両方のヘテロ構造デバイス(ZnO / CeO 2-x )に多くの酸素空孔を有するZnO膜の存在下で結論付けることができます。 およびCeO 2-x / ZnO)は、動作電圧の低減に重要な役割を果たします。 ZnOの酸素空孔は、電子の浅いトラップとして機能する可能性があり、これらのトラップサイトの電子は、SETおよびRESET電圧の小さな値で簡単にトラップまたはトラップ解除できます。

a での動作電圧のサイクルごとの累積確率分布 Ti / CeO 2-x / ZnO / Ptおよび b Ti / ZnO / CeO 2-x / Ptヘテロ構造メモリデバイス。 c Ti / CeO 2-x のSETおよびRESET電圧の統計分析 / ZnO / PtおよびTi / ZnO / CeO 2-x / Ptヘテロ構造メモリデバイス。 d Ti / CeO 2-x の両方の電鋳電圧の統計的評価 / ZnO / PtおよびTi / ZnO / CeO 2-x / Ptヘテロ構造メモリデバイス

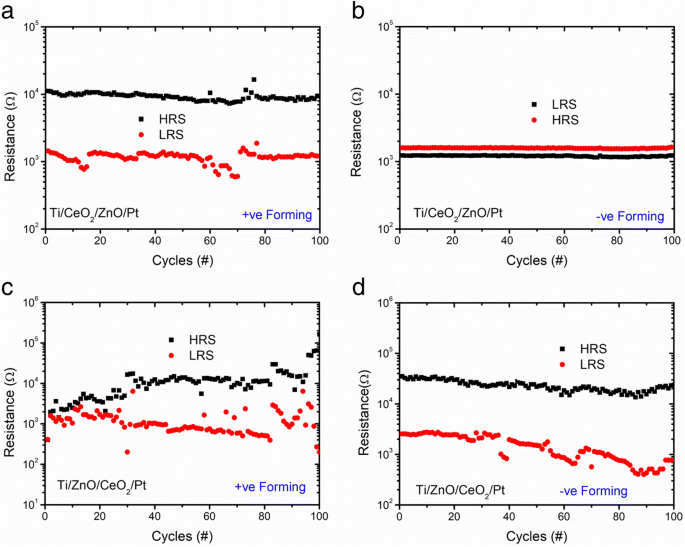

両方のデバイスのヘテロ構造の信頼性を調査するために、バイアス電位のさまざまな極性での耐久性テストを実行しました。 HRSとLRSの抵抗値は、DC耐久性スイッチングサイクルから0.2Vで取得されます。図4aは、Ti / CeO 2-x の耐久特性を示しています。 / ZnO / Ptヘテロ構造メモリデバイス。正に電鋳されたTi / CeO 2 / ZnO / Ptヘテロ構造メモリデバイスは、明確に区別できるHRSとLRSを保証できる〜10のメモリウィンドウで優れた耐久性を示しました。 Ti / CeO 2-x でのショットキー障壁の形成 インターフェースは、TiTEとCeO 2-x の隣接層との間の仕事関数の違いによるものです。 、良好なRSプロパティにつながります。同じヘテロ構造デバイスの場合(Ti / CeO 2-x / ZnO / Pt)は負に電鋳されており、図4bに示すように、デバイスをLRSからHRSに変更することはできませんでした。図4cは、正に電鋳されたTi / ZnO / CeO 2-x の耐久特性を示しています。 / Ptヘテロ構造メモリデバイスは非常に低い耐久性を示します。メモリウィンドウがほとんど折りたたまれているように見え、ON状態とOFF状態を実質的に区別できなくなります。この事実は、高濃度の空孔が存在するために注入されたキャリアをZnOが捕捉できないことに起因する可能性があります。これにより、Ti / ZnO界面に障壁が形成されないため、Ti TEへの伝導トラックが形成されます。 Ti(4.33 eV)とZnO(4.35 eV)であり、これは耐久性の低下につながります[26]。もう1つの理由は、ZnO / CeO 2-x 内の欠陥の密度が高いことである可能性があります。 酸素空孔の移動が拡張された欠陥に沿って大幅に強化されるため、強電界下で作成されたマトリックス。さらに、欠陥部位に偏析した正に帯電した酸素空孔は、表面密度状態を増加させ、ON / OFF比の崩壊をもたらします。これは、Ti / ZnOブロッキング接触が形成されると、TiからZnOへの電子の移動により、フェルミ準位が互いに整列していることを示唆しています。その結果、多数キャリアが酸化物層の表面に集まり、バリアはほとんど形成されません[26]。図4dは、負に形成されたTi / ZnO / CeO 2-x のはるかに優れた耐久特性を示しています。 正に形成されたデバイスのものと比較した/ Ptヘテロ構造メモリデバイス。朱ら。 [27] 3種類のデバイスを製造しました:(i)Ag / ZnO / NSTO / In、(ii)Ag / CeO 2 / NSTO / In、および(iii)Ag / CeO 2 / ZnO / NSTO / In。二層デバイス(CeO 2-x / ZnO)は、単層のものと比較して、約10年のデータ保持でより優れたRS動作を示しました。彼らは、二分子膜ヘテロ構造のより良いRS特性は、CeO 2-x 間の界面障壁に起因すると考えました。 / ZnO二重層構造とZnO膜のトラップ中心として機能する多数の空孔の存在。

a の耐久特性 積極的に電鋳され、 b 負の電鋳Ti / CeO 2-x / ZnO / Ptヘテロ構造メモリデバイス。 c 正の電鋳と d 負の電鋳Ti / ZnO / CeO 2-x / Ptヘテロ構造メモリデバイス

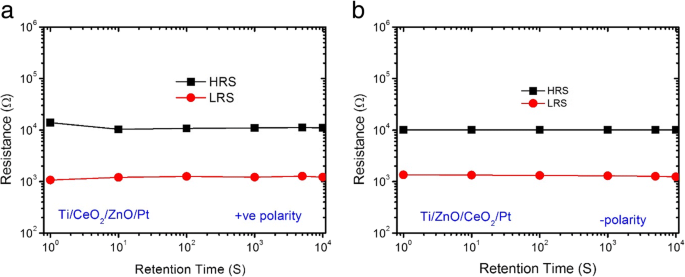

両方のCeO 2-x の保持パフォーマンス / ZnOおよびZnO / CeO 2-x 二分子膜ヘテロ構造も調べた。図5a、bから明らかなように、両方のヘテロ構造デバイスの保持時間は、0.2Vの読み取り電圧で室温で測定されました。どの状態でも抵抗を一定に保つために電力は必要ありませんでした。最大保持時間10 4 s、HRSとLRSの抵抗は劣化の兆候をまったく示さず、両方のヘテロ構造デバイスに保存された情報を10 4 よりもはるかに長い時間保持できることを意味します。 s。

a の保持特性 正に電鋳されたTi / CeO 2-x / ZnO / Ptヘテロ構造メモリデバイスおよび b 負の電鋳Ti / ZnO / CeO 2-x 室温での/ Ptヘテロ構造メモリデバイス

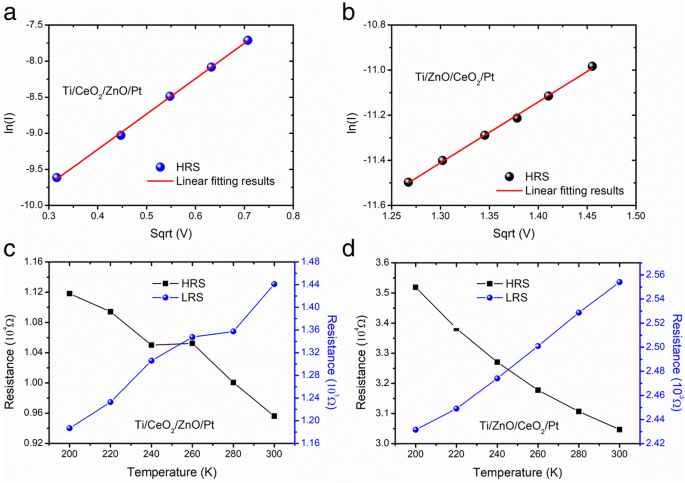

両方のヘテロ構造メモリデバイスの高電界領域で一般的な伝導メカニズムについて調査するために、カーブフィッティング手順をポジティブ(CeO 2-x の場合)で実行しました。 / ZnO)および負(ZnO / CeO 2-x の場合) )バイアス電位の極性。図6a、bは、実験データへの線形カーブフィッティングが、それぞれのバイアス極性で両方のヘテロ構造デバイスのショットキー放射動作とよく一致していることを示しています。ショットキー放出は、電極が熱的に活性化された電子をバリアを越えて絶縁体の伝導帯に注入するときに発生することが知られているため、電極制限メカニズムと呼ばれます。一般に、ショットキー放出は、電極接触が高度にキャリア単射である場合に発生します。 ln( I の線形関係 )vs.√ V 電子がエネルギー障壁を克服するのに十分な量のエネルギーを達成したことを示します。低電界領域で発生するオーム伝導(電流は印加電圧に比例)は、熱的に生成された電子によって電流が流れることを示しています(結果はここには示されていません)。ショットキー放出モデルは通常、[28]の形式の方程式で記述できます。\(\ ln(J)=\ ln {A} ^ {\ ast} {T} ^ 2-q \ left({\ varPhi} _b- \ sqrt {\ frac {qV} {4 \ pi {\ varepsilon} _o {\ varepsilon} _rd}} \ \ right)/ {k} _BT \)、ここで J は電流密度、 A *はリチャードソン定数、 T は温度、 q は電荷、 V 折衷電圧、ε r は誘電率、ε o は自由空間の誘電率、 d は膜厚で、 k B ボルツマン定数です。さらに、LRSとHRSの温度依存抵抗値は、CeO 2-x の両方について、200〜300Kの温度範囲で0.2Vの電圧で測定されました。 / ZnOおよびZnO / CeO 2-x 図6c、dに示すヘテロ構造メモリデバイス。低抵抗状態の両方のヘテロ構造デバイスの電気輸送特性は本質的に金属であることに注意することができます。つまり、LRSの抵抗は温度の上昇とともに増加します。これとは対照的に、HRSの両方のデバイスの電気輸送特性は、本質的に半導体です。つまり、HRSの抵抗は、温度の上昇とともに減少します。活性化エネルギーの値( E a )両方のヘテロ構造デバイスのLRSのアレニウスプロットから得られたもの(結果は表示されていません)は〜0.092 eVであり、酸素空孔の最初のイオン化エネルギー(〜0.1 eV)に匹敵します[25、26、29]。酸素空孔のイオン化はHRSでの伝導の原因であり、HRSの動作伝導メカニズムとしてのショットキー放出の優位性をさらに確認します。両方のヘテロ構造デバイスのLRSでの金属挙動とHRSでの半導体挙動は、Ti / CeO 2-x でのスイッチング挙動をサポートする十分な証拠を提供します。 / ZnO / PtおよびTi // ZnO / CeO 2-x / Ptヘテロ構造メモリデバイス。酸素空孔ベースの導電性フィラメントメカニズムに関連付けることができます。

log I-V 1/2 SET状態のHRSの特性。 a Ti / CeO 2-x の場合 / ZnO / Pt。 b Ti / ZnO / CeO 2-x の場合 / Ptヘテロ構造メモリデバイス。 c のLRSとHRSの温度依存性 Ti / CeO 2-x / ZnO / Ptおよび d Ti // ZnO / CeO 2-x / Ptヘテロ構造メモリデバイス

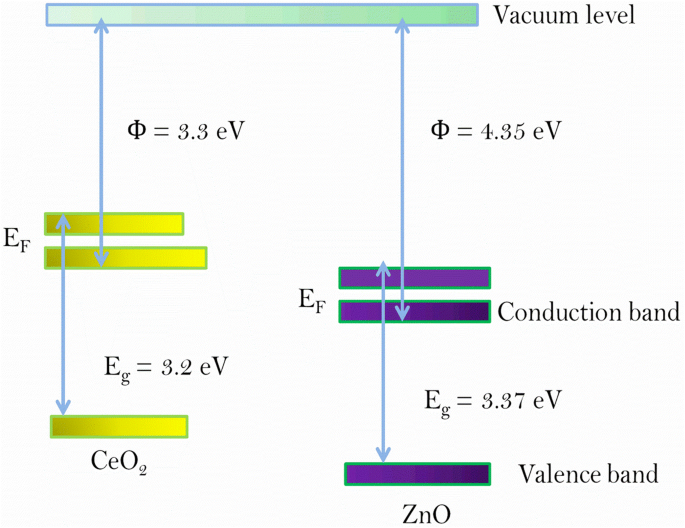

図7は、CeO 2 の提案されたエネルギーバンド図を示しています。 定常状態のZnOn-n型半導体材料。 ZnO(4.35 eV)とCeO 2 の仕事関数の違い (3.33 eV)は、酸素空孔の同じ電子遷移に対して1.02eVに等しくなります[30]。 CeO 2 の下部仕事関数 (3.33 eV)は、ZnO(4.35 eV)よりもCeO 2 からの電子の移動を可能にします。 ZnOに変換され、マトリックス中の濃度が高くなります。

CeO 2 のエネルギーバンド図 およびZnOn型半導体材料

以前の研究[31]によると、単層Ti / CeO 2-x のRS特性 / Ptデバイスは、導電性フィラメントパスの作成と破壊に重要な役割を果たすTiO界面層の形成に起因していました。 Warule etal。 Ti / ZnO / PtデバイスのRS挙動は、酸素空孔ベースの導電性フィラメントの作成と切断によって引き起こされると提案しました[32]。さらに、Ti / ZnO / Ptデバイスのフォーミングフリー現象は、準備されたままのTi / ZnO / Ptデバイスにかなりの量の酸素空孔が存在することに関連しています[32、33、34]。 ZnO / Pt界面でのショットキー障壁は、ZnO膜に適切な量の酸素空孔が存在することによって排除することができ、その結果、ZnO / Pt界面でオーミック接触が生じる。したがって、TiO界面層の形成は、二重層ZnO / CeO 2-x のRS効果と関連付けることができます。 およびCeO 2-x / ZnOヘテロ構造。 Tiは大気中の酸素と反応性の高い金属であることがよく知られているため、Ti /酸化物界面にTiO層を容易に形成することができます[35]。 Ti / ZnO / CeO 2-x / Ptヘテロ構造メモリデバイスであるZnOはn型半導体であり、酸素空孔が多く含まれているため、Ti / ZnO界面にオーミック接触が形成されます[36]。 TiとZnOの仕事関数はほぼ同じであるため、TiはZnOから酸素イオンを抽出してTiO界面層を形成することはできません。非格子状の酸素イオンと格子欠陥に関連する酸素がZnO膜に存在することが報告されています[37]。セリアの沈着による(CeO 2 )室温でのRFスパッタリングにより、CeO 2 を製造 フィルムは本質的に多結晶です。したがって、セリアがCeO 2-x に還元されることを以前の研究ですでに証明したように、セリアフィルムは非化学量論的である可能性があります。 [12]。 Hu etal。 [17]は、CeO 2 のそのような減少も報告しました CeO 2-x への堆積中 。 CeO 2-x の欠陥 フィルムは酸素イオンを動員するには不十分です。したがって、CeO 2-x 層は、Ti / ZnO / CeO 2-x の酸素貯蔵器として機能します / Ptヘテロ構造。 CeO 2 の形成のためのギブのエネルギー は前述のようにZnO(− 318.52 kJ / mol)よりもはるかに小さい(− 1024 kJ / mol)ため、化学量論的でない性質のためにZnOに非格子酸素が存在し、CeO 2に向かって移動します。 外部バイアスがない場合でも層[37]。したがって、Ti TEがZnO上に堆積されると、TiOの形成のギブスエネルギーはZnOのそれよりも小さいが、TiとZnOとの間に界面層が形成されることは予想されない。 TEに正の電圧を印加すると、酸素イオンがCeO 2-x に引き付けられます。 / Pt界面と導電性フィラメントは、ドリフトとライン配置能力のために酸素空孔で生成されます。

一方、Ti / CeO 2-x / ZnO / Ptヘテロ構造メモリデバイスでは、Ti / CeO 2-x に非常に薄い界面TiO層が形成されます。 HRTEM画像(図1c)から明らかであり、以前の研究[37]で示唆されているようにインターフェース。 TiOのギブズ形成エネルギー(− 944 kJ / mol)は、CeO 2-x のそれよりも比較的大きい (− 1024 kJ / mol);したがって、Tiは酸素親和性が高いため、CeO 2-x から酸素イオンを捕捉します。 界面TiO層を形成するために、酸素イオンの一部がCeO 2-x に戻ります。 外部の負のフィールドが存在しない/存在する場合のレイヤー[38]。 TiOとZnOの酸化物形成のギブズエネルギーは、それぞれ-944 kJ / molと-318.52kJ / molです。したがって、(1/2)CeO 2 の酸化物形成のギブズエネルギーを得ることができます。 =− 512 kJ / mol。 ZnOと比較すると、Ceの酸素親和性はZnの酸素親和性よりも少し高いため、酸素イオンはZnOからCeOに拡散します 2-x 層、次にTiO層に移動し、そこからこれらのイオンがTEに移動して、酸化物層に酸素空孔を残します。その結果、すべての酸素イオンが上部界面に集まり、電極間に酸素空孔を備えた導電性フィラメントが形成されます。反対のバイアス極性が存在する場合、酸素イオンは酸化物層に送り返され、その結果、酸素空孔が満たされ、フィラメントが破裂します。

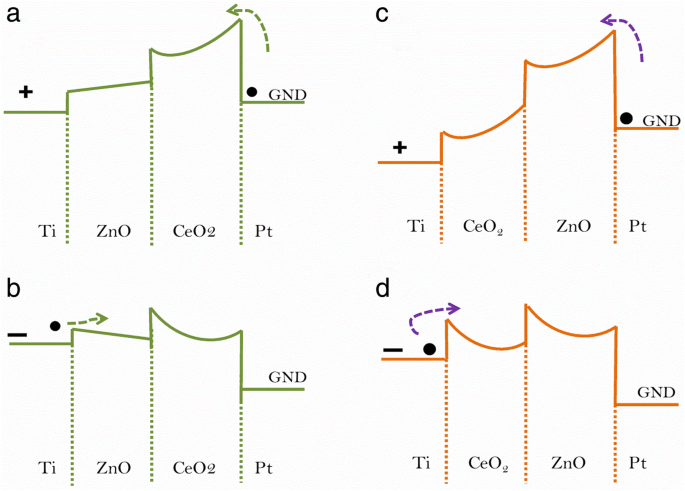

上部のTi電極と下部のPt電極の仕事関数は、それぞれ4.33と5.65eVです[39]。 ZnOの電子親和力と仕事関数(3.37eVと4.35eV)は、CeO 2 よりも高くなっています。 (3.50eVおよび3.2eV)[40]。したがって、ZnO / CeO 2-x でのエネルギー障壁 ショットキー障壁のように、インターフェースが期待されます。正の電圧領域では、CeO 2 の欠陥から電子を簡単に注入することはできません。 ZnOの仕事関数はCeO 2 よりも高いため、Pt下部電極からZnO層へ 。そのため、電子はZnOからTi上部電極にドリフトする能力が低くなります。これは、Tiが同様の仕事関数のためにZnOから酸素イオンを引き付けることができないためです。上部のTi / ZnOおよびCeO 2-x でのバリアの高さ / Pt下部インターフェースはそれぞれ0.05eVと2.45eVで、CeO 2 でのバリアの高さです。 / Pt下部界面は高いため、金属から誘電体への電子のトリガーが容易ではなく、下部界面にショットキー障壁が形成されます[41]。

ただし、上部のTi / ZnO界面の障壁の高さは、同様の仕事関数のために無視できるほど小さいですが、下部のCeO 2-x でははるかに高くなっています。 / Ptインターフェースは、バイアスフィールドの極性が2つのインターフェースのバリア高さのバランスをとるのに十分でない理由です。したがって、Ti / ZnO / CeO 2-x の耐久性とスイッチング特性 / Ptヘテロ構造は、印加されたバイアスの正極性にはあまり適していません。負の電圧掃引がTi上部電極に印加されると、Ti / ZnO / CeO の上部Ti / ZnO界面にショットキー障壁が形成されないため、TiTEからの電子注入はTi / ZnO界面の障壁を制御できません。 2-x / Ptヘテロ構造(図8a、bに示す)

a の伝導バンドオフセットの概略図 、 b Ti / ZnO / CeO 2-x / Ptおよび c 、 d Ti / CeO 2-x / ZnO / Ptヘテロ構造メモリデバイス。矢印は、スイッチング極性に応じた電子のドリフト方向を表しています

一方、正電圧領域では、ZnOの欠陥を介してPt電極からCeO 2-x に電子を容易に注入できます。 層。次に、これらの電子はCeO 2-x からドリフトします。 Ti上部電極への層。トップTi / CeO 2-x のバリアの高さ (1.13 eV)と下部のZnO / Pt(2.28 eV)の界面は、図8c、dに示すようにショットキー放出を示唆しています。負の電圧がTi上部電極に掃引されると、上部電極からの電子注入は、Ti / CeO 2-x のこのショットキーバリアによって制御されます。 トラップとデトラップの現象は、下部バリア(1.13 eV)で簡単に発生する可能性があるためです。酸素イオンはTi / CeO 2-x に移動できます 正の電圧を印加することによってインターフェースします。 Ti / CeO 2-x のRSメカニズム / ZnO / Ptヘテロ構造メモリデバイスは、酸化物層に酸素空孔を持つ導電性フィラメントの作成と溶解によって説明できます[41]。これは、酸素イオンがTi / CeO 2-x 間を行き来できることを意味します。 外部バイアスの2つの反対の極性による界面層と酸化物層。 Ti電極に正の電圧を印加すると、CeO 2-x から酸素イオンがドリフトします。 / ZnOからTi / CeO 2-x インターフェース。酸化物層に酸素空孔のある導電性フィラメントが形成され、その結果、抵抗状態がOFF-(HRS)からON-state(LRS)に切り替わります。 Ti TEに負の電圧が印加されると、トラップ解除のプロセスが開始され、酸素イオンがTi / CeO 2-x に集まります。 インターフェースは下部電極に向かって戻されます。導電性フィラメントは、酸素イオンの移動により破裂します。したがって、デバイスは再びHRSに戻されます。現在の結果に基づいて、CeO 2-x などのデバイスヘテロ構造の影響を調査しました。 / ZnOおよびZnO / CeO 2-x 抵抗変化型メモリデバイスで考えられるアプリケーションの抵抗スイッチングパラメータの電鋳極性。デバイス構造とその電鋳極性の両方が、電鋳電圧、メモリウィンドウ、SET / RESET電圧の均一性などのスイッチングパラメータに大きな影響を与えることに気づきました。ただし、将来の研究では、プログラミング/消去時間の短縮、スケーラビリティの向上、電鋳のない、ローキャストデバイスを実現するために、より多くの注意が必要です。特に、絶縁層に埋め込まれたナノ結晶または金属イオンのいずれかを利用し、バッファ層構造上にデバイスを製造することで、適切な電極材料を選択するための作業が必要です。

結論

結論として、RSの振る舞いに関する詳細な調査は、二重層ZnO / CeO 2-x の形態を変更することによって行われました。 およびCeO 2-x / ZnOヘテロ構造と電鋳極性の兆候。性能、耐久性、電鋳電圧、動作電圧の均一性に大きな影響があります。実験結果は、Ti / CeO 2-x におけるTiO界面層の形成を明らかにしています。 正極性のバイアスを適用した場合の/ ZnO / Ptヘテロ構造、およびCeO 2-x 負極性の層は、Ti / ZnO / CeO 2-x の酸素貯蔵庫として機能します / Ptヘテロ構造。まとめると、RSパラメータの均一性と再現性を向上させるために重要な役割を果たすことができます。 HRSの主な伝導メカニズムは、高電界領域での電極制限ショットキー発光でした。 LRSおよびHRS抵抗の温度依存性は、観察されたRSメカニズムが印加電圧下での酸素空孔の動きに基づいているという結論につながります。

略語

- BRS:

-

バイポーラ抵抗スイッチング

- DC:

-

直流

- HRS:

-

高抵抗状態

- HRTEM:

-

高分解能透過型電子顕微鏡

- LRS:

-

低抵抗状態

- MOM:

-

金属-酸化物-金属

- RRAM:

-

抵抗変化型メモリ

- RS:

-

抵抗スイッチング

- TE:

-

上部電極

- URS:

-

ユニポーラ抵抗スイッチング

ナノマテリアル

- MnХFe3−XО4スピネルの構造的および磁気的特性に及ぼす接触非平衡プラズマの影響

- フラーレン由来のナノ材料とそれらのポリマー複合材料の常磁性特性:劇的なポンピングアウト効果

- 光触媒活性と安定性を強化するためのIn2O3ナノ粒子ハイブリッド双晶六角形ディスクZnOヘテロ構造の水熱合成

- Al2O3 / ZnOナノラミネートの形態的、光学的、および電気的特性に及ぼす二重層の厚さの影響

- 界面層の設計によるZnO膜の表面形態と特性の調整

- 超循環原子層堆積によるZnO膜のフェルミ準位調整

- ZnOナノ結晶の合成と逆ポリマー太陽電池への応用

- Cu / Ti3SiC2 / Cナノコンポジットの微細構造と機械的性質に及ぼすグラフェンとMWCNTの相乗効果

- ポリオール媒介プロセスによるZnOナノクリップの製造と特性評価

- 赤外領域におけるAlドープZnO膜の光学的性質とそれらの吸収への応用

- 酸化亜鉛/多孔質陽極酸化アルミナ複合膜の調製とアンチバイオフィルム特性