28 nmCMOSプロセスでのESD保護のためのPMOSFETが組み込まれた堅牢でラッチアップ免疫LVTSCRデバイス

要約

低電圧でトリガーされるシリコン制御整流子(LVTSCR)は、低電圧集積回路に静電放電(ESD)保護を提供することが期待されています。ただし、保持電圧が非常に低いため、通常はラッチアップ効果に対して脆弱です。この論文では、EP-LVTSCRと呼ばれる追加のp型MOSFETが埋め込まれた新しいLVTSCRが提案され、28 nmCMOSテクノロジで検証されました。提案されたデバイスは、〜6.2 Vの低いトリガー電圧と〜5.5 Vの大幅に高い保持電圧を備えており、送電線パルステストでの故障電流の低下はわずか23%です。また、EP-LVTSCRは、3.63 Vで測定した〜1.8Ωの低いターンオン抵抗と〜1.8 nAの信頼性の高いリーク電流で動作するため、2.5 V / 3.3 VCMOSでのESD保護に適していることも示されています。プロセス。さらに、提案されたデバイスのトリガーメカニズムと伝導特性が調査され、TCADシミュレーションで実証されました。

背景

半導体デバイスの機能サイズの継続的な小型化に伴い、集積回路(IC)の静電放電(ESD)によって引き起こされる損傷がより深刻な問題になっています。さらに、ESD保護デバイスの製造コストは、高度なプロセス技術によって大幅に増加しています[1]。したがって、高面積効率と堅牢性のESD保護デバイスの設計は非常に価値があります。

シリコン制御整流子(SCR)デバイスは、その寄生バイポーラ接合トランジスタの強い正のフィードバック効果により、小さなデバイス寸法で高いESD電流を維持することが検証されました[2]。ただし、SCRのトリガー電圧は通常高い( V t1 )これは、ナノスケールCMOS技術の入力段のゲート酸化物絶縁破壊電圧を超えています。 V を減らすには t1 SCRの中で、高濃度にドープされたn + を挿入することにより、入力ESD保護について修正されたラテラルSCR(MLSCR)が報告されました。 またはp + nウェルとpウェルの境界を越えた領域[3、4]。ただし、MLSCRのトリガー電圧は、CMOS出力バッファー内の出力トランジスタのブレークダウン電圧よりも高いままです。したがって、効率的な出力ESD保護だけを提供することはできません。

CMOS出力バッファを効率的に保護するために、従来のSCRに短チャネルNMOS(PMOS)デバイスを挿入して、はるかに低いトリガー電圧を実現することにより、低電圧トリガーSCR(LVTSCR)が提案されています[5、6、7]。 、挿入されたNMOS(PMOS)デバイスのスナップバックトリガー電圧に相当します。ただし、従来のSCRおよびMLSCRデバイスと同様に、LVTSCRも、保持電圧(V h )が非常に低いため、ラッチアップの危険性があります。 )約2 V [8]。このようなラッチアップ効果により、通常の動作中に誤動作が発生し、ICを破壊するための絶え間ない大電流が発生します[9]。

V を改善するためのいくつかの可能な方法があります h LVTSCRの[10,11,12,13,14,15]。最も一般的な解決策は、SCRの寄生バイポーラ接合トランジスタ(BJT)のベース領域を拡張して、エミッタ-ベース接合の注入効率を下げることです[10]。このソリューションを採用すると、デバイスのレイアウト領域が増えるだけでなく、ターンオン抵抗( R )も増加します。 on )も必要です。これにより、故障電流( I )がさらに大幅に低下します。 t2 )。次に、 I の犠牲を少なくして、LVTSCRにフローティングnウェル領域を挿入することにより、最適化された方法を提案しました。 t2 [11]ですが、大きな R でも動作します on 小さな電流に対してゲート酸化物のブレークダウン電圧を超える法外な導通電圧を導き、その結果、その実効ESD保護電流を減少させます。 LVTSCRに追加のN-LDD / P-HALOレイヤーを追加する方法でも、 V を上げることができます。 h [12]一方、このようなデバイスは特定のプロセスとのみ互換性があり、通常のCMOSプロセスで広く使用することはできません。さらに、ゲートからグランドへのNMOSトリガーLVTSCR(GGSCR)が[13]で報告されており、これにより V が増加します。 h 埋め込まれたNMOSのドレインをアノードに導くことによって、しかしそれは、低電流でのSCR導通の前に埋め込まれたNMOSを損傷させる可能性があります。最近、低い V を実行する複合LVTSCR構造 t1 高い V h [14、15]で実証されました。これらの複合構造は、高度な複雑さと面積要件で設計されているため、設計コストを考慮すると、高度なCMOSテクノロジでのアプリケーションが制限されます。したがって、高度なプロセスのESD保護では、堅牢で面積効率が高く、ラッチアップに強いESD保護デバイスが非常に望まれます。

この論文では、PMOSトランジスタが組み込まれた新しいLVTSCR構造(EP-LVTSCR)を、2.5 V / 3.3Vの供給電圧アプリケーション向けに提案します。提案されたデバイスは28nm CMOSプロセスで製造され、その電気的特性は伝送ラインパルス(TLP)の測定によって検証されます。提案されたデバイスの物理メカニズムは、テクノロジーコンピュータ支援設計(TCAD)シミュレーションによって調査されます。結果として、提案された構造は、より高い保持電圧、より低いトリガー電圧、より低い R を有する。 on 、および I のわずかな減少 t2 余分なプロセスステップなしで。

メソッド

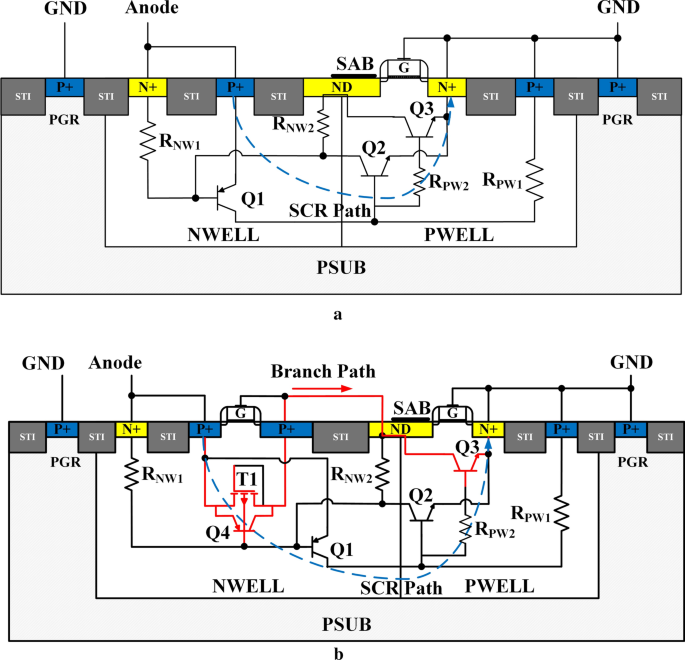

従来のLVTSCRと提案されたEP-LVTSCRがこの論文で研究された。従来のLVTSCRとEP-LVTSCRの概略断面図をそれぞれ図1a、bに示しますが、それらの等価回路は寄生トランジスタとウェル抵抗を備えた構造内に示されています。どちらのデバイスでも、部分的なND領域の上部にケイ化物ブロック(SAB)層が配置され、ケイ化物層の形成を防ぐことでバラスト抵抗を誘導します[16、17]。従来のLVTSCRでは、NMOSトランジスタはPWELLに挿入され、そのドレイン(ND)はNWELLとPWELLの間に設定され、ソースとゲートは一緒にグランド(GND)に接続されます(図1aを参照)。 ESDストレスの間、寄生横方向p-n-p BJT(Q1)と寄生横方向n-p-n BJT(Q2およびQ3)が徐々にオンになります。このような状態では、Q1トランジスタとQ2トランジスタが結合して、電流放電を支配するSCR伝導経路を構成します。ここで、SCR伝導経路は破線で示されています。

a の断面図 従来のLVTSCRと b 提案されたEP-LVTSCR

従来のLVTSCRと比較すると、EP-LVTSCRのゲートとドレインは金属でNDに接続されているため、NWELLに追加のPMOSトランジスタ(T1)が埋め込まれています(図1bを参照)。 EP-LVTSCRのアノードにESDパルスが印加されると、ザッピング電圧がN + / PWELLブレークダウン電圧よりも高い場合、逆バイアスされたN + / NWELL / N + / PWELL / P +ダイオードが最初に導通します。次に、アバランシェ乗数効果によって生成された正孔/電子がカソード/アノードに向かって流れ、NWELL / PWELLの電流密度が増加し、NWELL / PWELL全体の降下電位がさらに上昇します。 R での総電圧降下が1回 NW1 および R NW2 、これはソースとゲート間の電圧降下に相当します(− V gs )T1の、そのしきい値電圧( V th )約0.9 Vの場合、T1がオンになります。続いて、寄生横方向n–p–nトランジスタQ2およびQ3は、それらのエミッタ-ベース接合の導通に依存してトリガーされます。 T1を実行すると、 R が低下することに注意してください。 on NWELLの両端にあるため、Q2とQ3はより低い電圧でトリガーできます。電流が増加し続けると、 R の電圧降下が発生します NW1 約0.7Vに上昇し、Q1とPMOS(Q4)の寄生横方向p–n–pトランジスタをオンにします。最後に、SCRパスが分岐パスの導通に対してオンになります。

いくつかの報告によると、SCRの保持電圧は、主にNWELL / PWELL空乏領域 V の電位差によって決定されます。 dep [18,19,20]、これは空乏領域に注入された少数キャリア(電子/正孔)に反比例します。 EP-LVTSCRの分岐パスは、SCRパスから空乏領域に注入された正孔/電子を抽出できるため、 V が上昇します。 h EP-LVTSCRの。

EP-LVTSCRの物理メカニズムをさらに実証するために、TCADシミュレーションが実行されました。ここでは、移動度、再結合、熱力学、有効固有密度などの物理モデルが統合され、外挿、RelErrcontrol、直流などの数学的手法が使用されています。計算が使用されました。 EP-LVTSCRと従来のLVTSCRのアノードには、立ち上がり時間が10nsの1.2AパルスによるESD電流モデリングがそれぞれ適用され、デバイスの基板が唯一のヒートシンクと見なされ、周囲温度が300に設定されました。 K。

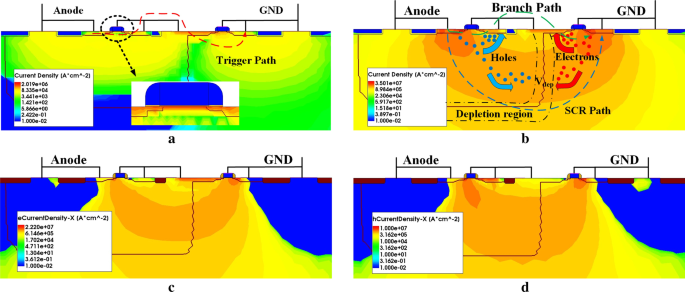

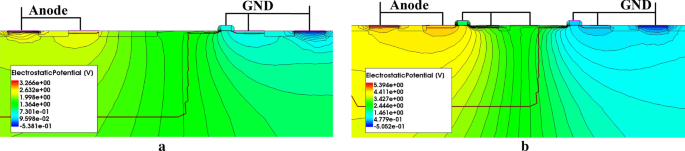

500psと5nsでのEP-LVTSCRの総電流密度分布のシミュレーション結果をそれぞれ図2a、bに示します。 500 psでは、電流密度分布はT1トランジスタとQ2トランジスタに集中します。これは、図2aに示すように、シリーズT1 / Q2がトリガーパスとしてオンになったことを示しています。時間が5nsに達すると、図2bに示すように、SCRパスと分岐パスの両方が導通しています。このとき、P + / N +によって生成された正孔/電子の一部がNWELL / PWELLから抽出され、分岐パスを流れます。これは、図2c、dに示す提案された構造の水平正孔と電子電流密度によって示されます。 。さらに、5 nsでの従来のLVTSCRとEP-LVTSCRの静電ポテンシャル分布を図3a、bで比較します。明らかに、EP-LVTSCR内の潜在的なピークはより高くなっています。これらのシミュレーション結果は、図1bに示されている分岐経路に起因するEP-LVTSCRのより高い保持電圧の上記の仮定の直接的な証拠を提供します。

TCADでシミュレートされた a t での総電流密度分布 =500 ps、 b 5 nsでの総電流密度分布、 c 5nsおよび d での水平電子電流密度分布 1.2A-TLPストレス下で提案されたEP-LVTSCRの5nsでの水平ホール電流密度分布

TCADでシミュレートされた a の静電ポテンシャル分布 提案されたEP-LVTSCRと b t での従来のLVTSCR =1.2A-TLPストレス下で5ns

結果と考察

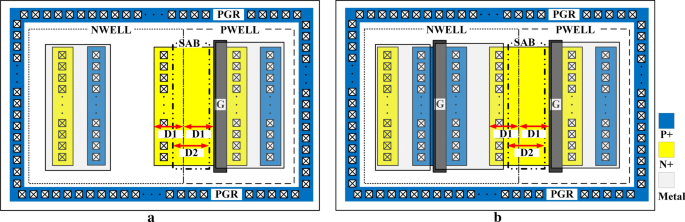

従来のLVTSCRとEP-LVTSCRは、同じ幅40umの28nm 2.5 V / 3.3 VロジックCMOSプロセスで実装されており、それらのレイアウトトポロジをそれぞれ図4a、bに示します。基板に関連する寄生効果を回避するために、両方の構造でP型ガードリング(PGR)が採用されており、各PGRはGNDに接続されています[21]。 NDの中央車軸はNWELL / PWELLジャンクションと位置合わせされており、パラメーターD1はNDの長さの半分を表すために使用され、D2はSAB領域の長さです。

a のレイアウトトポロジ 従来のLVTSCRと b 提案されたEP-LVTSCR

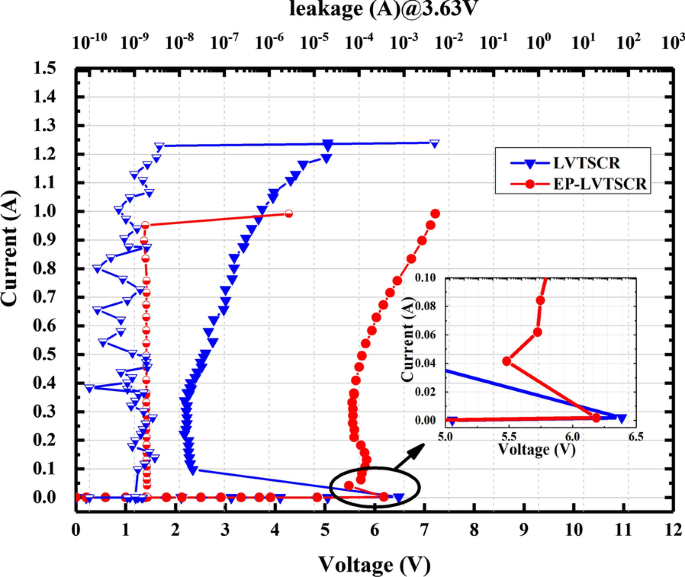

従来のLVTSCRおよびEP-LVTSCRのESD特性は、Hanwa TED-T5000TLPテスターを使用して立ち上がり時間10ns、パルス幅100 nsで測定し、リーク電流は、それぞれの後に3.63 V(1.1 * VDD)DC電圧バイアスで測定しました。 TLPストレス。測定されたTLPI–Vと、EP-LVTSCRおよびLVTSCRのリーク特性を図5に示します。明らかに、EP-LVTSCRはより高い V を持っています。 h 従来のLVTSCRの2.18Vと比較して5.49Vです。EP-LVTSCRは保持電圧が大幅に向上していますが、その I t2 約0.29A減少しました。これは、分岐電流パスのアシスタントの恩恵を受けています。さらに、EP-LVTSCRは V も実行します t1 6.49から6.18Vに減少します。28nmCMOSプロセスの2.5Vまたは3.3V IOピンの場合、ESD設計ウィンドウは10%の安全マージンを考慮して3.63から9.4Vの範囲でした。したがって、提案されたEP-LVTSCRは、従来のLVTSCRタイプの構造でのラッチアップの問題を克服することにより、2.5 V / 3.3 VIOポートの有効なESD保護ソリューションとして使用できます。

EP-LVTSCRと同じダイ面積の従来のLVTSCRの測定されたTLPI–Vおよびリーク電流

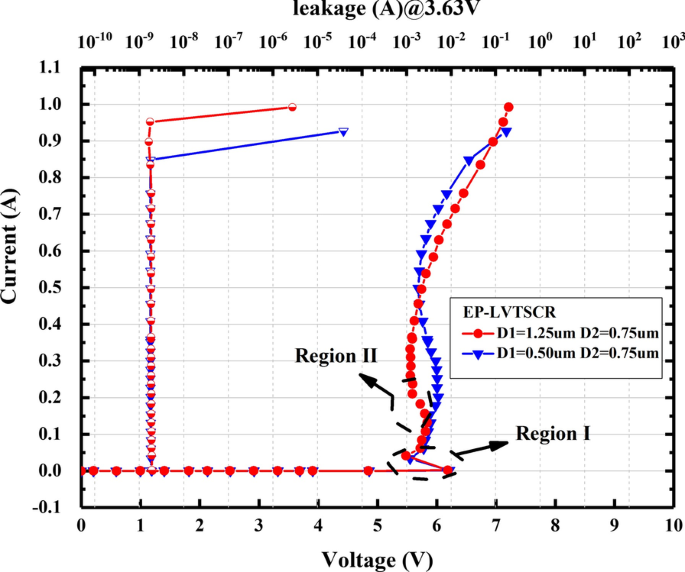

この記事では、提案されたESD保護の電気的特性は、設計変数D1およびD2を変更することによって最適化されました。図6は、2つの異なるD1を使用したEP-LVTSCRのTLP測定結果を示しています。 EP-LVTSCRのI–V曲線は、デバイスの電源投入時のマルチトリガー効果により、2つのスナップバック領域を示していることに注意してください。最初のスナップバック領域Iは、図2aに示されているトリガーパスの伝導を示唆していますが、領域IIの2番目のスナップバックは、SCRパスのターンオンによって誘導されます。 D1が1.25から0.5umに減少すると、 I t2 約0.1A減少し、2番目のスナップバックの保持電流が約0.17 A増加します。これは、ウェルの抵抗が R であるためです。 NW2 および R PW2 (図1)は、D1が減少すると減少するため、SCRの伝導をトリガーして維持するには、より多くの電流が必要になります。

2つの異なるD1を使用したEP-LVTSCRの測定されたTLPI–Vおよびリーク電流

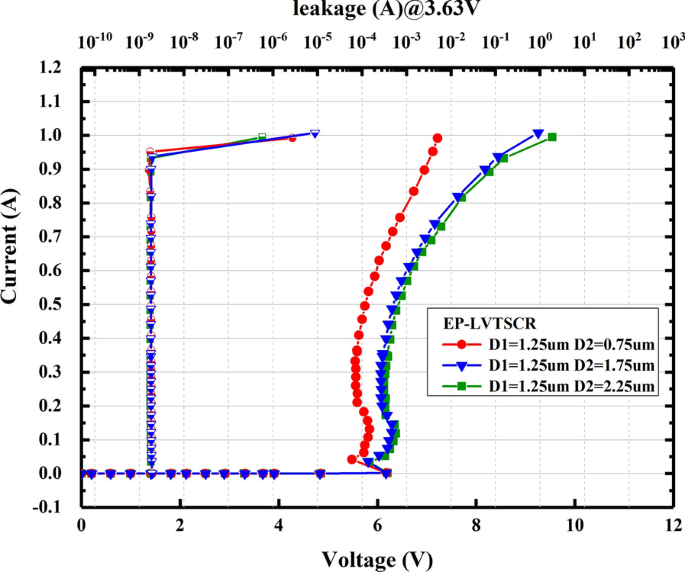

図7は、3つの異なるD2を使用したEP-LVTSCRのTLP I–Vの結果を示しています。 D2が0.75から2.25µmに増加すると、NDのバラスト抵抗が徐々に増加し、分岐パスの抵抗が増加し、 R がさらに拡大します。 on 、これは、図7のIV特性曲線の傾きの変化によって観察できます。その結果、 V h D2が増加し、I t2 に大きな変化がない場合、5.5Vから5.8Vに上昇します。 。

3つの異なるD2を使用したEP-LVTSCRの測定されたTLPI–Vおよびリーク電流

結論

EP-LVTSCRと呼ばれる強化されたESDデバイスは、28 nmCMOSテクノロジで設計および製造されています。提案されたデバイスのメカニズムは、TCADシミュレーションでも実証されました。従来のLVTSCRと比較して、提案されたEP-LVTSCRは、トリガーメカニズムと分岐伝導効果が改善されているため、6.2 Vの低いトリガー電圧と、5.5Vの大幅に高い保持電圧を備えています。 V のこのような高い増加で h 、EP-LVTSCRの故障電流は約20%しか減少しませんでした。さらに、提案された構造は、ターンオン抵抗が低く、3.63Vの電圧で約2nAの信頼性の高いリーク電流で動作するため、2.5 V / 3.3 V I / Oピンの保護に非常に適しています。さらに、EP-LVTSCRは、調整可能な保持電圧特性の恩恵を受けて、5V電源回路にESD保護を提供することも期待されています。

データと資料の可用性

この調査中に生成または分析されたすべてのデータは、この公開された記事に含まれています。

略語

- ESD:

-

静電放電

- SCR:

-

シリコン制御整流子

- MLSCR:

-

修正された横方向SCR

- LVTSCR:

-

低電圧トリガーSCR

- CMOS:

-

相補型金属酸化膜半導体

- IC:

-

集積回路

- V t1 :

-

トリガー電圧

- V h :

-

保持電圧

- BJT:

-

バイポーラ接合トランジスタ

- R on :

-

ターンオン抵抗

- I t2 :

-

故障電流

- TLP:

-

伝送線路パルス

- TCAD:

-

テクノロジーコンピュータ支援設計

- SAB:

-

ケイ化物ブロック

- V th :

-

しきい値電圧

- DC:

-

直流

ナノマテリアル

- マイクロコントローラと組み込みシステムのIC技術に関する簡単な説明

- マキシム:DC-DCレギュレータとサージ保護を備えたデュアルIO-Linkトランシーバ

- FPGAを使用した組み込み設計:開発プロセス

- TRS-STAR:価値のある堅牢でファンレスの組み込みシステム

- スリーステートエレクトロクロミックデバイスのディップコーティングプロセスエンジニアリングと性能最適化

- 純粋なCMOSロジックプロセスによる自己抑制抵抗スイッチング負荷を備えたRRAM統合4TSRAM

- 光起電デバイス用の反射防止および超疎水性特性を備えた新しいナノコーンクラスター微細構造

- テラヘルツ範囲での吸収と偏光変換の切り替え可能な機能を備えた多機能デバイス

- インメモリアプリケーションを計算するための低動作電圧の原子層堆積HfAlOxベースのRRAM

- 自動化とサイバーセキュリティ:顧客の完全な保護

- PCB材料と高電圧用の設計