NORゲートS-Rラッチ

部品と材料

- 4001クワッドNORゲート(Radio Shackカタログ番号276-2401)

- 8ポジションDIPスイッチ(Radio Shackカタログ番号275-1301)

- 10セグメント棒グラフLED(Radio Shackカタログ番号276-081)

- 6ボルトのバッテリー1個

- 2つの10kΩ抵抗器

- 2つの470Ω抵抗器

- 2つの100Ω抵抗器

注意! 4001 ICはCMOSであるため、静電気に敏感です!

相互参照

電気回路の教訓 、第4巻、第3章:「論理ゲート」

電気回路の教訓 、第4巻、第10章:「マルチバイブレータ」

学習目標

- デジタル回路における正のフィードバックの効果を学ぶために

- ラッチ回路の「無効な」状態とはどういう意味ですか

- どのような競合状態 デジタル回路にあります

- 有効な「高い」CMOS信号電圧レベルの重要性を知るため

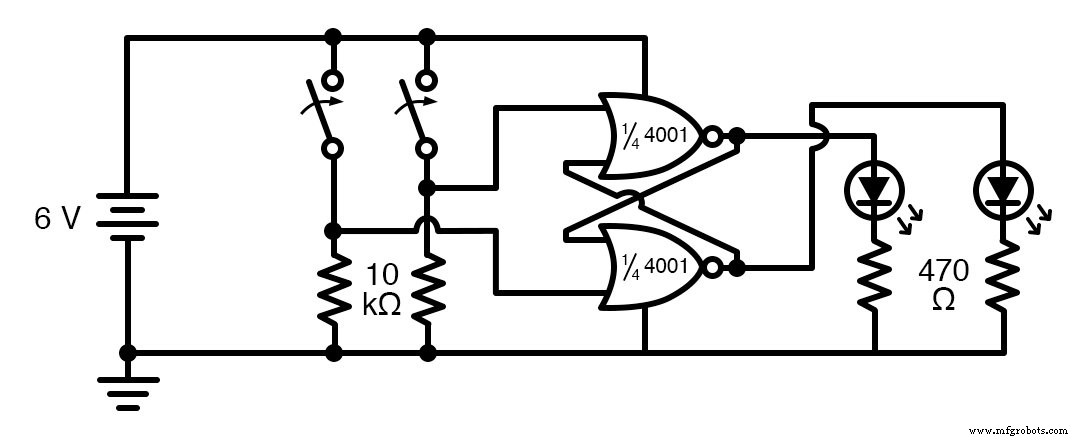

回路図

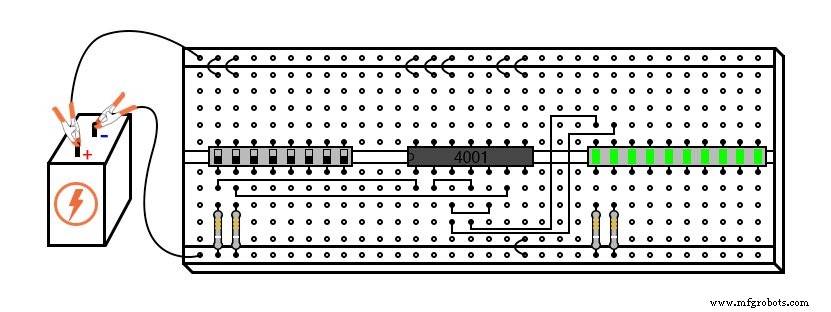

イラスト

手順

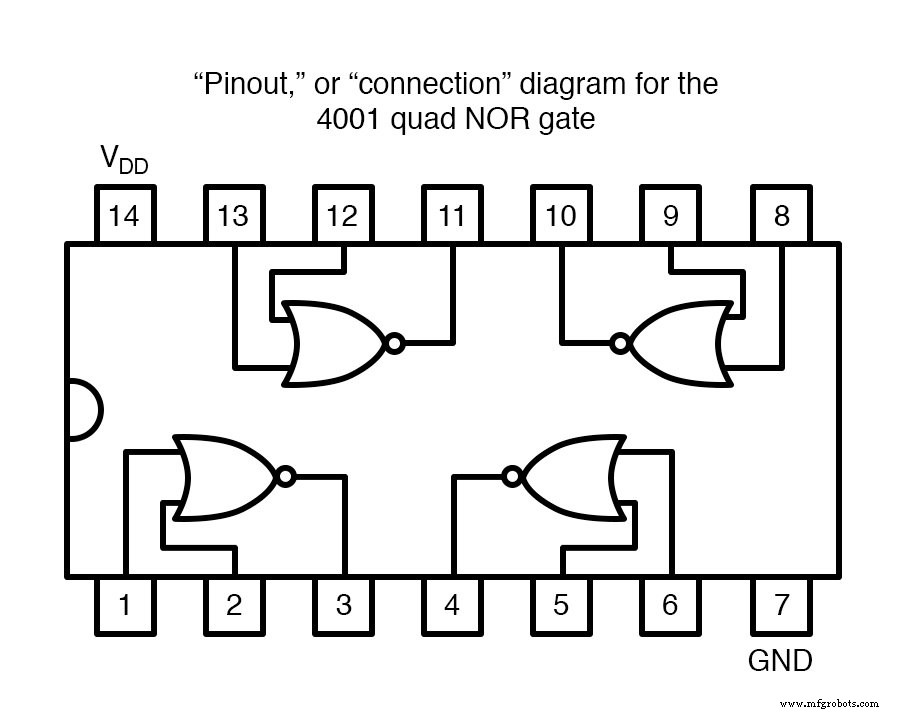

4001集積回路はCMOSクワッドNORゲートであり、入力、出力、および電源ピンの割り当てが4011クワッドNANDゲートと同じです。その「ピン配置」または「接続」図は次のとおりです。

回路図に示すように2つのNORゲートが相互接続されている場合、出力から入力への正のフィードバックがあります。つまり、出力信号はゲートを最後の出力状態に維持する傾向があります。オペアンプ回路の場合と同様に、正のフィードバックはヒステリシスを作成します 。

回路が最後の出力状態のままになるこの傾向は、回路に一種の「メモリ」を与えます。実際、このような回路に基づくソリッドステートコンピュータメモリテクノロジーがあります!

左側のスイッチを「セット」入力、右側のスイッチを「リセット」と指定すると、左側のLEDが「Q」出力になり、右側のLEDが「Q-not」出力になります。セット入力を「ハイ」(スイッチオン)、リセット入力を「ロー」にすると、Qは「ハイ」になり、Q-notは「ロー」になります。

これはセットとして知られています 回路の状態。リセット入力を「ハイ」にし、セット入力を「ロー」にすると、ラッチ回路の出力状態が反転します。Qは「ロー」で、Qは「ハイ」ではありません。これはリセットとして知られています 回路の状態。両方の入力が「ロー」状態になると、回路のQおよびQ-not出力は最後の状態のままになり、以前の設定を「記憶」します。これはラッチとして知られています 回路の状態。

出力は「Q」および「Q-not」と指定されているため、それらの状態は常に相補的(反対)になることを意味します。したがって、何かが起こった場合、両方の出力が同じに強制されます。 状態では、回路のそのモードを「無効」と呼ぶ傾向があります。

これは、Set入力とReset入力の両方を「ハイ」にした場合に発生することです。QとQ-not出力の両方が同じ「ロー」ロジック状態に強制されます。これは無効として知られています または違法 回路の状態。問題が発生したためではなく、出力がラベルで確立された期待に応えられなかったためです。

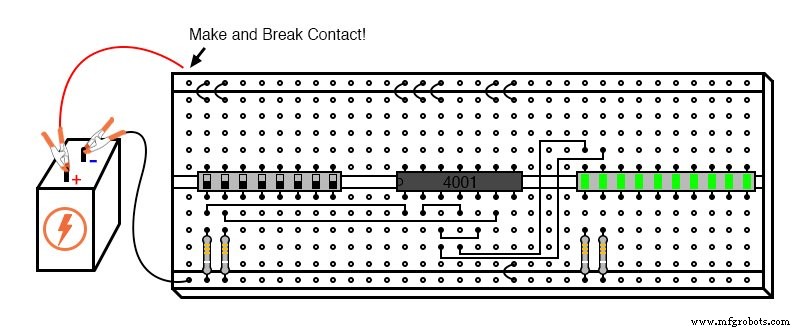

「ラッチ」状態は、最後の出力状態が「記憶」されるヒステリシス状態であるため、前の状態を保持せずに、回路がこのようにパワーアップするとどうなるか疑問に思うかもしれません。 。実験するには、両方のスイッチをオフの位置に置き、セット入力とリセット入力の両方をローにしてから、バッテリーワイヤーの1つをブレッドボードから外します。

次に、そのバッテリーワイヤーとブレッドボード上の適切な接続ポイントをすばやく接続して切断し、回路の電源が何度もオンになるときの2つのLEDのステータスを確認します。

このようなラッチ回路が「ラッチ」状態にパワーアップされると、ゲートは制御のために互いに競合します。 「ロー」入力が与えられると、両方のゲートが「ハイ」信号を出力しようとします。一方のゲートがもう一方のゲートよりも先に「ハイ」出力状態に達すると、その「ハイ」状態がもう一方のゲートの入力にフィードバックされ、出力が「ロー」になり、より速いゲートがレースに勝ちます。

常に、チップ内のゲート間の内部変動、および/または一方のゲートを他方よりも遅延させるように作用する外部抵抗および静電容量のために、一方のゲートが競争に勝ちます。これが通常意味することは、回路が同じモードで何度も何度もパワーアップする傾向があるということです。ただし、電源投入/非電源投入のサイクルを継続している場合は、少なくとも数回、ラッチ回路が反対側でラッチされて電源が入るのを確認する必要があります。 通常の状態から。

競合状態は、予測できない動作につながるため、どのような種類のシステムでも一般的に望ましくありません。この実験が示すように、それらが作成する予測不可能性のために、それらを見つけるのは特に面倒な場合があります。たとえば、2つのNORゲートの1つが、チップの欠陥のために非常に低速で動作するシナリオを想像してみてください。

このハンディキャップにより、もう一方のゲートが毎回パワーアップレースに勝つことになります。言い換えると、両方の入力が「ロー」の電源投入時に、回路は非常に予測可能になります。ただし、通常とは異なるチップを、ゲートがより均等に一致するチップ、またはその他のチップに交換するとします。 NORゲートは一貫して遅くなりました。

コンポーネントを交換しても通常の回路動作は変わらないはずですが、競合状態が存在する場合は、コンポーネントを変更することでそれがうまくいく可能性があります。

SRラッチには固有のレース傾向があるため、一貫した電源投入状態を期待して回路を設計するのではなく、外部手段を使用してレースを「強制」し、目的のゲートが常に「勝つ」ようにする必要があります。

この回路で試す興味深い変更は、470ΩのLED「ドロップ」抵抗の1つを100Ωなどのより低い値のユニットに置き換えることです。この変更の明らかな効果は、より多くの電流が流れるため、LEDの明るさが増すことになります。

それほど明白ではない効果も生じます、そしてそれは大きな学習価値を保持するこの効果です。 470Ωの抵抗の1つを100Ωの抵抗に交換し、回路の動作に注意して、4つの可能な設定の組み合わせすべてを介して入力信号スイッチを操作してみてください。

回路は、入力スイッチが両方とも「ロー」に設定されている場合(「ラッチ」モード)、一方の状態(セットまたはリセット)ではラッチを拒否しますが、もう一方の状態でのみラッチすることに注意してください。どうしてこれなの?電圧計を取り、両方の入力が「低」のときに出力が「高」であるゲートの出力電圧を測定します。

この電圧表示に注意してから、 other 状態(リセットまたはセット)が強制され、出力が「ハイ」のときにもう一方のゲートの出力電圧を測定します。 2つのゲート出力電圧レベルの違いに注意してください。一方のゲートには470Ωの抵抗を備えたLEDが搭載され、もう一方のゲートには100Ωの抵抗を備えたLEDが搭載されています。

「より重い」負荷(100Ω抵抗)によって負荷がかけられたものははるかに少なくなります。この電圧よりはるかに低い電圧は、フィードバックされるときに他のNORゲートの入力によって「高」信号としてまったく解釈されません。すべての論理ゲートには、許容される「高」および「低」入力信号電圧範囲があり、デジタル信号の電圧がこの許容範囲外にある場合、受信ゲートによって適切に解釈されない可能性があります。

このようなラッチ回路では、一方のゲートの出力からもう一方のゲートの入力にフィードバックされる安定した「ハイ」信号に依存しますが、「ウィーク」信号は、回路はその状態の1つでラッチされました。

これが、「ハイ」ライトと「ロー」ライトを備えた実際のロジックプローブではなく、デジタル信号レベルを決定するためのロジック「プローブ」として電圧計を使用することを好む理由の1つです。論理プローブは「弱い」信号の存在を示さない場合がありますが、電圧計はその定量的表示によって確実に示されます。

このタイプの問題は、集積回路のさまざまな「ファミリ」が混在する回路(TTLとCMOSなど)で一般的であり、信号レベルの定量的測定を提供するテスト機器でのみ見つけることができます。

産業技術