シフトレジスタ:パラレル入力、シリアル出力(PISO)変換

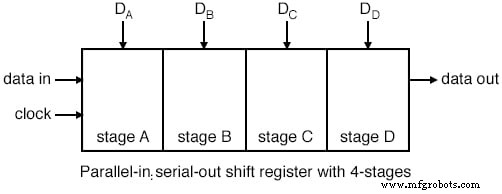

パラレル入力/シリアル出力シフトレジスタは、以前のシリアル入力/シリアル出力シフトレジスタが行うすべてのことと、すべてのステージへの入力データを同時に実行します。

パラレル入力/シリアル出力シフトレジスタは、データを格納し、クロックごとにデータをシフトし、ステージ数にクロック周期を掛けた分だけ遅延させます。

さらに、パラレル入力/シリアル出力は、シフトが始まる前にすべてのステージにデータを並列にロードできることを意味します。

これは、パラレルからデータを変換する方法です。 シリアルにフォーマットする フォーマット。パラレルフォーマットとは、以下に示すように、データビットがデータビットごとに1つずつ、個々のワイヤに同時に存在することを意味します。

シリアルフォーマットとは、下のブロック図の「データ出力」の場合のように、データビットが単一のワイヤまたは回路上で時間的に順番に表示されることを意味します。

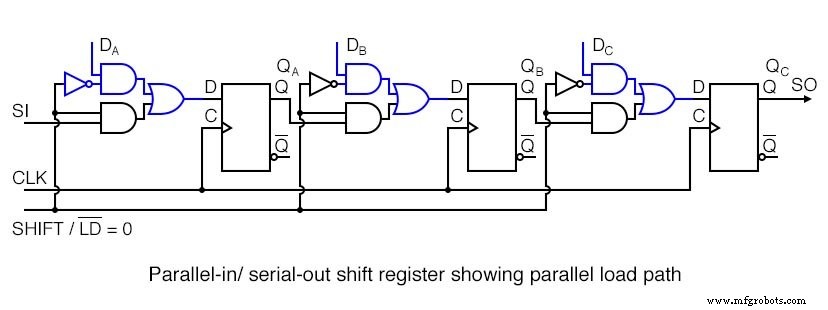

以下では、3ステージのパラレル入力/シリアル出力シフトレジスタの内部の詳細を詳しく見ていきます。

ステージはタイプ D で構成されます ストレージ用のフリップフロップ、およびデータを並列にロードするか、保存されたデータを右にシフトするかを決定するためのAND-ORセレクター。

一般に、これらの要素は、必要なステージ数だけ複製されます。スペースの制限により、3つのステージを示しています。

実際の部品では、4、8、または16ビットが正常です。

上に、SHIFT / LD ’がロジックローの場合の並列ロードパスを示します。 D A にサービスを提供する上部NANDゲート D B D C が有効になり、タイプ D のD入力にデータが渡されます ビーチサンダルQ A Q B D C それぞれ。

次の正方向のクロックエッジで、データは3つのFFのDからQにクロックされます。 3ビットのデータがQ A にロードされます Q B D C 同時に。

クロックパルスでデータがロードされる、今説明した並列ロードのタイプは、同期ロードとして知られています。 データの読み込みが時計に同期しているためです。

これは、非同期ロードと区別する必要があります ここで、ロードは、クロックを必要としないフリップフロップのプリセットピンとクリアピンによって制御されます。

これらのロード方法の1つだけが個々のデバイス内で使用され、同期ロードは新しいデバイスでより一般的です。

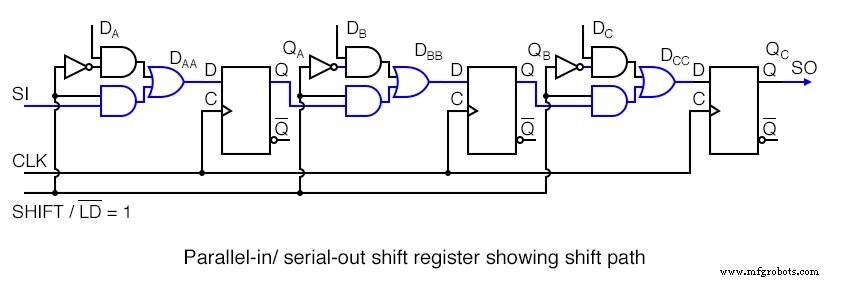

SHIFT / LD ’がロジックハイの場合のシフトパスを上に示します。 ORゲートに給電するペアの下位ANDゲートが有効になり、SIからD A へのシフトレジスタ接続が可能になります。 、Q A D B へ 、Q B D C へ 、Q C SOに。クロックパルスにより、データは連続するパルスでSOに右シフトアウトされます。

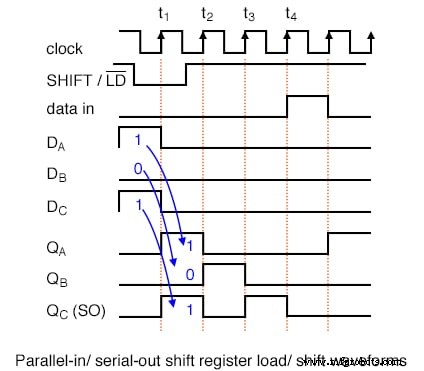

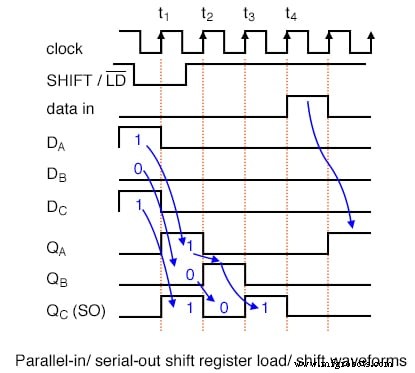

以下の波形は、3ビットのデータの並列ロードとこのデータのシリアルシフトの両方を示しています。 D A でのパラレルデータ D B D C SOでシリアルデータに変換されます。

以前に並列ロードとシフトの言葉で説明したことは、上記の波形として設定されています。

例として、 101 を紹介します。 並列入力へD AA D BB D CC 。次に、SHIFT / LDが低くなり、データのシフトではなくデータのロードが可能になります。

セットアップとホールドの要件により、クロックパルスの前後の短時間はローにする必要があります。必要以上に幅が広いです。

ただし、同期ロジックでは、幅を広くするのが便利です。アクティブなローSHIFT / LDをほぼ2クロック幅にし、t 1 のほぼ1クロック前にローにすることもできます。 t 3 の直前にハイに戻ります 。

重要な要素は、クロック時間t 1 の前後で低くする必要があるということです。 クロックによるデータの並列ロードを有効にします。

t 1 に注意してください データ 101 D A で D B D C Q A に示すように、フリップフロップのDからQまでクロックされます。 Q B Q C 時間t 1 。

これは、クロックと同期したデータの並列ロードです。

データがロードされたので、シフトを有効にするためにSHIFT / LD ’が高い場合は、データをシフトできます。これは、t 2 より前です。 。

t 2 で データ 0 Q C で Q C と同じSOからシフトアウトされます 波形。別の集積回路にシフトされるか、SOに接続されていない場合は失われます。

Q B のデータ 、 0 Q C にシフトされます 。 1 Q A で Q B にシフトされます 。 「データ入力」を使用して 0 、Q A 0 になります 。 t 2 の後 、Q A Q B Q C = 010 。

t 3 の後 、Q A Q B Q C = 001 。この 1 、元々Q A に存在していた t 1 の後 、現在SOおよびQ C に存在します 。

最後のデータビットは、存在する場合は外部集積回路にシフトアウトされます。 t 4 の後 並列ロードからのすべてのデータが失われます。

クロックt 5 データのシフトインを示します 1 SI、シリアル入力に存在します。

Q:シフトレジスタにSIピンとSOピンを提供するのはなぜですか?

A:これらの接続により、シフトレジスタステージをカスケード接続して、単一のIC(集積回路)パッケージで利用できるよりも大きなシフターを提供できます。また、マイクロプロセッサなどの他のICとのシリアル接続も可能です。

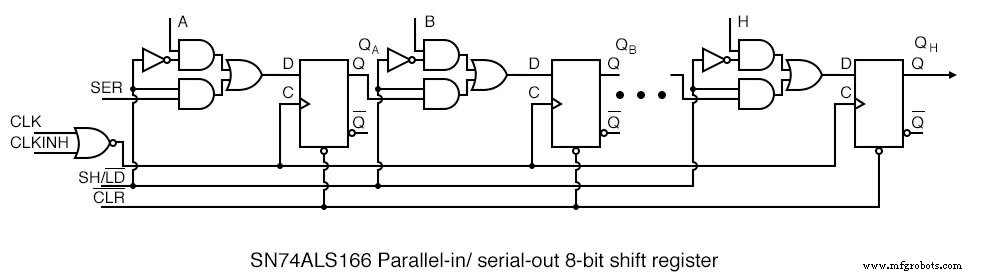

Texas Instrumentsの厚意により、集積回路として利用可能なパラレル入力/シリアル出力シフトレジスタを詳しく見てみましょう。

完全なデバイスデータシートについては、これらのリンクをたどってください。

パラレルイン/シリアルアウトデバイス

- SN74ALS166パラレル入力/シリアル出力8ビットシフトレジスタ、同期負荷

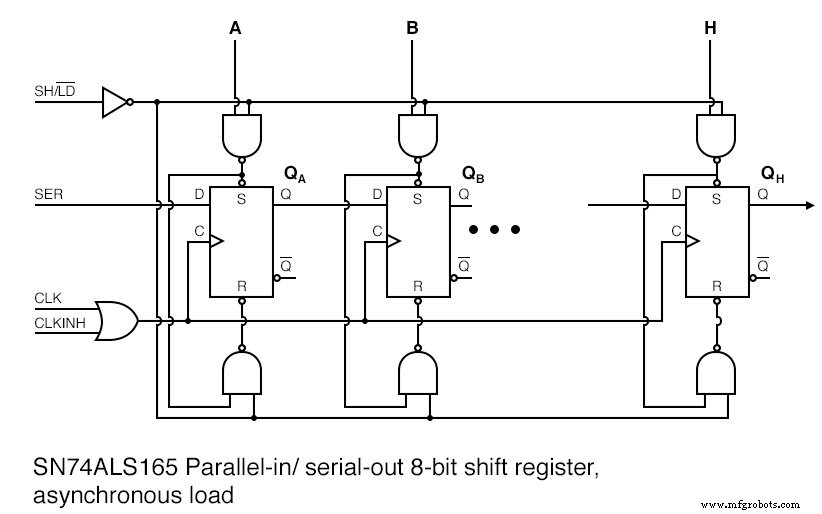

- SN74ALS165パラレル入力/シリアル出力8ビットシフトレジスタ、非同期ロード

- CD4014Bパラレル入力/シリアル出力8ビットシフトレジスタ、同期負荷

- SN74LS647パラレル入力/シリアル出力16ビットシフトレジスタ、同期負荷

上に示したSN74ALS166は、実際の部品が以前のパラレルイン/シリアルアウトシフターの図に最も近いものです。

上記の図の小さな変更に注意してください。まず、8段階あります。 3つだけ表示します。

すべての8ステージは、上記のリンクから入手できるデータシートに示されています。メーカーは、データ入力A、B、CなどにHのラベルを付けます。

SHIFT / LOADコントロールはSH / LD ’と呼ばれます。以前の用語から省略されていますが、同じように機能します。低い場合は並列負荷、高い場合はシフトします。

シフト入力(シリアルデータ入力)は、SIではなくALS166のSERです。クロックCLKは、禁止信号CLKINHによって制御されます。

CLKINHがハイの場合、クロックは禁止または無効になります。それ以外の点では、この「実際の部分」は、詳細に調べたものと同じです。

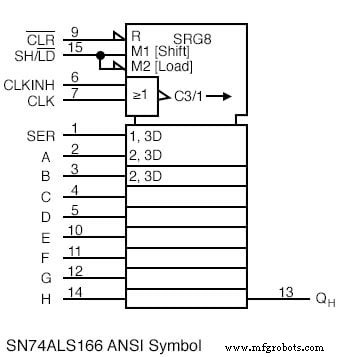

上記は、データシートに記載されているSN74ALS166のANSI(米国規格協会)の記号です。

パーツがどのように動作するかがわかれば、シンボル内の詳細を非表示にすると便利です。シンボルには多くの一般的な形式があります。

ANSIシンボルの利点は、ラベルが部品の動作に関するヒントを提供することです。

‘74ASL166の上部にある大きなノッチ付きブロックは、ANSIシンボルの制御セクションです。 R によって起訴されたリセットがあります 。

3つの制御信号があります: M1 (シフト)、 M2 (ロード)、および C3 / 1(矢印) (禁止時計)。時計には2つの機能があります。

まず、 C3 プレフィックス3が表示される場合は常にパラレルデータをシフトします。第二に、 M1 1 で示されるように、がアサートされます C3 / 1(矢印) 、データは右向きの矢印で示されているようにシフトされます。

スラッシュ(/)は、これら2つの関数の間の区切り文字です。タイトル SRG8 で示される8シフトステージ 、外部入力 A、B、C、によって識別されます H へ 。

内部の 2、3D そのデータを示します、 D 、 M2 によって制御されます [読み込み]と C3 時計。この場合、パラレルデータはクロック C3 と同期してロードされていると結論付けることができます。 。

A の上段 入力 SER に対応するために、他のブロックよりも幅の広いブロックです。 。

伝説の 1、3D SER M1 によって制御されます [Shift]と C3 時計。したがって、 SER でデータをクロックインすることを期待しています。 並列ロードではなくシフトする場合。

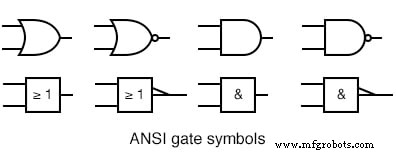

ANSI / IEEE基本ゲート長方形記号 よく知られている形状記号と比較するために、上記で提供されています。 CLKIN に関連付けられた記号の意味を解読できるようにするため Hと CLK 以前のANSISN74ALS166シンボルのピン。

CLK およびCLKINHはまたはをフィードします SN74ALS166ANSIシンボルのゲート。 または => で示されます 長方形のはめ込み記号。

出力の長い三角形はクロックを示します。矢印の付いたバブルがあった場合、これはクロックの負のエッジ(高から低)のシフトを示しているはずです。

クロック矢印の付いたバブルがないため、レジスタはクロックの正のエッジ(ローからハイへの遷移)でシフトします。

凡例 C3 / 1 の後の長い矢印 右向きは、シンボルの下にある右シフトを示します。

SN74ALS165パラレル入力/シリアル出力、非同期ロードシフトレジスタの内部ロジックの一部は、上記のデータシートから再現されています。

完全な図については、このセクションの冒頭にあるリンクを参照してください。これまで、データの非同期読み込みについては検討していません。

まず、ロードはセットに適切な信号を適用することによって行われます。 (プリセット)およびリセット (クリア)フリップフロップの入力。

上部の NAND ゲートはセットにフィードします FFのピンであり、下部の NAND にもカスケード接続されます リセットを供給するゲート FFのピン。

下の NAND ゲートは、セットからの信号を反転します リセットに固定します ピン。

まず、 SH / LD ’ 低を引く必要があります 上部と下部の NAND を有効にします ゲート。

SH / LD ’の場合 論理的に高い 代わりに、ロジックに低を供給するインバーター すべての NAND ゲートは高を強制します アウト、「アクティブロー」セットをリリース およびリセット すべてのFFのピン。

FFをロードする可能性はありません。

SH / LD ’ 低を開催 、たとえば、データ 1 をフィードできます 並列入力へ A 、上部の NAND でゼロに反転します ゲート出力、設定FF Q A 1 に 。

0 セットで ピンは下部の NAND に供給されます 1 に反転されるゲート 、リセットをリリースします Q A のピン 。

したがって、データ A =1 Q A を設定します =1 。これにはクロックが必要ないため、ロードはクロックに対して非同期です。

クロックがデータをパラレルロードするのを待つことができない場合、または単一のクロックパルスを生成するのが不便な場合は、非同期ロードシフトレジスタを使用します。

データのフィードの唯一の違い 0 並列入力へ A 1 に反転するということです セットを解放する上部ゲートから 。

この 1 セットで 0 に反転されます 下のゲートで、リセットを引いて 低に 、 Q A をリセットします =0 。

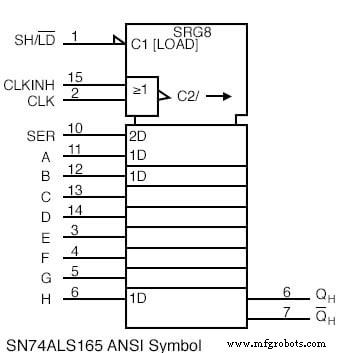

上記のSN74ALS166のANSIシンボルには、2つの内部コントロール C1 があります。 [LOAD]および C2 またはからの時計 ( CLKINH、CLK の機能 。

SRG8 8ステージシフターは言います。 C2 の後の矢印 右または下にシフトすることを示します。 SER 入力は、内部ラベル 2D で示されるクロックの関数です。 。

パラレルデータ入力 A、B、C H へ C1 の機能です [LOAD]、内部ラベル 1D で示されます 。

C1 sh / LD ’=0 のときにアサートされます 入力の半矢印インバーターによるものです。

これを、以前の同期ANSISN75ALS166のクロックによるパラレルデータ入力の制御と比較してください。 ANSIデータラベルの違いに注意してください。

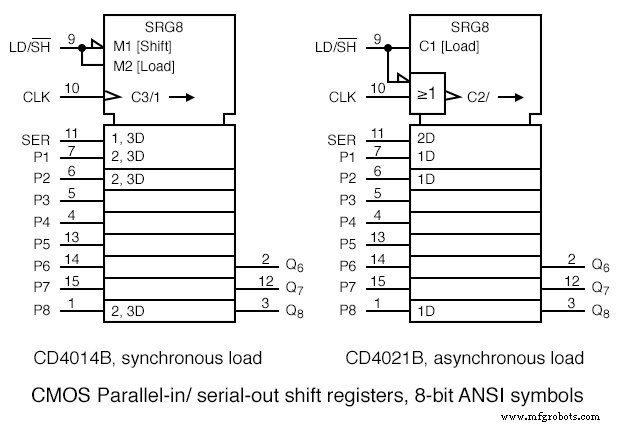

上記のCD4014Bでは、 M1 LD / SH ’=0 のときにアサートされます 。 M2 LD / SH ’=1 のときにアサートされます 。

時計 C3 / 1 2、3D でのデータの並列読み込みに使用されます M2 の場合 2,3 で示されるようにアクティブです プレフィックスラベル。

ピン P3 P7 へ 内部にスマエがあると理解されている 2,3 プレフィックスラベルを P2 および P8 。 SER で 、 1,3D プレフィックスは、 M1 を意味します 時計 C3 シリアルデータを入力するために必要です。

右シフトは、M1がアクティブなときに 1 で示されるように行われます。 C3 / 1矢印 。

CD4021Bは、 2 がないことからわかるように、データの非同期並列ロードを除いて、同様の部分です。 データラベルのプレフィックス 1D ピンP1、P2、P8の場合。

もちろん、プレフィックス 2 ラベル 2D 入力時 SER データがこのピンにクロックインされることを示します。 または ゲートの挿入図は、時計が LD / SH ’によって制御されていることを示しています 。

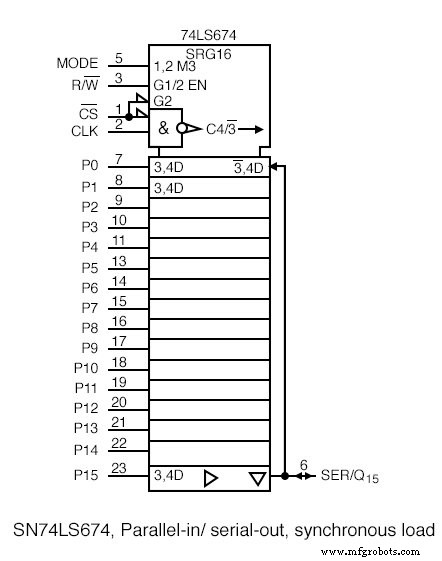

上記のSN74LS674内部ラベル SRG 16 16ビットシフトレジスタを示します。

モード 記号の上部にある制御セクションへの入力には、 1,2 M3 というラベルが付いています。 。内部 M3 入力モードの関数です および G1 および G2 1,2 で示されるように 先行する M3 。

ベースラベル G AND を示します そのような G の機能 入力。 R / W ’を入力します 内部的に G1 / 2 EN のラベルが付いています 。

これは有効化 EN ( G1およびG2 によって制御されます )シンボルの他の場所で使用されるトライステートデバイスの場合。

CS ’ オン(ピン1)は内部 G2 。チップセレクト CS ’ AND でもあります 入力 CLK で編集 内部時計を与えるために C4 。

クロック矢印内のバブルは、アクティビティがクロックの負のエッジ(高から低への遷移)にあることを示します。

スラッシュ(/)は、クロックの2つの機能を意味する区切り文字です。スラッシュの前に、 C4 プレフィックスが 4 のすべてのものの制御を示します 。

スラッシュの後、 3 ’(矢印) シフトを示します。 3 ’ C4 / 3 ’ M3がディアサートされたときにシフトすることを意味します( MODE =0 )。長い矢印は右シフト(下)を示します。

コントロールセクションの下からデータセクションに移動すると、外部入力 P0-P15 があります。 、ピン(7-11、13-23)。

プレフィックス 3,4 内部ラベルの 3,4D M3 と時計 C4 並列データのロードを制御します。

D データの略です。このラベルは、明示的に書き出されていませんが、すべての並列入力に適用されると想定されています。

ラベル 3 ’、4D を見つけます P0 の右側 (pin7)ステージ。補完- 3 M3 =MODE =0 であることを示します 入力(シフト) SER / Q 15 (pin5)時刻、( 4 時計 C4 に対応する3 ’、4D) 。

つまり、 MODE =0 、データを Q 0 にシフトします シリアル入力(ピン6)から。他のすべてのステージは、クロック時に右(下)にシフトします。

シンボルの下部に移動すると、右向きの三角形は Q の間のバッファーを示します と出力ピン。

下向きの三角形は、トライステートデバイスを示します。トライステートはenable EN によって制御されることを以前に述べました 、実際には G1およびG2 コントロールセクションから。

R / W =0 の場合 、トライステートは無効になっており、データを Q 0 にシフトできます。 SER 経由 (ピン6)、上記で省略した詳細。実際には、 MODE =0、R / W ’=0、CS’ =0 が必要です。

SN74LS674の内部ロジックと、制御信号の動作を要約した表は、セクション上部の箇条書きのリンクにあります。

R / W ’=1 の場合 、トライステートが有効になっています、 Q 15 シフトアウト SER / Q 15 (ピン6)そして Q 0 に再循環します 右側のワイヤーを介して 3 ’、4D にステージングします 。

CS ’は低く、クロックC4 / 3’とG2を EN にすると仮定しました。 トライステートが可能です。

実用的なアプリケーション

パラレルイン/シリアルアウトシフトレジスタの用途は、データをマイクロプロセッサに読み込むことです。

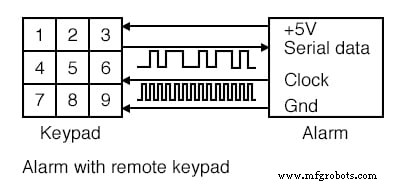

上記のアラームは、リモートキーパッドによって制御されます。アラームボックスは+ 5Vを供給し、リモートキーパッドにアースして電力を供給します。

アラームは、シフトクロックをキーパッドに送信することにより、数十ミリ秒ごとにリモートキーパッドを読み取ります。キーパッドは、パラレルイン/シリアルアウトシフトレジスタを介してキーのステータスを示すシリアルデータを返します。

したがって、4本のワイヤーで9つのキースイッチを読み取ります。 9つのキーのそれぞれに対して回路を実行する必要がある場合、何本のワイヤーが必要になりますか?

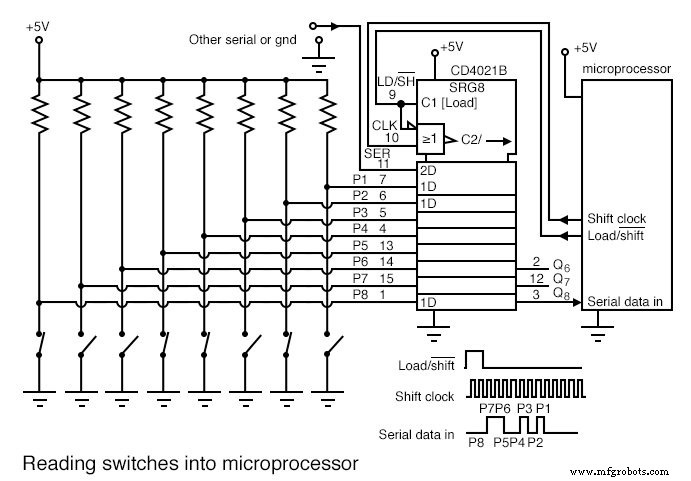

パラレルイン/シリアルアウトシフトレジスタの実際のアプリケーションは、わずか数ピンでマイクロプロセッサに多くのスイッチクロージャを読み込むことです。

一部のローエンドマイクロプロセッサには、8ピンパッケージで使用可能な6-I / O(入力/出力)ピンしかありません。

または、84ピンパッケージのほとんどのピンを使用した可能性があります。回路基板、機械、車両、または建物の周りを走るワイヤーの数を減らしたい場合があります。

これにより、システムの信頼性が向上します。自動車のワイヤーの数を減らしたメーカーは、より信頼性の高い製品を製造していると報告されています。

いずれにせよ、上の図のスイッチから8ビットのデータを読み取るために必要なマイクロプロセッサピンは3つだけです。

単一の並列ロードクロックを生成しなくてもデータのロードを制御する方が簡単なため、非同期ロードデバイスであるCD4021Bを選択しました。

シフトレジスタのパラレルデータ入力は、各入力に抵抗を使用して+ 5Vにプルアップされます。

すべてのスイッチが開いている場合は、すべての 1 sは、マイクロプロセッサが LD / SH ’を移動すると、シフトレジスタにロードされます。 低から高へのライン、そしてシフトを見越して低へ戻る。

スイッチを閉じると、ロジック 0 が適用されます sを対応する並列入力に接続します。 P1-P7のデータパターンは、 LD / SH ’=1 によって並列ロードされます。 マイクロプロセッサソフトウェアによって生成されます。

マイクロプロセッサはシフトパルスを生成し、8ビットごとにデータビットを読み取ります。

このプロセスは完全にソフトウェアで実行される場合もあれば、より大きなマイクロプロセッサに1つ以上のシリアルインターフェイスがあり、ハードウェアでより迅速にタスクを実行する場合もあります。

LD / SH ’=0 の場合 、マイクロプロセッサは 0 を生成します 1 へ シフトクロックラインでの遷移 、次にシリアルデータのデータビットを読み取ります ライン。これはすべての8ビットに対して繰り返されます。

SER より多くのスイッチ接点を読み取る必要がある場合は、シフトレジスタのラインを別の同一のCD4021B回路で駆動できます。

この場合、マイクロプロセッサは16シフトパルスを生成します。多くの場合、このシリアルデータ形式と互換性のある他の何か、たとえば、アナログ-デジタルコンバーター、温度センサー、キーボードスキャナー、シリアル読み取り専用メモリによって駆動されます。

スイッチクロージャーに関しては、それらは、機械のキャリッジ上のリミットスイッチ、過熱センサー、磁気リードスイッチ、ドアまたはウィンドウスイッチ、空気または水圧スイッチ、またはソリッドステート光遮断器である可能性があります。

関連するワークシート:

- シフトレジスタワークシート

産業技術