シフトレジスタ:シリアル入力、シリアル出力

シリアル入力、シリアル出力のシフトレジスタは、ステージごとに1クロック時間ずつデータを遅延させます。

レジスタごとに少しのデータを格納します。シリアル入力、シリアル出力のシフトレジスタの長さは1〜64ビットで、レジスタまたはパッケージがカスケード接続されている場合はさらに長くなります。

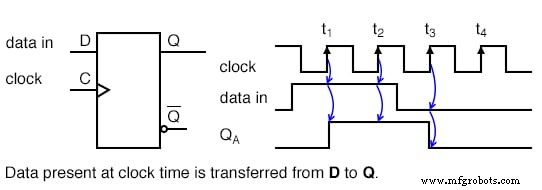

以下は、レジスタクロックに同期されていないデータを受信する単段シフトレジスタです。

D の「データ入力」 タイプ D のピン FF (フリップフロップ)は、クロックがローからハイに変化してもレベルを変更しません。

デジタル論理回路の信頼性を向上させるために、データを回路基板のシステム全体のクロックに同期させたい場合があります。

上に示した(下の図と比較した)明らかなポイントは、 D に「データイン」が存在することです。 タイプ D のピン FFはクロック時にDから出力Qに転送されます。

この例のシフトレジスタはポジティブエッジセンシティブストレージエレメントを使用しているため、出力 Q D に従います 上の図の上矢印で示されているように、クロックがローからハイに遷移するときに入力します。

データはクロックエッジの前後で十分に安定しているため、クロック時にどのロジックレベルが存在するかは間違いありません。

これは、多段シフトレジスタではめったにありません。しかし、これは最初の簡単な例でした。ポジティブなローからハイのクロックエッジのみに関心があります。

立ち下がりエッジは無視できます。 Q はとても見やすいです D をフォローする 上記の時刻に。

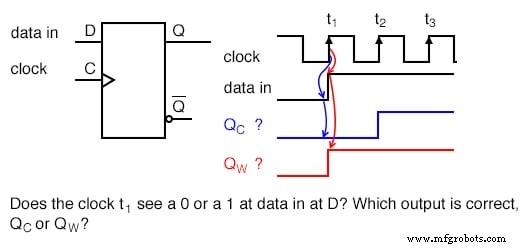

これを、「データ入力」がクロックの正のエッジで変化しているように見える下の図と比較してください。

「データ入力」は時刻t 1 で変化するように見えるので 上記のタイプ D は何ですか FFは時計の時間に見えますか?

簡単になりすぎた答えは、 D に存在していたデータが表示されるというものです。 時計の前に。

それが Q に転送されるものです 時刻t 1 。正しい波形はQ C です。 。 t 1 で Qがまだゼロでない場合、Qはゼロになります。

D レジスタは時間t 2 まで1を認識しません 、その時点でQが高くなります。

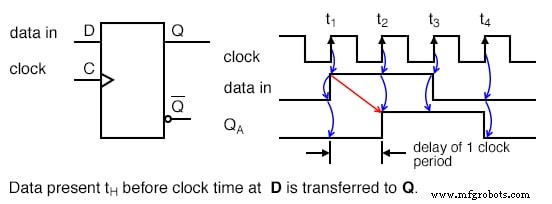

上記のデータ以降、 D に存在します Q にクロックされます 時計の時間に、そして Q 次の時刻、 D まで変更できません データがすでにクロックに同期されている場合、FFはデータを1クロック周期だけ遅延させます。 Q A 波形は「データ入力」と同じですが、1クロック周期の遅延があります。

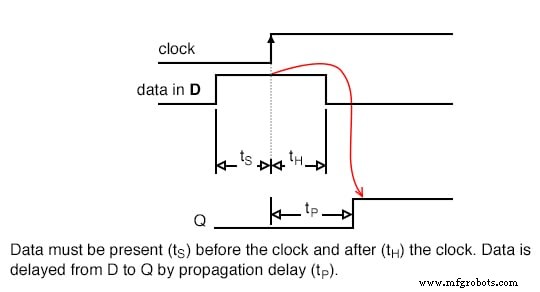

タイプ D の入力の詳細 フリップフロップは、次の時刻に表示されます。

下図を参照してください。 「データ入力」は時計の時刻(上記)で変化するように見えるため、 D が何であるかを判断するには、さらに情報が必要です。 FFは見ています。

「データ入力」が別のシフトレジスタステージからのものである場合、別の同じタイプの D FF、データシートに基づいていくつかの結論を導き出すことができます 情報。

デジタルロジックのメーカーは、データシートで部品に関する情報を利用できるようにしています。以前は、データブックと呼ばれるコレクションでしか利用できませんでした。 。

データブックは引き続き利用できます。ただし、製造元のWebサイトが最新のソースです。

以下のデータは、5V DC で動作するようにCD4006bデータシートから抽出されました。 、これはタイミングを説明するための例として機能します。 [*]

- t S =100ns

- t H =60ns

- t P =200-400ns typ / max

t S セットアップ時間です 、時刻データは時刻の前に存在する必要があります。この場合、データは D に存在する必要があります 時計の100ns前。

さらに、データは保持時間の間保持する必要があります t H =クロック時間後60ns。 D からのデータを確実にクロックするには、これら2つの条件が満たされている必要があります。 Q へ フリップフロップの。

D のデータとして、セットアップ時間60nsを満たすのに問題はありません。 別のシフトレジスタステージからのものである場合は、前のクロック期間全体にわたって存在しています。

たとえば、1 Mhzのクロック周波数では、クロック周期は1000 µsであり、十分な時間です。

データは、実際にはクロックの前の1000µsの間存在します。これは、必要な最小t S よりもはるかに大きい値です。 60nsの。

保持時間t H 別のステージのQに接続されたDは、前のステージの伝播遅延t P よりも速く変化できないため、=60nsが満たされます。 =200ns。

前の D の伝搬遅延がある限り、ホールドタイムが満たされます。 FFはホールドタイムよりも大きいです。

D のデータ 別のステージによって駆動される Q CD4006bの場合、200nsより速く変化することはありません。

要約すると、 Q を出力します フリップフロップが多段シフトレジスタにカスケード接続されている場合、ほぼクロック時間で入力Dに従います。

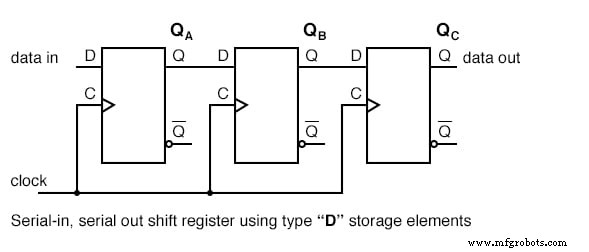

3つのタイプ D フリップフロップはQからDにカスケード接続され、クロックが並列化されて、上記の3ステージシフトレジスタを形成します。

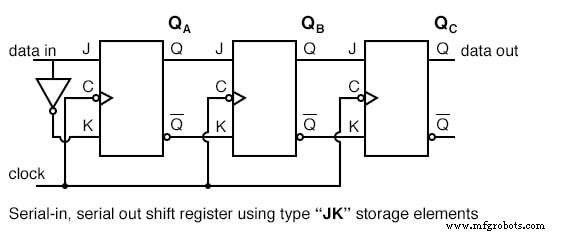

JK と入力します フロップをFlipFlopsでカスケード接続し、QからJ、Q ’からKにクロックを並列に接続して、上記のシフトレジスタの代替形式を生成します。

シリアル入力/シリアル出力シフトレジスタには、クロック入力、データ入力、および最終ステージからのデータ出力があります。

一般に、他のステージの出力は使用できません。それ以外の場合は、シリアル入力、パラレル出力のシフトレジスタになります。

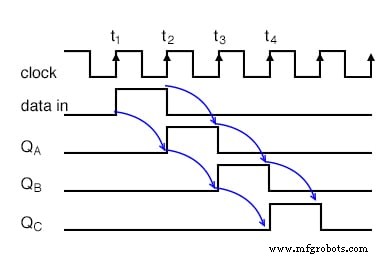

以下の波形は、シリアル入力、シリアル出力のシフトレジスタの前の2つのバージョンのいずれかに適用できます。

3対の矢印は、3ステージシフトレジスタが一時的に3ビットのデータを格納し、入力から出力まで3クロック周期だけ遅延させることを示しています。

時刻t 1 0 の「データ入力」 D からクロックされます Q へ 3つの段階すべての。特に、 D ステージの A ロジック 0 が表示されます 、Q A にクロックされます 時間t 2 まで残ります 。

時刻t 2 1 の「データ入力」 D からクロックされます Q A へ 。ステージ B および C 、 0 、前のステージから供給され、Q B にクロックされます およびQ C 。

時刻t 3 0 の「データ入力」 D からクロックされます Q A へ 。 Q A 「データ入力」が 0 であるため、ローになり、残りのクロックの間ローのままになります 。 Q B t 3 でハイになります 1 による 前の段階から。 Q C t 3 後もまだ低い 前のステージからの安値のため。

Q C 最終的にクロックt 4 でハイになります D への高給による 前の段階からQ B 。初期のすべてのステージには 0 があります sはそれらにシフトしました。そして、t 5 での次のクロックパルスの後 、すべてのロジック 1 sはシフトアウトされ、 0 に置き換えられます s

シリアルイン/シリアルアウトデバイス

Texas Instrumentsの厚意により、集積回路として利用可能な以下の部品を詳しく見ていきます。

完全なデバイスデータシートについては、リンクをたどってください。

- CD4006b18ビットシリアル入力/シリアル出力シフトレジスタ

- CD4031b64ビットシリアル入力/シリアル出力シフトレジスタ

- CD4517bデュアル64ビットシリアル入力/シリアル出力シフトレジスタ

次のシリアル入力/シリアル出力シフトレジスタは4000シリーズ CMOS (相補型金属酸化膜半導体)ファミリ部品。

そのため、V DD を受け入れます 、3ボルトから15ボルトの正電源。 V SS ピンは接地されています。

シフトクロックの最大周波数。V DD によって異なります。 、は数メガヘルツです。

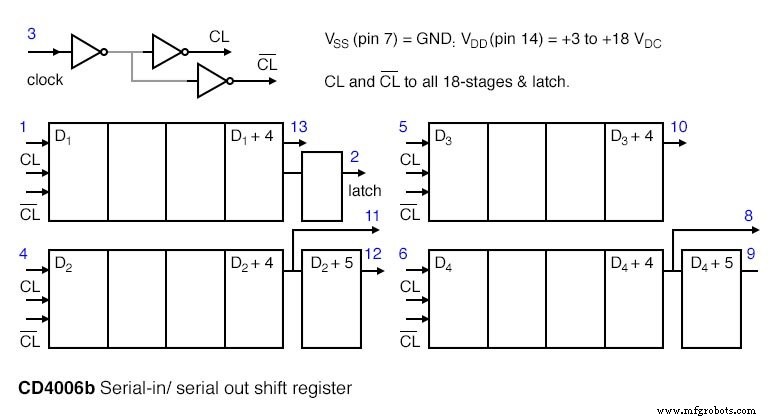

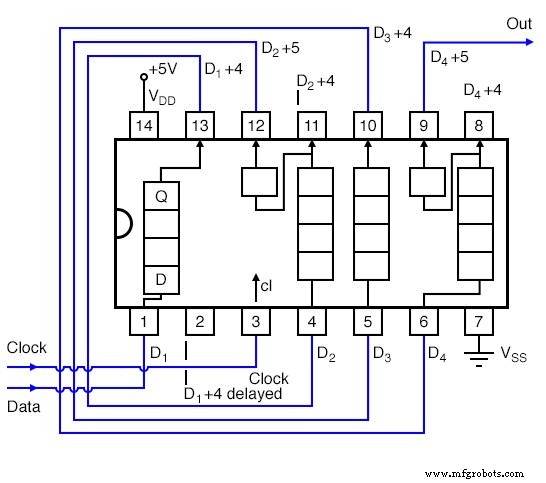

18ビットCD4006bは、4ビットの2つのステージと、4ビットの出力タップを備えた5ビットの2つのステージで構成されています。

したがって、5ビットステージは4ビットシフトレジスタとして使用できます。

完全な18ビットシフトレジスタを取得するには、以下に示すように、すべてのステージが単一のシフトレジスタを作成するまで、1つのシフトレジスタの出力を別のシフトレジスタの入力にカスケードする必要があります。

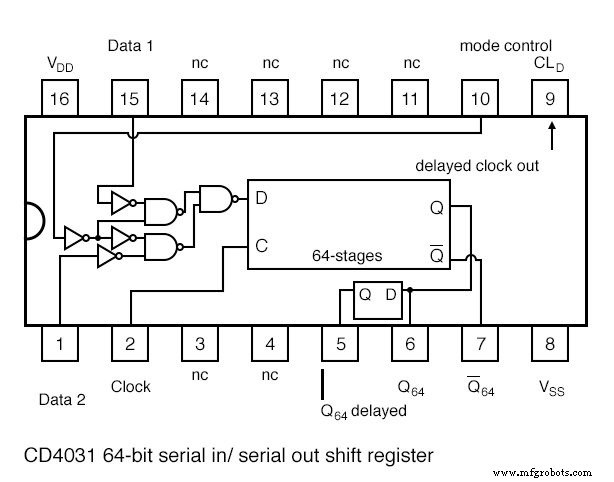

CD403164ビットシリアル入力/シリアル出力シフトレジスタを以下に示します。

多くのピンが接続されていません(nc)。 QとQ ’の両方が64番目のステージ、実際にはQ 64 から利用可能です。 およびQ ’ 64 。

Q 64 もあります 半クロックサイクルだけ遅延する半ステージから「遅延」します。主な機能は、シフトレジスタへのデータ入力にあるデータセレクタです。

「モード制御」は、データ1とデータ2の2つの入力から選択します。「モード制御」がハイの場合、シフトレジスタへの入力用に「データ2」からデータが選択されます。

「モード制御」がロジックローの場合、「データ1」が選択されます。この例を下の2つの図に示します。

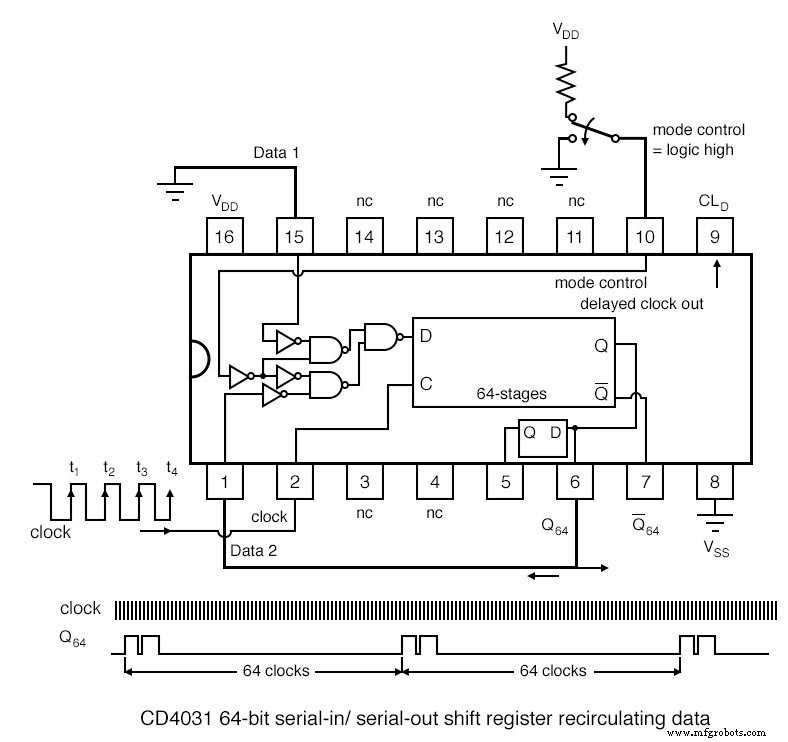

上記の「データ2」はQ 64 に配線されています シフトレジスタの出力。 「モード制御」が高い場合、Q 64 出力はシフターデータ入力Dに戻されます。

データは再循環されます 出力から入力へ。上記のように、データは64クロックパルスごとに繰り返されます。

発生する問題は、このデータパターンが最初にシフトレジスタにどのように組み込まれたかということです。

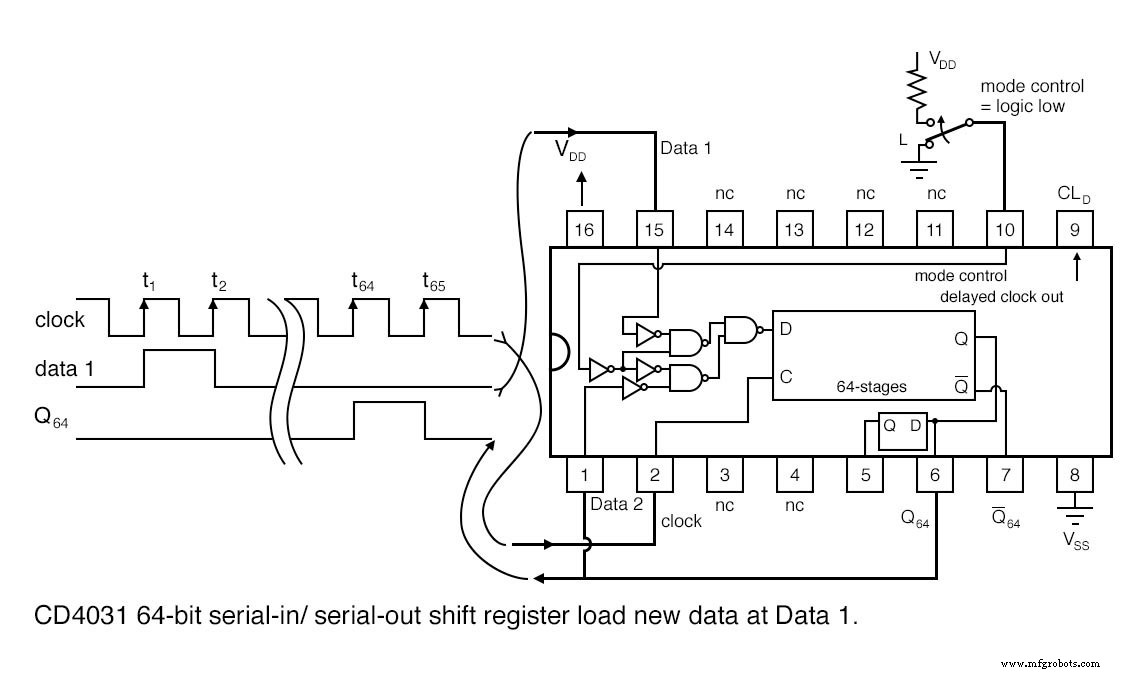

「モード制御」がローの場合、CD4031「データ1」がシフターへの入力用に選択されます。

出力、Q 64 、下部のデータセレクタゲートが無効であるため、再循環されません。 。

無効とは、下側のNANDゲートで論理ローの「モード選択」が2回反転してローになることを意味します。これにより、下側のピン(データ2)の信号がゲート出力に渡されなくなります。

したがって、無効になります。

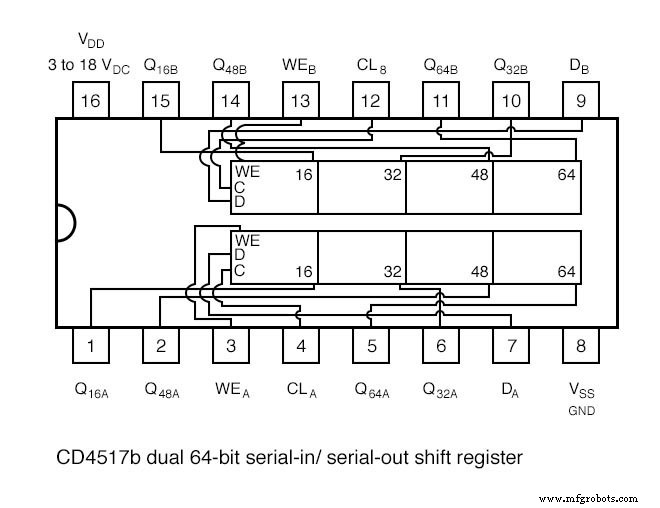

CD4517bデュアル64ビットシフトレジスタを上に示します。 16、32、および48番目のステージのタップに注意してください。

つまり、これらの長さのシフトレジスタは、64ビットシフターの1つから構成できます。

もちろん、64ビットシフターをカスケード接続して、80ビット、96ビット、112ビット、または128ビットのシフトレジスタを生成することもできます。

時計CL A およびCL B 2つのシフターをカスケード接続するときに並列化する必要があります。 WE B およびWE B 通常のシフト操作のために接地されています。

シフトレジスタAおよびBへのデータ入力はD A です。 およびD B それぞれ。

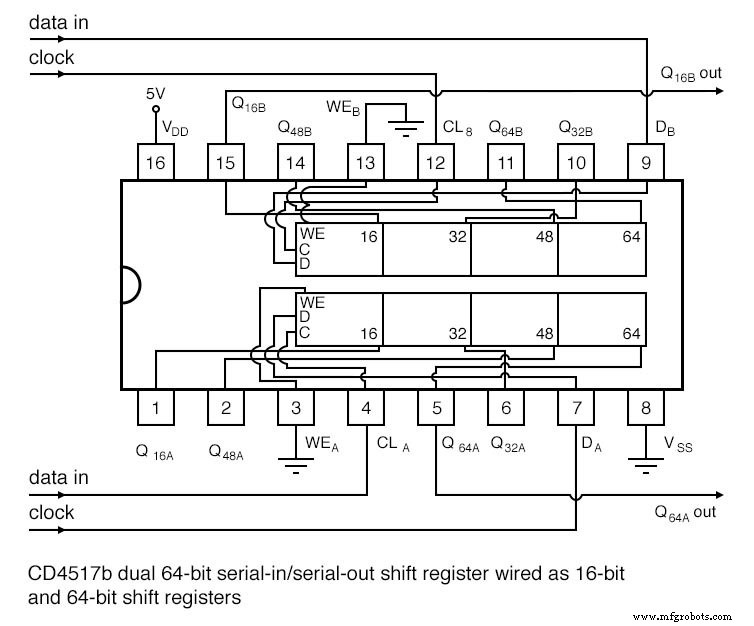

16ビットのシフトレジスタが必要だとします。

これはCD4517bで構成できますか?同じ部分からの64シフトレジスタはどうですか?

上に、セクションBの16ビットシフトレジスタとして配線されたCD4517bを示します。

セクションBのクロックはCL B です。 。データはCL B でクロックインされます 。そして、16クロック遅れたデータは、Q 16B から選択されます。 。 WE B 、書き込みイネーブルは接地されています。

上記では、独立セクションAの64ビットシフトレジスタとして配線された同じCD4517bも示しています。

セクションAのクロックはCL A です。 。データはCL A に入力されます 。 64クロックパルスで遅延したデータは、Q 64A から取得されます。 。 WE A 、セクションAの書き込みイネーブルは接地されています。

関連するワークシート:

- シフトレジスタワークシート

産業技術