Delta-Sigma ADC

より高度なADCテクノロジーの1つは、いわゆるデルタシグマまたはΔΣ(適切なギリシャ文字表記を使用)です。数学と物理学では、ギリシャ文字の大文字のデルタ(Δ)は違いを表します。 または変更 、大文字のシグマ(Σ)は合計を表します :複数の用語を一緒に追加します。このコンバーターは、同じギリシャ文字で逆の順序で参照されることがあります:sigma-delta、またはΣΔ。

ΔΣコンバータでは、アナログ入力電圧信号が積分器の入力に接続され、入力の大きさに対応する出力で電圧変化率またはスロープを生成します。次に、このランピング電圧は、コンパレータによって接地電位(0ボルト)と比較されます。

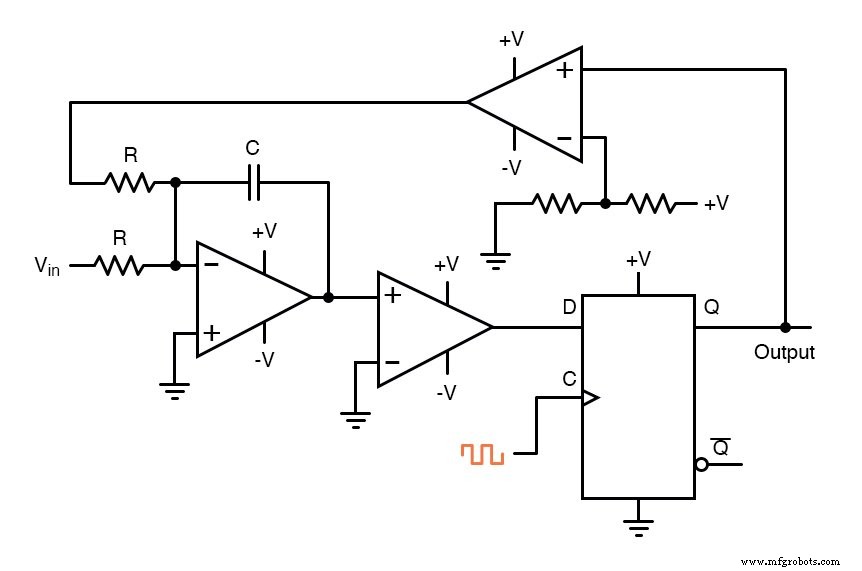

コンパレータは一種の1ビットADCとして機能し、積分器の出力が正か負かに応じて1ビットの出力(「ハイ」または「ロー」)を生成します。次に、コンパレータの出力は、高周波でクロックされるDタイプのフリップフロップを介してラッチされ、フィードバックされます。 積分器を0ボルト出力の方向に駆動するために、積分器の別の入力チャネルに接続します。基本的な回路は次のようになります:

概略図

左端のオペアンプは(合計)積分器です。積分器が供給する次のオペアンプは、コンパレータ、つまり1ビットADCです。次に、Dタイプのフリップフロップがあります。これは、クロックパルスごとにコンパレータの出力をラッチし、回路の上部にある次のコンパレータに「ハイ」または「ロー」信号を送信します。

この最後のコンパレータは、フリップフロップの単極性0V / 5Vロジックレベル出力電圧を+ V / -V電圧信号に変換して、積分器にフィードバックするために必要です。積分器の出力が正の場合、最初のコンパレータはフリップフロップのD入力に「ハイ」信号を出力します。

次のクロックパルスで、この「ハイ」信号がQラインから最後のコンパレータの非反転入力に出力されます。この最後のコンパレータは、入力電圧がしきい値電圧の1/2 + Vを超えていることを確認し、正の方向に飽和して、積分器のもう一方の入力に完全な+ V信号を送信します。

この+ Vフィードバック信号は、積分器の出力を負の方向に駆動する傾向があります。その出力電圧が負になると、フィードバックループは補正信号(-V)を積分器の上部入力に送り返し、積分器を正の方向に駆動します。

これは、実際のデルタシグマの概念です。最初のコンパレータは差異を検出します。 (Δ)積分器の出力とゼロボルトの間。インテグレータの合計 (Σ)アナログ入力信号を使用したコンパレータの出力。

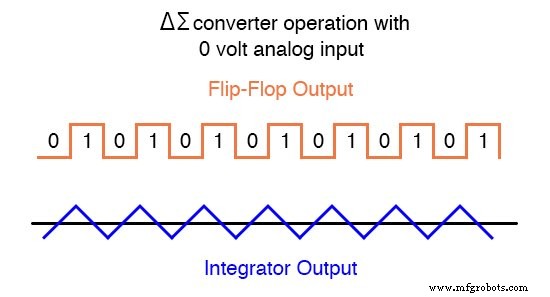

機能的には、これにより、フリップフロップによって出力されるビットのシリアルストリームが生成されます。アナログ入力がゼロボルトの場合、フィードバック電圧に応答する場合を除いて、積分器は正または負のどちらにもランプする傾向がありません。

このシナリオでは、フィードバックシステムが積分器の出力をゼロボルトに維持しようとして前後に「ハント」するため、フリップフロップの出力は「高」と「低」の間で継続的に振動します。

出力波形

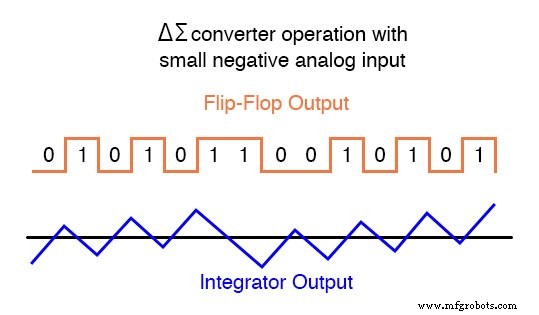

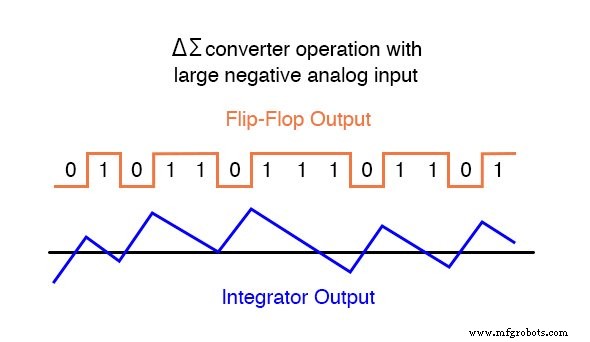

ただし、負のアナログ入力電圧を印加すると、積分器はその出力を正の方向にランプする傾向があります。フィードバックは、一定の時間にわたる一定の電圧によってのみ積分器のランピングに追加できるため、フリップフロップによって出力されるビットストリームはまったく同じにはなりません。

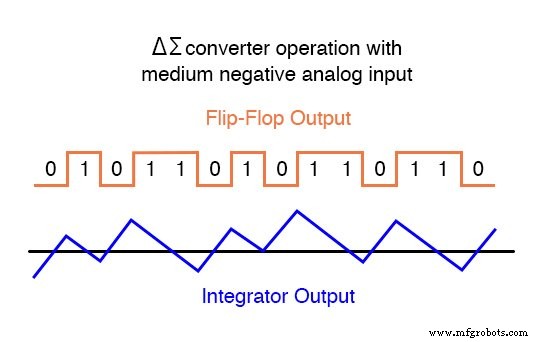

より大きな(負の)アナログ入力信号を積分器に適用することにより、その出力を正の方向により急に傾斜させることができます。したがって、フィードバックシステムは、積分器の出力をゼロボルトに戻すために、以前よりも多くの1を出力する必要があります。

アナログ入力信号の大きさが大きくなると、フリップフロップのデジタル出力で1が発生します。

並列2進数出力は、ビットのシリアルストリームを平均化することによってこの回路から取得されます。たとえば、カウンタ回路は、特定のクロックパルス数でフリップフロップによって出力された1の総数を収集するように設計できます。このカウントは、アナログ入力電圧を示します。

このテーマにはバリエーションがあり、複数の積分器ステージやコンパレータ回路を使用して1ビット以上を出力しますが、すべてのΔΣコンバータに共通する概念の1つは、オーバーサンプリングです。 。オーバーサンプリングとは、アナログ信号の複数のサンプルがADC(この場合は1ビットADC)によって取得され、それらのデジタル化されたサンプルが平均化されることです。

最終的に、信号から解決されるビット数が効果的に増加します。つまり、オーバーサンプリングされた1ビットADCは、速度は遅くなりますが、1回のサンプリングで8ビットADCと同じ仕事をすることができます。

関連ワークシート:

- アナログ-デジタル変換ワークシート

産業技術