高速 PCB のイメージ プレーンの設計方法

現在、多層PCBはほとんどの高速回路システムで使用されており、多くの回路システムには多数の動作電力があり、イメージプレーンの設計、特に複数の電源/グランドプレーン間の関係の解決に厳しい要件が課せられています.さらに、発振器が RF (無線周波数) エネルギーを生成するのを防ぎ、高出力コンポーネントに優れた熱放散を提供するために、特殊な銅被覆表面をデバイス層設計で設計する必要があります。

イメージ プレーンの機能

イメージ プレーンは、プリント回路基板の信号層に隣接する銅張りの表面です。イメージ プレーンの主な機能は次のとおりです。

1)。リフロー ノイズと EMI (電磁干渉) を低減します。イメージ プレーンは、特に配電システムに大電流が流れている場合に、信号のリフローに対して低インピーダンスのパスを提供します。さらに、信号とリフローによって形成される閉じたリング領域が減少するため、EMI が低下します。

2)。高速デジタル回路の信号線間のクロストークを抑制。クロストークは、比 D/H によって決定されます。ここで、D は干渉源と干渉対象物との間の距離を表し、H は信号層間のイメージ プレーンの高さを表します。信号線間のクロストークが最終的に制御されるように、比率 D/H は H の値を変更することによって制御できます。

3)。インピーダンスの制御。プリント配線の特性インピーダンスは、ワイヤの幅と、ワイヤとイメージ プレーン間の高さに関連しています。イメージプレーンがない場合、インピーダンスを制御できず、伝送線路の整合不良や信号の反射につながる可能性があります。

また、像面も反射による外板へのノイズを抑えることができます。これらの機能を実装するには、イメージ プレーンだけでは不十分であることを認識しておく必要があります。期待される目標を達成するには、厳密な設計規則を補足する必要があります。この事実は次のように言えます:高速デジタル回路のノイズを制御するには、イメージ プレーンが不可欠ですが、単独では機能しません。

信号リフローのレイヤースキップ

多層 PCB では、各レイアウト層は 1 つのイメージ プレーンに隣接する必要があり、信号の戻り回路は対応するイメージ プレーン上を流れます。信号線がレイアウト層を貫通していない場合は、まず信号線をレイアウト層に接続し、その後信号線を別の層にスルーホールで接続する方法が一般的です。したがって、信号線はある層から別の層にスキップしているので、同じ経路をたどって電流を返しています。両方の層がグランド層の場合、2 つの層を接続するスルー ホールまたはグランド ピンにより、還流電流をスキップすることができます。 1 層が電源層でもう 1 層がグランド層の場合、帰還電流が層間をスキップする唯一の機会は、デカップリング コンデンサを配置した位置です。デカップリング コンデンサやグランド層を接続するスルー ホールがない場合、最も遠くまで行かなければならない帰還電流をスキップする必要があり、帰還電流が他の回路とデカップリングされ、クロストークや EMI が発生します。

その結果、PCB 設計の過程で、レイヤ スキップは、せいぜいコンポーネントに隣接するグランド ピンまたはデカップリング コンデンサの周囲に設定する必要があります。これが実現できない場合は、グランド スルー ホール (2 つのグランド層の間をスキップ) またはバイパス コンデンサ (電源層とグランド層の間をスキップ) をスキップ ポイントに配置して、戻り電流をスキップさせることができます。

平面の分割

多層 PCB を使用するプロセスでは、統合されたイメージ プレーンを分割プレーンと呼ばれるいくつかの独立した部分に分割する、特定の幅の銅箔のない領域を生成する必要がある場合があります。

プレーンの分割は通常、ノイズの影響を受けやすい回路を阻止し、デジタル ノイズがアナログ、オーディオ、I/O 領域に侵入するのを阻止し、5V と 3.3V の電源電圧を分離するなど、さまざまな基準電圧を分離するために使用されます。

分割面は、完全分割と不完全分割に分類できます。前者は、分割後の電源層とグランド層の間の完全な分離を指します。後者は、グランド層が「ブリッジ」によって接続されている間、電源層間の完全な分離を指します。完全な分割を使用するか不完全な分割を使用するかは、分割プレーン間に信号接続があるかどうかによって異なります。

• プレーンの分割例

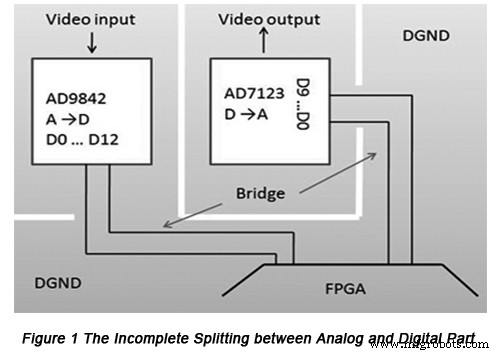

図 1 は、テスト プラットフォームのアナログとデジタルの混合回路のイメージ プレーン設計の一部です。ビデオアナログ入力はAD変換によりFPGAに伝送され、DA変換として出力されます。 AD と DA はどちらも独立した電源コンポーネントを使用して電力を供給します。デジタル コンポーネントはボードのスペースの大部分を占めていますが、アナログ コンポーネントはごく一部しか占めていません。ただし、それらはすべて、システム全体のパフォーマンスにとって重要な不可欠な部分です。したがって、これらのコンポーネントを扱うプロセスには細心の注意を払う必要があります。デジタル部のノイズがアナログ部に入らないことが理想です。ただし、AD コンバータや DA コンバータからの信号の一部は、デジタル部の FPGA に接続されています。これらの接続された信号のリフローを確実にするために、デジタル電源とアナログ電源は完全に分離する必要がありますが、デジタル グランドとアナログ グランドは不完全に分離して、デジタル部分からのアナログ部分の影響を最小限に抑える必要があります。

デジタル部分からアナログ部分へのすべてのラインは、データ信号のリフローがブリッジによって戻ることができるように、必要なワイヤを通過するのにちょうど適した開口部のサイズが必要なブリッジを通過する必要があり、結果として他の信号への干渉を回避します。戻り経路の巻線の。この PCB 設計では、AD 部分と DA 部分のグランドは互いに完全に分離されています。

• 平面を分割する過程での問題

を。分離層の重なり

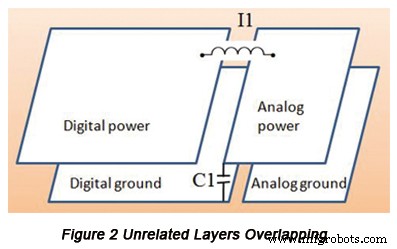

多層PCBでは、通常、異なる電源を分離するために分割プレーンが使用されます。一般的に言えば、これらの電源の対応するグランド層は互いに分離されています。つまり、各電源には独自の基準層があります。 PCB 設計のプロセスでは、絶縁層の重なりを避ける必要があります。たとえば、ほとんどの多層 PCB では、アナログ部分とデジタル部分の電源層とグランド層が互いに分離されています。図 2 のように、アナログ電源層とデジタル グランド層を空間的に重ねてはいけません。

重なり合う分離層が現れると、小さなパッド容量 C1 が重なり合う領域に現れます。静電容量により、ある層から別の分離された静的で独立した層に RF エネルギーが伝達され、分離の有効性が低下します。

b.デカップリング コンデンサの配置

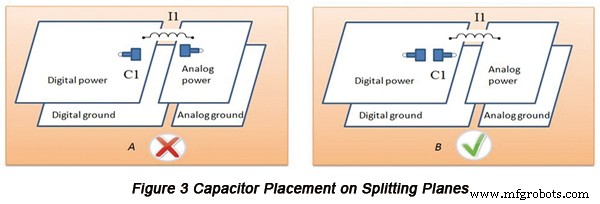

高速コンポーネントから発生する高周波のノイズを除去するために、PCB 上に多数のデカップリング コンデンサが配置されます。 PCB で分割プレーンが出てくると、レイアウトの過程で、デカップリング コンデンサのグランド ピンが、対応するグランド層ではなく、他の基準グランド層に接続されないという状況が発生する可能性があります。このタイプの間違いが発生する可能性があり、1 つのレイヤーから別のレイヤーへのノイズのデカップリングにつながります。これは、分割プレーンのオーバーラップと同様です。そのため、この問題は設計段階で対処する必要があります。再びデジタル・アナログ混合回路を例にとります。アナログ電源はフェライト ビーズを介してデジタル部分から取り込まれ、C1 はデジタル部分のデカップリング キャパシタンスを表します。図 3A では、C1 の電源ピンがデジタル電源に接続され、グランド ピンがアナログ グランドに接続されているため、敏感なアナログ部分で高周波のデジタル ノイズが分離されます。これは間違った接続です。図 3B は右のデカップリング コンデンサの接続です。

c.一点接地

異なる電力の基準層を一緒に接続する場合は、一点接地を確保する必要があります。例示したデジタル・アナログ混合回路では、回路基板はデジタル部分とアナログ部分に分類され、デジタル グランドとアナログ グランドの両方に少なくとも 2 つの接続点があり、ノイズ信号が 2 つの接続点を介して 2 つの基準層の間を循環する可能性があります。 「グランドループ」と呼ばれます。グラウンド ループは、ノイズ、EMI、エネルギー消費、熱放散の問題につながります。グランド ループの問題に対する簡単な解決策があります。参照レイヤー間に接続ポイントが 1 つしかない限り、ループは形成されません。

ローカル グラウンド レイヤー

イメージ プレーンの一部として、ローカル グランド層は、PCB の上面にある銅被覆を指し、内部グランド層に直接接続されます。その主な機能は、一部の主要なチップ (発振器など) の内部で生成された RF 磁束を捕捉すること、または電力消費に使用することです。

優れた性能を得るには、オシレータ、水晶、およびクロック サポートを独立したローカル グランド層に組み立てる必要があります。その理由は次のとおりです。

1)。発振器が金属クラッドにパッケージされている場合、金属クラッド内で生成される RF 電流が非常に大きくなる可能性があり、そのグランド ピンは低エネルギー消費の方法で大電流をグランドに導くことができません。その結果、この金属クラッドはユニポーラアンテナとなる。

2)。 PCB にオシレータを配置するときに表面実装アセンブリ技術が使用される場合、プラスチック材料は通常 SMT パッケージに使用され、RF 電流が接地点に流れるのを止めるため、上記の問題は悪化します。最後に、パッケージ内部で生成された RF 電流は自由空間に放射され、他のコンポーネントと分離されます。

3)。通常のオシレータは、超高速で高速なエッジ レートを持つコンポーネントに属するクロック バッファリングを駆動することができ、大量の RF 電流を生成します。これは、電流機能の障害につながる可能性があります。

ローカル グランド層が発振器とクロック回路に組み込まれている場合、イメージ プレーンが提供され、発振器と対応する回路の内部で生成された RF エネルギーをキャッチするために使用され、RF 放射を減らすことができます。

20時間ルール

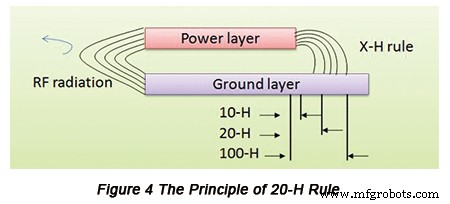

経験則として、20-H ルールは、高密度の多層 PCB において、回路基板が自由空間に放射する電磁エネルギーを減らすために、電源層のサイズを、H 2 つのレイヤー間の距離を表します。図 4 の左部分は、エッジ放射が非常に強いため、隣接する回路の機能に影響を与える特別な設計のない電源/グランド層を示しています。右側の部分は、電源面のサイズを X-H だけ小さくすることで、RF 放射の状況を示しています。下地層に多くの磁力線が引き寄せられ、RF 放射エネルギーが減少していることが分かります。実験結果によると、RF 放射力は 10-H から下がり始めます。 20-H の場合、地面は磁流の 70% を引き付けることができます。 100-Hの場合、磁力を98%減少させることができます。

当然、20-H はすべての PCB 構造に最適というわけではありません。 20-H の効率は、動作周波数、電源/グランド層の物理的サイズ、および PCB ボードの SRF (自己共振周波数) を決定する後者の 2 つの要素間の距離に依存します。調査によると、PCB が任意の SRF で動作する場合、20-H は機能せず、接地も放射エネルギーを引き付けることができません。さらに悪いことに、代わりに大量の放射線エネルギーが生成されます。したがって、実際の高速回路では、20-H ルールを選択するかどうかを決定する際に、特定の状況を考慮する必要があります。

役立つリソース

• 高速レイアウトのヒント

• EMI の影響を軽減するための高速 PCB ルーティング テクニック

• 高速 PCB 設計に関する誤解と戦略

• 微分等尺性高速 PCB 設計の処理とシミュレーション検証

• PCBCart のフル機能 PCB 製造サービス - 複数の付加価値オプション

• PCBCart の高度な PCB アセンブリ サービス - 1 個から開始

産業技術