PSRRが強化された180nmの自己バイアスバンドギャップリファレンス

要約

この論文では、高い電源除去率(PSRR)を備えた改良された自己バイアスバンドギャップリファレンス(BGR)が提示されます。フィードバックループを構成するオペアンプは、消費電力を抑えるために正の温度係数(TC)電圧の生成と多重化され、絶対温度(PTAT)電圧に比例するようにオフセット電圧が採用されています。温度に依存しないリファレンス生成により、PSRR拡張のために2つのフィードバックループが同時に実現され、ローカルの負のフィードバックループ(LNFL)とグローバルな自己バイアスループ(GSBL)が形成されます。提案されたBGRは180nmのBCD技術で実装されており、その結果は、生成された基準電圧が2.506 Vであり、TCが-55〜125°Cの温度範囲で25 ppm /°Cであることを示しています。ライン感度(LS)は0.08‰/ Vです。フィルタコンデンサがない場合、PSRRは低周波数で76 dB、46dBを超えて1MHzまでです。

はじめに

電圧リファレンスは、電子システムのコアモジュールの1つであり、医療用電子機器、電力管理、ワイヤレス環境センサー、および通信回路で広く使用されています。技術の進歩に伴い、チップの面積は縮小し続け、干渉防止能力は増加し続け、電圧リファレンスの構造最適化とノイズ耐性の要件は、特にナノスケールのアプリケーションで劇的に増加しています[1]。

従来のバンドギャップリファレンス(BGR)回路では、回路全体にバイアス電流を供給するために追加の回路ブロックが必要であり、これにより回路面積と消費電力が大幅に増加します。同時に、発生するバイアス電流は温度の影響を大きく受け、基準電圧の温度係数(TC)に影響を与えます。区分的曲率補正[2]、指数曲率補正[3]、リークベースの平方根補正(LSRC)[4]など、TCを改善するための高次補正手法が多数報告されています。従来のBGR回路のもう1つの欠点は、外部環境の影響を大きく受け、出力電圧が不安定になることです。これがこの記事の焦点です。

電源除去比(PSRR)は、電圧リファレンスのノイズ耐性を測定するための重要なパラメータです。 PSRRを改善するための従来のソリューションは、追加の増幅器、長チャネルトランジスタ、カスコード構造[6]、追加のゲインステージ[7]など、チップ面積と消費電力[5]を犠牲にします。 [8]では、低周波数と高周波数でそれぞれPSRRを改善するために、アクティブ減衰器とインピーダンス適応補償が採用されました。ユエら[9] PSRRを強化するためにカスコードカレントミラーを使用しました。ボディバイアスとネガティブフィードバック技術は、高いPSRRのために[10]で利用されました。

上記の問題を克服するために、この概要では、高いPSRRを備えた改善された自己バイアスBGRが提案されています。 PSRR拡張のために2つのフィードバックループが同時に実現され、ローカルの負のフィードバックループ(LNFL)とグローバルな自己バイアスループ(GSBL)が形成されます。一方、BGR全体の自己バイアス電流源(SBCS)が実現されます。定常状態では、提案されたBGRは、追加のバイアス電流モジュールやチップ領域なしでGSBLを介してセルフパワーで駆動されます。提示された手法は、GSBLに組み込まれた電流増幅器を介して供給電圧を出力基準電圧から分離します。これにより、PSRRを効果的に改善できます。また、出力電圧が不安定にならないように、出力電圧端子にLNFLを設計し、出力電圧を安定させています。さらに、温度安定基準電圧は、LNFLとGSBLを多重化して生成されます。これらの方法を使用すると、PSRRが強化された自己バイアスBGRが、コンパクトな構造と消費電流で実装されます。

メソッド

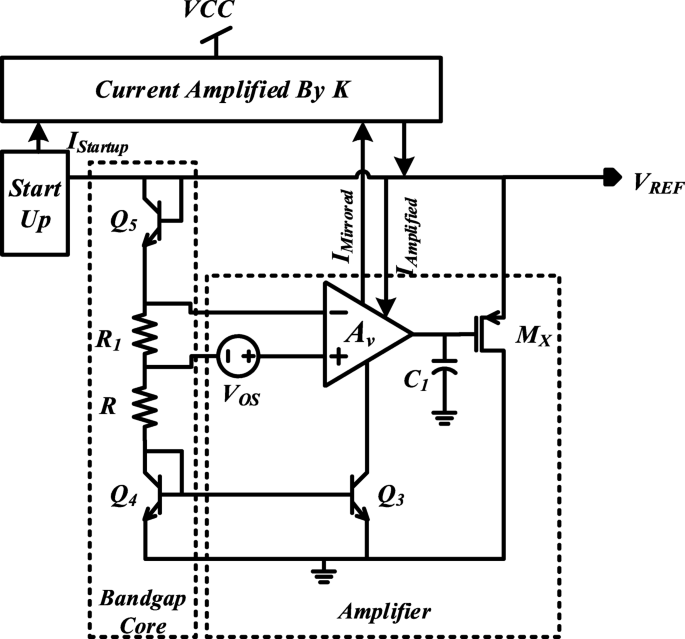

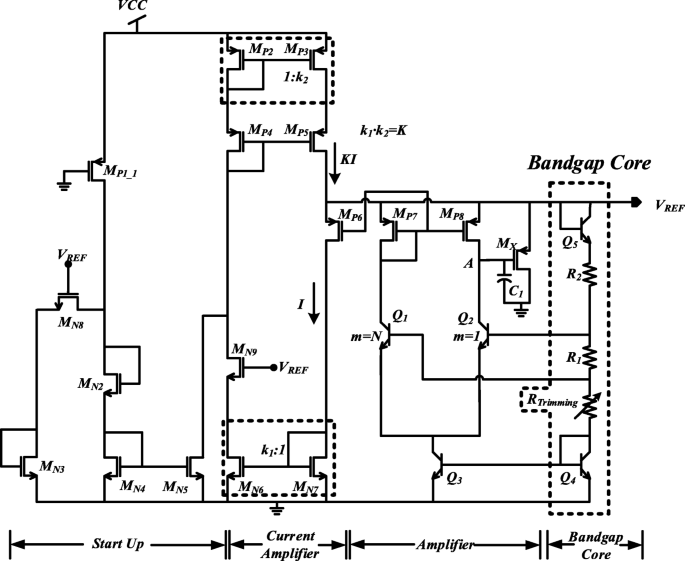

図1に示すように、提案されたBGR回路は、起動回路、電流増幅器、オペアンプ、およびバンドギャップリファレンスコアで構成されています。起動回路は、ゼロ縮退点を取り除くために使用されます。アンプの内蔵オフセット電圧は絶対温度(PTAT)電圧に比例するように設定されており、抵抗R1を介してPTAT電流を実現できます。 R1とR2の両端の電圧の正のTCで、 V の負のTC BE(Q5) および V BE(Q4) ノード V で温度安定した基準電圧を達成するために、適切にキャンセルすることができます REF 。同時に、パフォーマンスを向上させるためにアンプの助けを借りて形成されたLNFL。図1上部の電流増幅器と組み合わせることで、PSRRをさらに改善するためのGSBLが実現されます。提案されたBGRの詳細な実装を図2に示します。

提案された電圧リファレンスの等価アーキテクチャ図

提案された電圧リファレンスの概略図

起動回路

起動回路を図2の左側に示します。起動段階の開始時に、出力電圧 V REF 低レベルであり、MN8とMN9をオフに保ちます。 MP1_1を流れる電流は、MP5への起動電流を生成するために使用されます。MP1_1は、アスペクト比が非常に小さい大きな抵抗です。 V での電圧 REF 起動電流により徐々に充電されます。 V の電圧が REF バンドギャップコア部の最小動作電圧を超えると、アンプのバイアス電流が発生します。これにより、BGRが目的の操作ポイントに移動します。同時に、トランジスタMN8とMN9が徐々にオンになり、MP5の供給電流がバンドギャップコアで生成された自己バイアス電流に切り替わります。起動が完了した後、 V の起動電流はオフになりません。 REF 何らかの理由で基準電圧が低下した場合の再調整[11]。

SBCSジェネレーター

提案されたBGRには2つのSBCSループがあり、パフォーマンスの向上に役立ちます[1]。最初のものはアンプのテール電流にあります。トランジスタQ4を流れるPTAT電流はQ3にミラーリングされます。ただし、Q4を流れる電流は、アンプの入力オフセット電圧にクランプされた抵抗R1の両端の電圧によって決まります。 MP7とMP8のアスペクト比が同じであるため、アンプの入力オフセット電圧は次のように表すことができます。

$$ {V} _ {OS} ={V} _T \ ln N $$(1)ここで N はQ1とQ2の面積比であり、 V T は熱電圧です。したがって、増幅器とバンドギャップのコア部分の電流はPTAT電流であり、これは次の式で求めることができます。

$$ {I} _ {R1} ={V} _T \ ln N / {R} _1 $$(2)バンドギャップリファレンスコアの電流はテール電流として増幅器にミラーリングされ、最初の自己バイアスループを形成します。

2番目のSBCSループは、電流増幅器で構成されています。式(2)に示すPATA電流は、MP7およびMP6のカレントミラーによって電流増幅器にミラーリングされます。次に、現在の I 、 K によって増幅されます ノードVREFへの現在のソースとして。これは

として記述できます。 $$ K ={k} _1 {k} _2 $$(3)ここで k 1 = S MN 6 / S MN 7 、 k 2 = S MP3 / S MP2 、 S i トランジスタのアスペクト比 i 。したがって、現在の KI は、アンプとバンドギャップのコア部分に再注入され、2番目の自己バイアスループを構成します。

低消費電力での適切な動作を保証するために、電流、 KI 、アンプとバンドギャップコアの最小電流要件よりもわずかに大きくする必要があります。提案された設計では、MP6、MP7、およびMP8を流れる電流は同じレベル I に設定されています。 。バンドギャップコアを流れる電流は2 I 。したがって、関係、6≥ K > 5を満たす必要があります[12,13,14]。

V REF 発電機回路

V REF 図2の右側に、増幅器とバンドギャップコアで構成されるジェネレータ回路を示します。式(2)に示すように、増幅器のPTATオフセット電圧はSBCSループによって多重化されます[15]。これにより、R1、R2、およびR トリミングを流れる電流が生成されます。 はPTAT電流であり、Q4とQ5の負のTCの温度補償として使用されます。生成された基準電圧 V REF 、次のように表すことができます

$$ {V} _ {REF} =2 {V} _ {BE} + \ left(1+ \ frac {R_2 + {R} _ {Trim \ min g}} {R_1} \ right){V} _T \ ln N $$(4)( R 2 + R トリム min g )/ R 1 、温度補償された基準電圧は、低温ドリフトで実現できます。

フィードバック

LNFLは、2つの小さなLNFLによって形成される増幅器とバンドギャップコアに確立されます。最初のloop1は、アンプの入力から V までです。 REF 、およびアンプの入力へのフィードバック。もう1つ、loop2は V からのものです REF バンドギャップコアを介してアンプの電流テールに到達し、 V にフィードバックします。 REF 。 loop1の場合、アンプの入力に正帰還と負帰還の二重ローカルループがあります。正のフィードバックループは、Q5、R2、R1、Q1、MP8、およびMXで構成されています。負帰還ループは、Q5、R2、Q2、およびMXで構成されます。正と負のフィードバックループのゲインは次のように導出されます

$$ {A} _ {V、PF} =\ frac {R_ {Trim \ min g}} {R_1 + {R} _ {Trim \ min g} + {R} _2} {g} _ {m、Q1} {r} _ {o、MP8} $$(5)$$ {A} _ {V、NF} =\ frac {R_1 + {R} _ {Trim \ min g}} {R_1 + {R} _ {Trim \ min g} + {R} _2} {g} _ {m、Q2} {r} _ {o、MP8} $$(6)ここで g m 、 Q 1 はトランジスタQ1の相互コンダクタンスです r o 、 MP 8 はトランジスタMP8の出力抵抗であり、 g m Q1とQ2の値はほぼ同じです。負のフィードバックループの効果は正のフィードバックループの効果よりも強いため、loop1はフィードバックループとして動作し、そのループ特性は次のように表すことができます。

$$ {T} _ {\ mathrm {loop} 1} \ approx \ frac {R_1} {R_1 + {R} _ {Trim \ min g} + {R} _2} {g} _ {m、Q1} {r } _ {o、MP8} $$(7)$$ {p} _0 \ approx \ frac {1} {r_ {o、MP8} {C} _1} $$(8)ここで p 0 支配的な極です。 loop2に関しては、パフォーマンスは次のように与えられます

$$ {T} _ {\ mathrm {loop} 2} \ approx \ frac {1 / {g} _ {m、MP8}} {R_1 + {R} _ {Trim \ min g} + {R} _2} $ $(9)$$ {p} _1 \ approx \ frac {g_ {m、MP8}} {C_1} $$(10)ここで g m 、 MP 8 はトランジスタMP8の相互コンダクタンスであり、 p 1 支配的な極です。その結果、LNFLの合計ループゲインは

になります。 $$ {T} _ {\ mathrm {LNFL}} \ approx \ frac {R_1 {g} _ {m、Q1} {r} _ {o、MP8} + 1 / {g} _ {m、MP8}} {R_1 + {R} _ {Trim \ min g} + {R} _2} \ frac {1 + s / {z} _0} {\ left(1 + s / {p} _0 \ right)\ left(1+ s / {p} _1 \ right)} $$(11)式(2)を考慮すると、式(11)は次のように書き直すことができます。

$$ {T} _ {\ mathrm {LNFL}} \ approx \ frac {r_ {o、MP8} \ ln N + 1 / {g} _ {m、MP8}} {R_1 + {R} _ {Trim \ min g} + {R} _2} \ frac {1 + s / {z} _0} {\ left(1 + s / {p} _0 \ right)\ left(1 + s / {p} _1 \ right)} $$(12)ここで z 0 ≈ g m 、 MP 8 / [ C 1 (1 + 1 / ln N )]。 N 以降 =提案された設計では8であり、ゼロ z になります。 0 、極の2倍にほぼ等しい p 1 、LNFLのループ帯域幅を2倍に拡張できます。

GSBLは、電流増幅器、バンドギャップコア、および増幅器によって形成され、PSRRパフォーマンスが向上した自己バイアス方式で回路全体にバイアス電流を供給することができます。 GSBLのループゲインは次の式で与えられます

$$ {T} _ {\ mathrm {GSBL}} \ approx \ frac {K \ left(1/3 {g} _ {m、MP8} \ Big \ Vert 1 / {g} _ {m、MX} \右)} {R_1 + {R} _ {Trim \ min g} + {R} _2} $$(13)ここで g m 、 MX はトランジスタ M の相互コンダクタンスです X 。トランジスタの主な効果 M X V での等価インピーダンスを下げることです REF ループ補正の便利さで。 T GSBL は、提案された設計の1よりも小さく設定されているため、発振を回避できます。

LNFLとGSBLの助けを借りて、生成された基準電圧 V の安定性 REF 、大幅に改善できます。

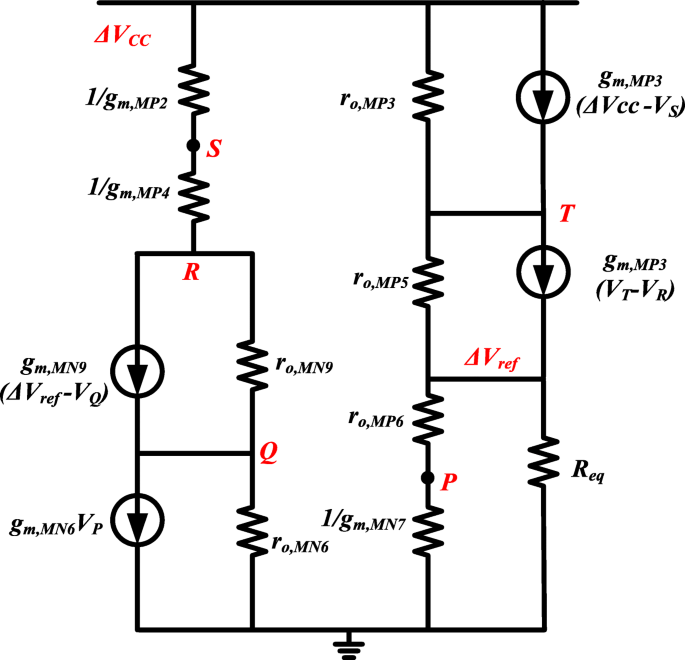

提案された電圧リファレンスのPSRR

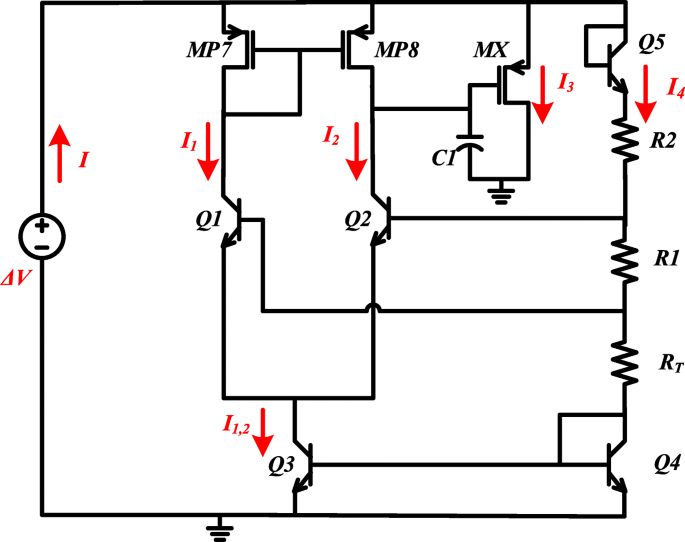

提案された回路のPSRR計算を単純化するために、基準電圧 V によって電力が供給される部品の等価抵抗 REF 、最初に計算されます。この部分の計算図を図3に示します[16]。

R eq 計算図

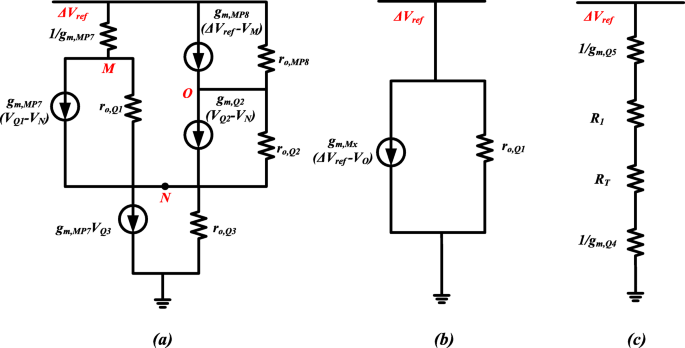

図4aは、回路分岐1、2の等価抵抗計算の小信号モデルを示しています。ここで、電流 I 1 および私 2 それぞれ図3の流れ。次に、等価抵抗 R eq 1,2 、次のように表すことができます

$$ {R} _ {eq1,2} \ approx \ frac {3 {R} _ {eq、4} {r} _ {o、Q1}} {3 {g} _ {m、Q1} {r} _ {o、Q1} \ left({R} _T + {R} _1 + {r} _ {o、Q3} \ right)+ {g} _ {m、Q1} {R} _1 {r} _ {o、 Q1} +3 {R} _ {eq、4}} $$(14)ここで g m 、 Q 1 および r o 、 Q 1 それぞれQ1の相互コンダクタンスと出力抵抗です。 R eq 4 I との分岐の等価抵抗です。 4 。図2に示すMP6のゲート電圧はMP7のドレイン電圧によって決定されるため、ノードMでの電源ノイズ減衰(PSNA)も計算する必要があります。これは次の式で求められます。

$$ {V} _M =\ Delta {V} _ {ref} + \ frac {g_ {m、Q1} {R} _1 {r} _ {o、Q2}} {2 {g} _ {m、MP7 } \ left({r} _ {o、Q2} + {r} _ {o、MP8} \ right){R} _ {eq4}} \ Delta {V} _ {ref} \ approx \ Delta {V} _ {ref} $$(15)ここで r o 、 MP 8 および r o 、 Q 2 それぞれMP8とQ2の出力抵抗です。 g m 、 MP 7 MP7の相互コンダクタンスです。式(15)で主張されているように、電源ノイズはMP6のソースゲート電圧にほとんど影響を与えません。これにより、MP6は高インピーダンス r として機能します。 o 、 MP 6 、アンプとバンドギャップコア部品からのノイズの影響を分離します。

R eq の小信号モデル 。 a R eq1,2 計算図。 b R eq3 計算図。 c R eq4 計算図

I を使用した分岐の等価抵抗 3 図3の図4bは、次のように表すことができます。

$$ {R} _ {eq3} \ approx \ frac {6 {R} _ {eq、4}} {g_ {m、mx} \ left [3 {g} _ {m、Q1} {r} _ { o、Q1} \ left({R} _T + {R} _1 + {r} _ {o、Q3} \ right)+3 {R} _ {eq、4} + {g} _ {m、Q1} {r } _ {o、Q1} {R} _1 \ right]} $$(16)ここで g m 、 Mx Mxの相互コンダクタンスです。 I を使用した分岐の等価抵抗の小信号モデル 4 図3の図4cは、

です。 $$ {R} _ {eq4} \ approx 1 / {g} _ {m、Q5} + {R} _1 + {R} _T + 1 / {g} _ {m、Q4} + {R} _2 $$ (17)したがって、図3の増幅器とバンドギャップコア部品の小信号等価抵抗は

です。 $$ {R} _ {eq} ={R} _ {eq1,2} \ left \ Vert {R} _ {eq3} \ right \ Vert {R} _ {eq4} $$(18)したがって、提案された電圧リファレンスの合計PSRRを図5に示すことができます。PSRRは次の式で求めることができます。

$$ \ frac {\ Delta {V} _ {ref}} {\ Delta {V} _ {CC}} \ approx \ frac {6 {R} _ {eq、4}} {g_ {m、mx} { g} _ {m、mp3} {r} _ {o、mp3} {r} _ {o、mp6} \ left [3 {g} _ {m、Q1} {r} _ {o、Q1} \ left ({R} _T + {R} _1 + {r} _ {o、Q3} \ right)+3 {R} _ {eq、4} + {g} _ {m、Q1} {r} _ {o、Q1 } {R} _1 \ right]} $$(19)g 以降 m r o >> 1は一般的に有効であり、生成された基準電圧に対する電源ノイズの影響は大幅に抑制されます。

PSRRの小信号モデル

結果と考察

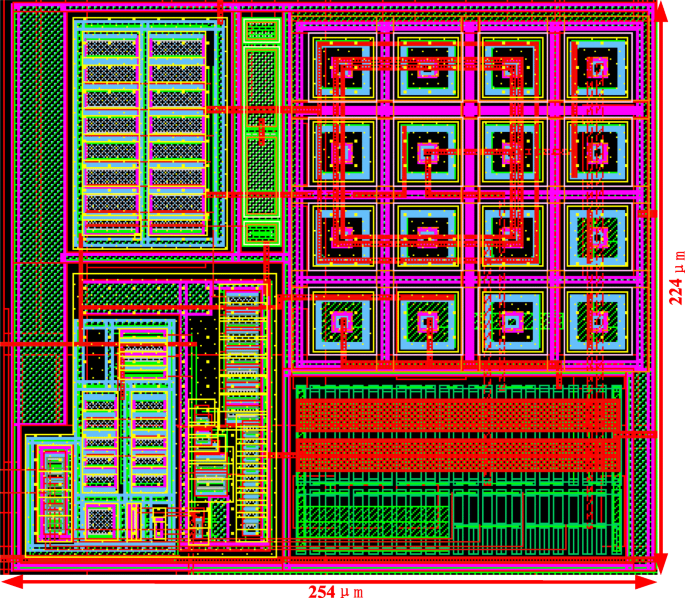

電圧リファレンスは180nmのBCDプロセスで実装され、そのレイアウトは図6に示され、0.05690 mm 2 を占めます。 アクティブエリア。

提案された回路のレイアウト

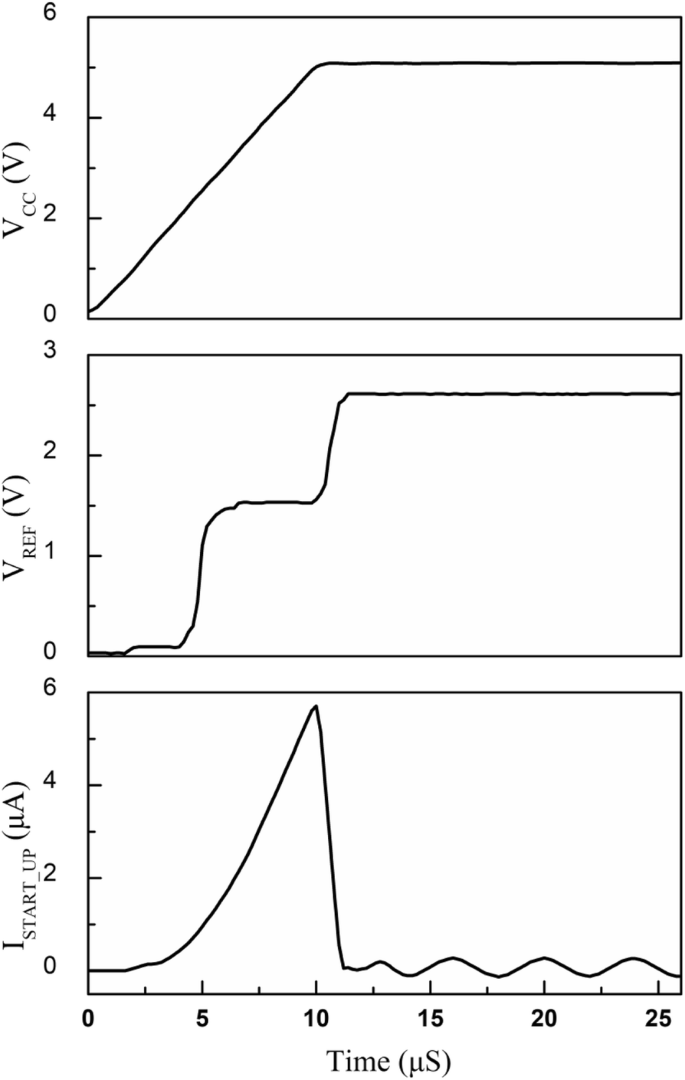

シミュレートされた起動波形を図7に示します。これは、電源電圧の確立を伴う過渡手順を示しています。供給電圧が小さい場合、基準回路全体が完全に動作していません。つまり、起動分岐電流が非常に小さく、基準電圧がゼロに維持されます。電源電圧の上昇に伴い、生成された基準電圧は最初に約2 V で安定します。 BE 図2の増幅器部分の異常動作により、供給電圧が提案されたBGRの最小必要供給電圧を超えると、コアオペアンプが動作を開始し、基準電圧が目的の値にすばやく安定します。さらに、GSBLによる電流供給の代わりに、提案されたSBCSが使用されている間、起動電流は目的の基準電圧でほぼゼロに低下します。起動回路の消費電力は、チップの消費電力のごく一部を占めています。

提案された電圧リファレンスの起動過渡特性

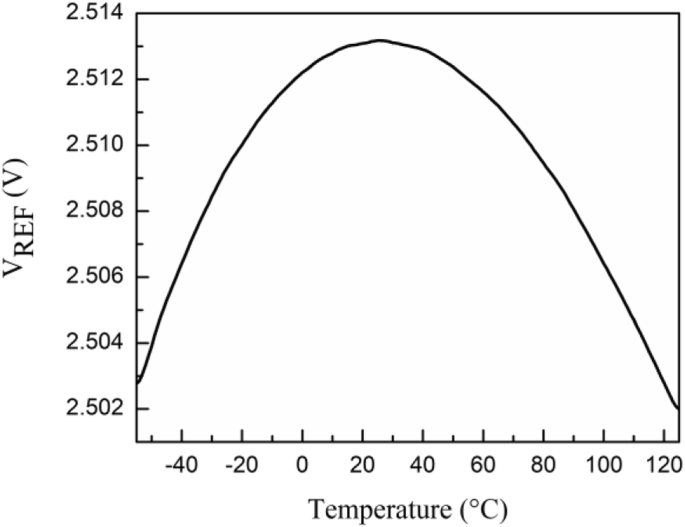

生成された基準電圧 V の温度特性 REF 、を図8に示します。 V の電圧変動 REF −55°C〜125°Cの範囲では11.3 mVであり、25 ppm /°CのTCが達成されます。

生成された基準電圧の温度依存性

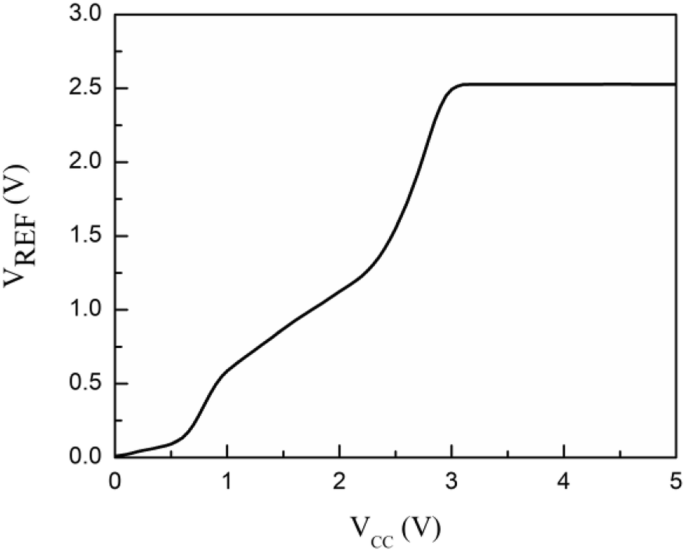

図9は、基準出力電圧のライン感度(LS)を示しています。提案されたBGRは、3 Vの供給電圧、および V で正常に確立できます。 REF 変動は3-5Vの供給電圧内で0.2mVです。これは、0.08‰/ Vの良好なLSが実現されることを意味します。

生成された基準電圧の電源依存性

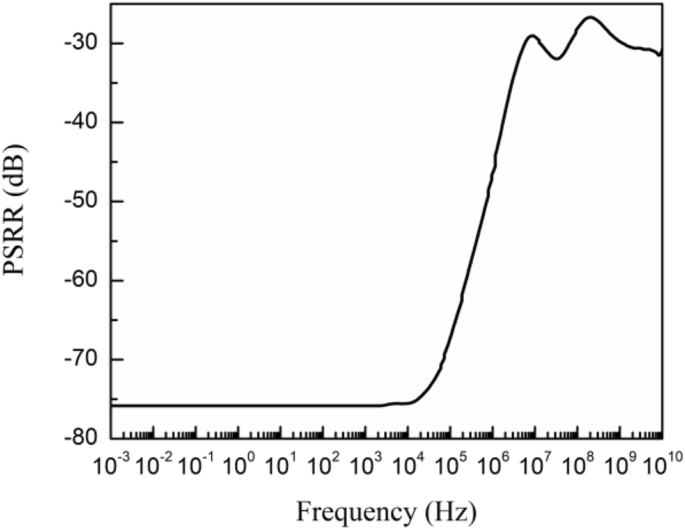

改善されたPSRR性能を図10に示します。これは、76 dBのPSRRを持ち、低周波数および1MHzまでの46dBを超える場合の式(19)の理論結果と一致します。

提案された電圧リファレンスのPSRR特性

R に8ビットトリミングを採用する提案されたBGRには、従来のバイナリトリミング方法が適しています。 トリミング 。これにより、9 mV / LSBのトリミングステップを実現できます。表1は、標準、低速、および高速のケースを含む、異なるプロセスコーナーでの3 -5 Vの供給電圧と-55〜125°Cの温度範囲でのトリミングされた電圧リファレンスのパフォーマンスを示しています。表1に示すように、温度ドリフトは0.6%以内、LSは0.12‰/ V未満、PSRRは71 dB @ 10Hzを上回っています。

<図>表2に、提案された電圧リファレンスの特徴的な要約と、以前に報告されたいくつかの電圧リファレンスとの比較を示します。提案された電圧リファレンスは高い電源安定性を目的としているため、この論文では高次の温度補償は使用されていません。したがって、主に温度または電力の最適化方法に焦点を当てた[11,12,13]のTCは、提案された電圧リファレンスのTCよりも小さくなります。提案された電圧リファレンスのTCは、必要に応じて、文献で報告されている曲率補償方法を使用してさらに最適化できます。提案されたコンパクトな構造により、LNFLとGSBLは、温度に依存しない基準電圧で同時に実現され、表2で最高のPSRRとLSのパフォーマンスを発揮します。

<図>結論

この論文では、高いPSRRを備えた圧縮された自己バイアスBGRを示します。 PTAT電圧は、非対称入力オフセット電圧を備えたオペアンプによって実装され、負の温度電圧が重畳されて、基準出力電圧が生成されます。同時に、LNFLとGSBLの2つのフィードバックループが同じ部品で実現され、温度安定性が向上し、構造の複雑さが軽減されます。これにより、PSRRが高くなり、供給電流の自給自足と電源感度の向上が実現します。

データと資料の可用性

この調査中に生成または分析されたすべてのデータは、この公開された記事に含まれています。

略語

- BGR:

-

バンドギャップリファレンス

- PSRR:

-

電源除去率

- TC:

-

温度係数

- PTAT:

-

絶対温度に比例

- LNFL:

-

ローカル負帰還ループ

ナノマテリアル