Verilog 言語と HDL 言語の簡単な紹介

紹介:

この記事では、VHDL と Verilog について紹介します。また、Verilog モジュールの基本構造を学習し、Verilog の「ワイヤ」データ型とそのベクトル形式に慣れます。また、Verilog と VHDL の基本的な違いについても説明します。

Verilog とは?

Verilog はハードウェア記述言語 (HDL) の一種であり、IEEE 1364 として標準化されています。これは、デジタル回路の設計と検証で使用される、電子回路とシステムの記述に最も一般的に使用されます。

VHDL とは?

VHDL は、電子設計自動化で電子システムの動作と構造を記述するために使用されるハードウェア記述言語 (HDL) の一種でもあり、デジタル電子ハードウェア設計の構造と動作を記述する言語として特に適しています。従来のデジタル回路。

Verilog と VHDL の両方が必要ですか?

先に進む前に、これら両方の言語が必要かどうかについて議論しましょうか?どちらも複雑なデジタル回路の設計に使用される強力なツールですが、使いたいものを自由にマスターできます。ただし、両方の言語の基本的な理解が必要です。

Verilog の進化

Verilog は、1984 年に Gateway Design Automation で設計されました。 1987 年に VHDL が IEEE 標準になり、Verilog が 1995 年までに登場しました。現在、これらはどちらも強力な HDL (ハードウェア記述言語) です。 「Verilog」という言葉は、「検証」と「ロジック」という言葉に由来しています。これは、言語が最初にシミュレーションおよび検証ツールとして使用されたためです。

ここで、いくつかの Verilog の概念について説明します。

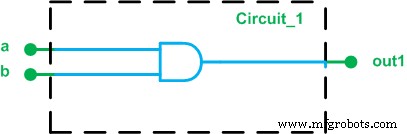

例 1:

この例では、以下に示す回路の Verilog コードを書きましょう。

2 つの入力と 1 つの出力が示され、ポートは 1 ビット幅です。この回路は、2 つの入力からの AND 関数を示しており、out1 ポートで出力が得られます。 Verilog の記述は次のように表示できます。

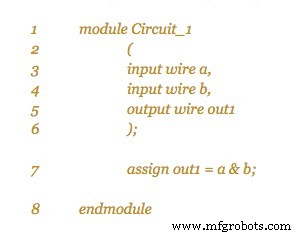

1 行目と 8 行目:

キーワード「module」と「endmodule」は、Circuit_1 を説明するそれらの間の行を指定するために使用されます。

2 行目から 6 行目:

これらの行は、「Circuit_1」のインターフェースとその環境を指定しています。キーワード「input」と「output」は、入力ポートと出力ポートを示します。この後、キーワード「wire」は、デザイン内の物理的な配線を表す Verilog データ型を指定します。モジュールには a、b、out1 の 3 本のワイヤがあります。

7 行目:

この行は、回路の AND 機能をビットごとの AND 演算子「&」で記述しています。キーワード「割り当て;出力ポートに a &b を配置するために使用されます。これは、式が右辺で変化するたびに常にアクティブであるため、連続代入とも呼ばれます。左辺は再評価されます。つまり、その出力は継続的に更新されます。

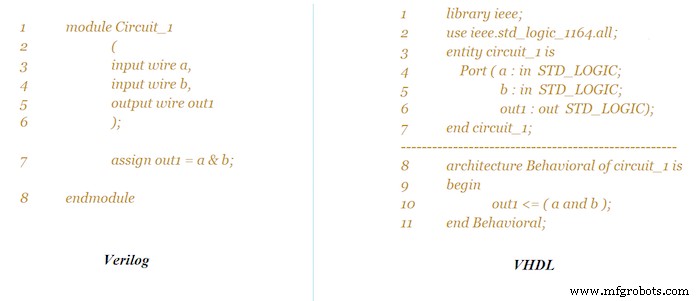

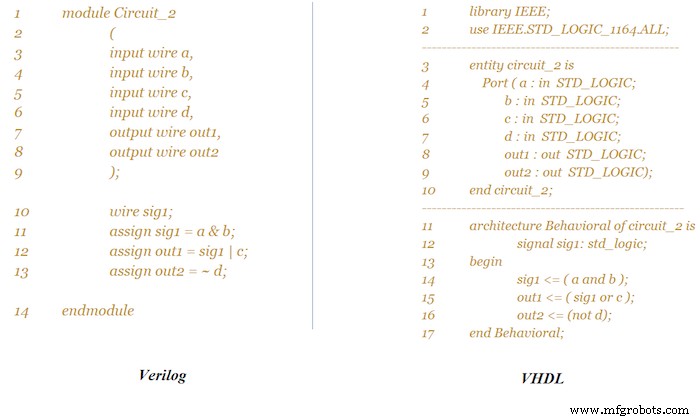

例 1 と VHDL コードの比較:

下の図は、Circuit_1 モジュールの Verilog と VHDL の説明を示しています。

VHDL では、データ型と演算子を定義するいくつかのライブラリを含める必要があります。したがって、VHDL コードの方がより説明的です。ただし、高レベル システムのモデル化など、場合によっては、これが有利な場合もあります。

Verilog の 4 値システム:

Verilog データ型で使用される値は 4 つあります:

<ウル>VHDL std_logic データ型は 9 つの異なる値を取ることができますが、一般的に使用される値は「0」、「1」、「Z」、および「-」です (「-」は不明な値を示します)。

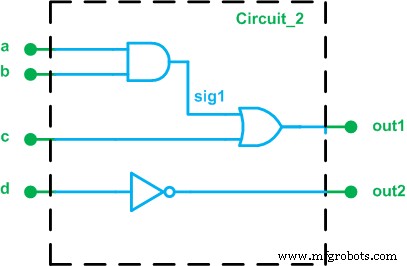

例 2:

次の例では、下の図に示されている回路 (Circuit_2) の Verilog コードを書きましょう。

次の Verilog コードは、示されている回路を説明しています。

使用される要素は前の例と似ていますが、10 行目で内部信号が定義されています。キーワード「wire」は、この接続のデータ型を指定します。ビット演算子「~」は NOT に使用され、「|」は OR 演算に使用されます。ビット単位の演算子「^」は、XOR 演算に使用されます。

次の図は、Circuit_2 モジュールの Verilog と VHDL の両方の記述を示しているため、違いを確認できます。

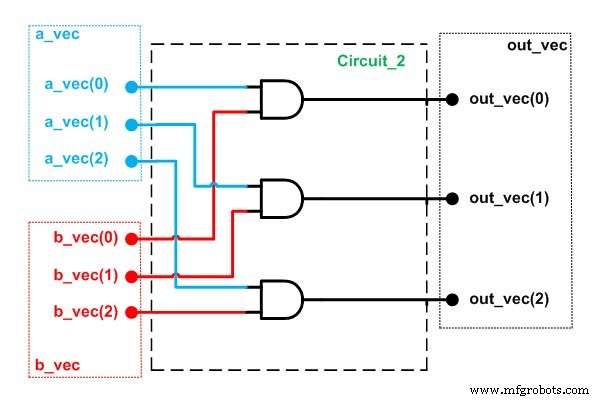

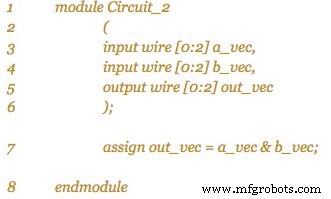

例 3:

3 番目で最後の例として、次の図に示す回路図の Verilog コードを示します。  赤と青の入力ポートが AND 演算子で結合されていることがわかります。結果は出力ポートによって示されます。シグナルをグループ化し、コードをコンパクトにして読みやすいベクトルとして扱うことができます。上記の回路は、Verilog コードを使用して記述できます。リスト 1 のコードを簡単に拡張して、この回路を記述することもできます。

赤と青の入力ポートが AND 演算子で結合されていることがわかります。結果は出力ポートによって示されます。シグナルをグループ化し、コードをコンパクトにして読みやすいベクトルとして扱うことができます。上記の回路は、Verilog コードを使用して記述できます。リスト 1 のコードを簡単に拡張して、この回路を記述することもできます。

ベクトルのインデックス範囲は、示されているように昇順 ([0:2]) または降順 ([2:0]) であることに注意してください。通常、降順形式はエラーが発生しにくいため、代わりに使用できます。

産業技術