PCB レイアウトが電子製品の EMC 性能に与える影響

PCB のアース

• PCB 内部信号への共通コード干渉の影響

プリント回路基板 (PCB) の内部プリント ラインは、基準グランド ボードに関連する寄生パラメータを備えており、機能信号が PCB 内で送信されている場合、回路内の同じネットワーク内の同じ等電位ノードはもはや等電位ではありません。 PCB 内の電流 i はソース エンドから始まり、一連のキャリア リターンを信号ソースに渡し、信号を形成します。さらに、i はインピーダンスの低い経路に沿って流れる傾向があるため、通常はインピーダンスの安定性で変化しません。

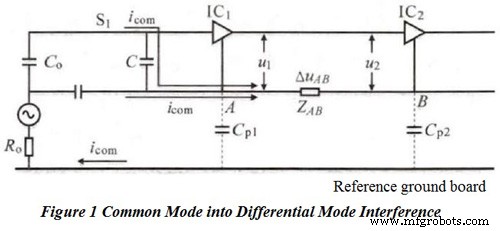

図 1 は、PCB 内でコモン モード干渉がディファレンシャル モード干渉に変換されるプロセスを示しています。私はd icom 中の PCB フロー内の差動モード電流を指します。 は、PCB の外側から基準グランド ボードを通って PCB に流れ込む、または PCB の内側から基準グランド ボードを通って PCB の内側に戻るコモン モード電流を指します。高頻度 icom 2 つのパスがあります。1 つ目は、GND から始まる PCB 内のポイント A からポイント B です。 2 つ目は、ポート S1 から始まるポイント A からポイント B までです。 静電容量 C によって内部の PCB に接続します。接地インピーダンス ZAB ΔuABの生成につながります 、そのため、通常の信号が IC2 に渡されると 、信号に変形が起こり、コモンモード干渉がディファレンシャルモード干渉に変換され、u2 の式に基づいて通常の信号に影響を与えます =u1 -ΔuAB .

したがって、すぐに icom が I/O ポートまたは宇宙放射線を介して PCB の内部に侵入すると、PCB の信号ラインの差動モード フィルタ キャパシタンスは、干渉バイパスを GND に押し付けることができるだけです。この結果の前提条件は、GND は信号の逆流に対して低インピーダンスと見なされ、常に低インピーダンスの方向に電流が流れることです。

• EMC 設計実装の鍵:PCB の接地インピーダンス

高周波信号による EMC の発生の理由は、信号基準レベル GND が低インピーダンスの特性を維持できないことにあります。インピーダンスZGNDの増加に伴い 基準レベルを超えると、信号伝送の品質も低下します。高周波干渉の問題を解決するために、「グランド」に密接に接続されたフィルター、グランド、シールドなどの一般的な方法が EMC 設計で使用されます。

フィルタはコンデンサ対グランドとみなすことができ、X コンデンサを信号基準グランドに接続する構造と、信号を Y コンデンサまたは PCB 内部の別のグランド接続によって金属シェルに接続する構造の 2 つがあります。シールドは、PCB グランドの空間への拡張の結果と見なすことができます。フィルタまたはシールドの目的は、通常の動作信号に流れ込むのを避けるために、高周波コモンモード干渉を低インピーダンスでバイパスさせることです。同様に、グランドのインピーダンスが低い場合を除き、これらの方法はすべて機能しません。

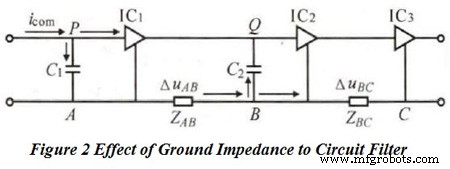

図 2 は、グランド インピーダンスが回路フィルタに与える影響を示しています。 icom IC1のシーケンスに従って流れます →IC2 →IC1 そして点Pに流れると、icom IC1の分岐回路に流れ込みます そしてC1 A 点から B 点に流れる場合、A 点と B 点の間のインピーダンスは ZAB です。 、ポイント P と IC1 の間のインピーダンスよりもはるかに小さい .現時点では、icom ポイント P から A への流れ、IC1 フィルターを実現できます。いつ com が B 点に流れると、B→C、B→Q という分岐回路が発生します。 PCB レイアウトが適切に制御されていない場合、ポイント B と C の間のインピーダンス、つまり ZBC 、ZBC>>ZC2 +ZQ . ZQ ポイントQとIC2の間のインピーダンスを指します . icom IC2 に逆流 C2 を介した入力ポート 元々 IC2 のみに使用されていた静電容量の場合 信号侵入干渉で役割を果たします。

低インピーダンスで基準レベルを作るために、通常は面になるように設計されています。一般的に言えば、長さと幅の比が 5 未満の導体は、工学の分野では低インピーダンスと見なすことができます。印刷された線のインピーダンスは、長さや太さの度合いによって決まりません。従来の PCB 設計原則では、アナログ回路の単一点接地が大いに推奨されているため、デジタル回路の複数点接地の PCB レイアウト原則とデジタル モジュール回路の混合接地は、EMC 問題に対処するためにはもはや有効ではありません。

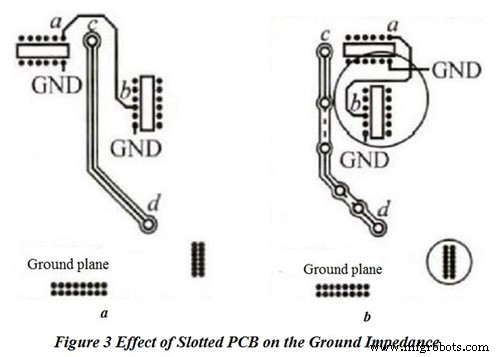

すべての信号のすべての逆流は、低インピーダンスの統合グランドを備えていることを確認する必要があるため、統合グランドプレーンを備えた 4 層または多層基板は要件を満たすことができますが、低コストの単一基板はそうではありません。コストの制限に基づいて 2 層基板を使用する必要がある場合は、PCB 内の信号用に比較的統合されたグランド プレーンを設計する必要があります。実際のアプリケーションでは、PCB のグランド インピーダンスは、その形状と、信号線のスルー ホール、クラック、スロットの両方の影響を受けます。図 3a と 3b はそれぞれ、低インピーダンスのグランド プレーン設計の悪い例と優れた例を示しています。

この図では、すべてのコンポーネントが PCB の前面にあり、グランド プレーンが背面にあります。チップは、前面の印刷線 ab と背面の印刷線 cd を介して接続されます。外部からの高周波コモンモード干渉の圧力の下で、cd によって形成されたスロットは ZGND の増加につながります。 印刷された行の逆流。 ZGND 信号伝送の過程で変動し、信号の品質が低下します。したがって、CD 間の印刷線の層は、PCB レイアウト設計の過程で穴を介して何度も交換できるため、ZGND 減少します。その上、2つのICS 敏感な信号を一緒に配置して、GND をローカルで比較的統合されたグランドプレーンにして、信号伝送の過程で信号が干渉されないようにすることができます。スルーホールを密集して配置しないと、グランドプレーンにクラックが発生し、ZGND のエスカレーションにつながることに注意してください。 .

PCB のスタッキング設計

EMC 設計は 4 層 PCB に最適です。 EMS の観点からは、ローカルに敏感な回路のメタル シェルまたはメタル シェル シールドは、干渉の問題を解決することができます。 EMI の観点からは、4 層基板は放射放出制限の要件を満たさない場合があり、多層基板は高 du の信号を生成できるため、層数を増やす必要があります。 /dt と di /dt 伝送過程でより小さな信号ループ領域を確保し、高速信号に対して低インピーダンスのバックフローを提供します。

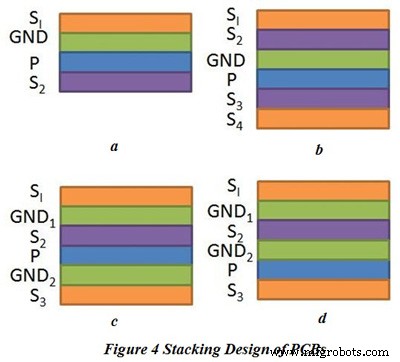

PCB スタッキング設計の基本原則は、高速信号層と電源プレーンをグランド プレーンに隣接して配置することです。図 4 は、4 層および 6 層基板のスタック設計を示しています。 S1

3 6 層 PCB 設計の中で、設計 b が最悪で S2 レイヤは高速信号レイヤである必要があります。 S2 設計 c および d のレイヤは、高速信号レイヤです。最短の信号逆流経路と S2 を確保するために、各信号層がグランド プレーンに近接しているため、設計 c が最適です。 P層はGND1でシールド および GND2 .設計 c と比較して、S3 設計では、d は GND 層から離れており、P は設計 c によって引き起こされる両面効果ではなく、片面効果にしか到達できません。

PCB の等価アンテナ

アンテナの基本的な機能は、無線電波の放射と受信です。放射の過程で、高周波電流は電磁波に変換されます。受信の過程で、電磁波は高周波電流に変換されます。 EMC フィールドでの放射は、主に遠方界放射を指します。アンテナの形成は、RF 信号源と RF 信号源に接続された特定の長さの導体という 2 つの基本的な条件に依存します。工学の分野では、アンテナ効果は導体の長さがl=λ/20の式で表されると考えられています。 l=(λ/4)n のとき、n を自然数としてアンテナ効果が最も大きくなります。

PCB 内で信号が伝送されている場合、インナー ループはループ アンテナと同じ効果があります。ループ面積が大きいほど、アンテナ効果が大きくなります。厳格な PCB ループ制御により、実際に実行可能な差動モード干渉を効果的に阻止できます。ただし、印刷された線が長くなると明らかにロッド アンテナ効果が発生するため、PCB レイアウトのプロセスで相互接続信号の長さを可能な限り短くする必要があります。

ZGND が比較的高い場合 PCB 内で送信される高 du/dt 信号の逆流経路で発生し、コモン モード ドライバ ソース ucom icomで行われます ZGND を通過 、外部に放射する可能性のある、接続された印刷された回線または I/O 安定と一緒に。

PCB のサイズが比較的小さい場合、長さの制限により、内側の印刷ラインがアンテナ放射要件に到達できません。この条件下では、I/O ケーブルはプリント ラインの拡張と見なすことができ、放射要件を満たすことができます。 I/O 安定への直接接続が存在しない場合でも、I/O ケーブル間のクロストーク結合を停止する必要があります。

PCB 内のクロストークとその対策

• PCB 印刷ラインと基準グランド間のカップリング

EMC は主に高周波コモンモード信号について論じているため、PCB の内外で分布パラメータを回避することはできません。 PCB と基準グランドの間で容量結合が発生し、その分布容量は最小スペース内のプレート容量と自然容量で構成されます。プレート容量は PCB のサイズに正比例し、PCB とグランド間の距離に間接的に比例します。最小スペース内の自然静電容量は、PCB 内のプリント ラインの等価直径に正比例します。したがって、PCB がどこに配置されていても、グランドから無限に離れていても、プリント ライン内とグランドの間には常に分布容量が存在します。 PCB では、比較的統合された GND プレーンから基準グランド ボードへの分布容量は約 10pF であり、内部プリント ラインから基準グランド ボードへの分布容量は約 0.001pF から 0.1pF 以下の範囲です。 PCB の中央にあるプリント ラインの分布キャパシタンスは、PCB の端にあるプリント ラインの分布キャパシタンスよりもはるかに低くなります。

• PCB 内のカップリング

を。 PCB内のカップリング理論と信号への影響

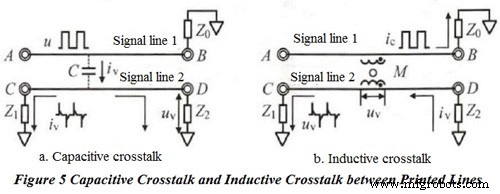

PCB 内部のカップリングは、容量性カップリングと誘導性カップリングで構成され、その理論を図 5 に示します。

この図では、AB と CD の両方が平行に印刷された線で、2 つの線の間に小さなスペースがあります。 Z0 は信号線 1 のキャリアを指し、Z1 は そしてZ2 信号線 2 のそれぞれのキャリアを参照してください。図 5a で、プリント線 AB の信号ピーク電圧を u、信号の立ち上がり時間を Δt、角周波数を ω とすると、Z2 の電圧は uv になります =[Z1 Z2 /(Z1 +Z2 )]cΔu/Δt。 c でも の値が非常に低い場合、Δu/dt の値が非常に高くなり、それらの積を回避することはできません。図 5b では、AB の信号のピーク電流が Ic の場合 、信号の立ち上がり時間は Δt、角周波数は ω、2 つの印刷ライン間の相互インダクタンス m は、誘起電圧が uv である CD を通過します。 =mωic . m の値は非常に小さいですが、信号周波数は増加する可能性があります。したがって、彼らの製品は避けられません。

その結果、容量性結合と誘導性結合の両方が、2 つのプリント ラインの分布パラメータ c または m に関連付けられます。 PCB レイアウト中、c と m の値は、平行線間の距離を大きくすることで減らすことができます。実際の回路では、容量性結合がデジタル回路の大部分を占めており、PCB プレーンが滑らかでない場合、またはスロッティングまたはクラックが存在する場合、誘導性クロストークは容量性クロストークよりも大きな影響を与えます。しかし、PCBの面積が限られている場合、平行線間の距離を大きくするだけではクロストークに対応できません。隣接する 2 つの平行線の間の最小分布パラメータを維持するために、統合された平面設計を射影領域に配置する必要があり、最上部と最下部にグランド層を配置するのが最善です。

b.クロストークを減らすためのシールドアース線の影響

クロストークの程度は、信号周波数、信号の立ち上がり時間、信号線間の距離、駆動ポート、受信ポートの電気的特性、PCB 層の数など、多くの要素によって決まります。プリント配線の下に一体型グランドプレーンを設置することでクロストークを低減し、信号間にシールドグランド線を追加することができます。

PCB レイアウトのプロセスでは、クロストークを防ぐために 2 つの側面が有益です。まず、敏感な内部回路と外部回路を停止する必要があります。第二に、内部回路またはノイズ回路と他の信号とのクロストークを停止する必要があります。実際の PCB レイアウトでは、クロストークのリスクが存在するかどうかを検出するために、PCB の同じレイヤーまたは異なるレイヤー間で詳細なテストを実行する必要があります。

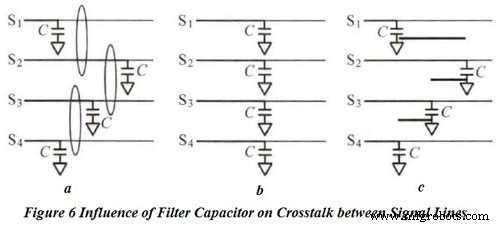

PCB レイアウトの手順では、同じ属性を持ついくつかの信号線は、同じ時間と同じ方向の配線を密度でたどる必要があります。 PCB スペースの制限により、フィルター コンポーネントを同じライン上に配置できないという事実につながる場合、信号間のクロストークが発生する傾向があります。この状況は、以下の図 6 に示されています。

c.エッジ効果に対するシールド接地線の影響

高感度の信号線や du/dt、di/dt の高い信号線を PCB の端に沿って配置すると、PCB の中央に配置した場合よりも EMC リスクが高くなります。寄生容量が大きいと、エッジ信号線が高周波干渉や外部放射を受けやすくなります。

PCB の面積の制限の下で、設計ファイルで 20H 原則に従って PCB をレイアウトすることは非常に困難です。 「パケット」は、干渉と外部放射を減らすために使用できます。パケット ラインは、厚さや形状などの特定の要件を満たす必要はありません。通常、信号線が PCB エッジに近すぎて銅をめっきできない場合、7 ~ 10mil の範囲のグランド線をシールドとして追加できます。

d.デジタル回路とアナログ回路の相互干渉

PCB が高速デジタル回路と低レベルのアナログ信号を保持する場合、通常、PCB レイアウトが悪いと、デジタル ノイズによってアナログ信号にクロストークが発生します。デジタル回路とアナログ回路の相互干渉は、以下の理由により発生します。まず、クロストーク ノイズは寄生容量と寄生インダクタンスによって発生します。第 2 に、電源リップルとデジタル チップ電源の分離が悪いと、電源ノイズが発生します。第 3 に、グランド インピーダンスとシステム グランドの場所がノイズの原因となります。ノイズの問題は、電源、信号、グランドの順に対処する必要があります。

役立つリソース:

• EMI および EMC 自動化ツールの最も包括的な紹介

• PCB EMC 設計で初めての成功を保証する

• EMC 改善のための PCB 分割設計ルール

• PCB無線周波数回路と電磁両立性のための設計

• ラップトップ PCB の EMC を保証する 3 つの設計上の考慮事項

• PCBCart のフル機能 PCB 製造サービス - 複数の付加価値オプション

• PCBCart の高度な PCB アセンブリ サービス- 1個からスタート

産業技術