VHDL でクロック プロセスを作成する方法

VHDL デザインの大部分は、クロック ロジックを使用しています。 、同期ロジックとも呼ばれます またはシーケンシャル ロジック .クロックされたプロセスは、他の入力信号が変化したときではなく、マスター クロック信号によってのみトリガーされます。

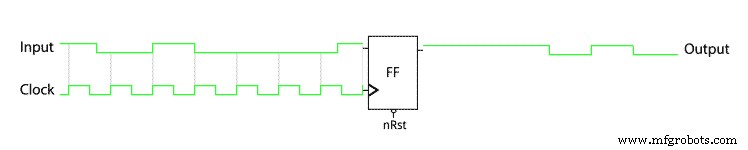

クロック ロジックの基本的なビルディング ブロックは、フリップフロップと呼ばれるコンポーネントです。 .これにはさまざまなバリエーションがあり、このチュートリアルでは、ネガティブ リセットを備えたポジティブ エッジ トリガー フリップフロップに焦点を当てます。

フリップフロップはサンプルアンドホールド回路です。つまり、クロック信号の立ち上がりエッジが到達すると、値が入力から出力にコピーされます。その後、クロックの次の立ち上がりエッジまで、またはリセット信号がパルス化されるまで、出力はサンプリングされた値で安定に保持されます。

このブログ投稿は、基本的な VHDL チュートリアル シリーズの一部です。

クロックされたすべてのプロセスは同時にトリガーされ、入力を一度に読み取ります。同時に、最後の反復からの結果を出力します。クロック信号は、データ フローのタイムステップを効果的に作成します。これにより、設計者は複雑で深いロジックを簡単に作成できます。彼または彼女は、アルゴリズムのアクションをクロック サイクルで発生するイベントに分解できます。

フリップフロップまたはフリップフロップの配列は、レジスタと呼ばれることがあります 、それは同じことです。

クロックされたプロセスのセンシティビティ リストには、通常、クロック信号のみが含まれます。これは、クロックされたプロセスがクロック信号の側面によってのみトリガーされ、他の入力信号によってまったくウェイクアップしないためです。

これは、同期リセットを使用してクロック プロセスを作成するためのテンプレートです:process(Clk) is

begin

if rising_edge(Clk) then

if nRst = '0' then

<reset all output signals here>

else

<main logic here>

end if;

end if;

end process;

エクササイズ

このビデオ チュートリアルでは、VHDL でクロック プロセスを作成する方法を学習します。

フリップフロップ テストベンチ の最終的なコード :

library ieee;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

entity T17_ClockedProcessTb is

end entity;

architecture sim of T17_ClockedProcessTb is

constant ClockFrequency : integer := 100e6; -- 100 MHz

constant ClockPeriod : time := 1000 ms / ClockFrequency;

signal Clk : std_logic := '1';

signal nRst : std_logic := '0';

signal Input : std_logic := '0';

signal Output : std_logic;

begin

-- The Device Under Test (DUT)

i_FlipFlop : entity work.T17_FlipFlop(rtl)

port map(

Clk => Clk,

nRst => nRst,

Input => Input,

Output => Output);

-- Process for generating the clock

Clk <= not Clk after ClockPeriod / 2;

-- Testbench sequence

process is

begin

-- Take the DUT out of reset

nRst <= '1';

wait for 20 ns;

Input <= '1';

wait for 22 ns;

Input <= '0';

wait for 6 ns;

Input <= '1';

wait for 20 ns;

-- Reset the DUT

nRst <= '0';

wait;

end process;

end architecture;

フリップフロップモジュールの最終的なコード :

library ieee;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

entity T17_FlipFlop is

port(

Clk : in std_logic;

nRst : in std_logic; -- Negative reset

Input : in std_logic;

Output : out std_logic);

end entity;

architecture rtl of T17_FlipFlop is

begin

-- Flip-flop with synchronized reset

process(Clk) is

begin

if rising_edge(Clk) then

if nRst = '0' then

Output <= '0';

else

Output <= Input;

end if;

end if;

end process;

end architecture;

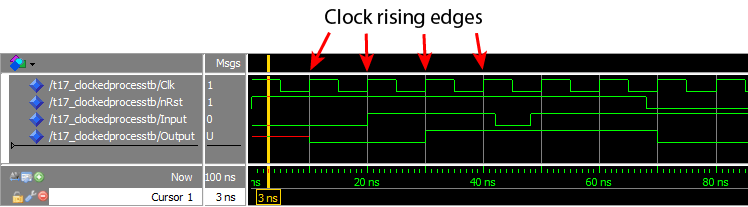

[実行] を押してタイムラインを拡大した後の ModelSim の波形ウィンドウ:

分析

波形から、出力信号はクロック信号の各立ち上がりエッジでのみ更新されることがわかります。入力信号は、クロック信号が「0」から「1」に変化したときにのみサンプリングされます。約 45 ns で始まる入力信号の負のディップは完全に失われます。クロックの 2 つの立ち上がりエッジの間にあるため、出力にコピーされず、無視されます。

このアニメーションは、変化する入力信号とクロック信号に出力がどのように反応するかを示しています。

垂直線は、クロックの立ち上がりエッジに対する入力信号の相対的な関係を示します。

20 ns から始まる入力信号の 1 つの正のパルスに特に注意してください。これはクロックに同期しており、正確に 1 クロック周期の長さです。出力は瞬時に反応せず、1 クロック周期遅れます。

私が VHDL を学んでいたとき、これが特に理解しにくいと感じました。クロックの立ち上がりエッジは入力の立ち上がりエッジと同期しているため、フリップフロップはどのようにして値を選択するのでしょうか?

シミュレーターはタイムステップを使用して予測可能な方法でイベントをモデル化し、信号はゼロ時間で伝播します。フリップフロップは、出力を更新するのとまったく同じタイムステップで入力を読み取るため、入力の古い値を見て、それを出力にコピーします。

VHDL タイムステップの詳細はこちら:デルタ サイクルの説明

これは実際ではないことをこの回答に追加する必要があります 使い方。物理的な世界では、信号が伝播するのに時間がかかります。信号がいつフリップフロップに到達するかは正確にはわかりません。これらの伝搬遅延は、VHDL コードをネットリストに変換するソフトウェア プロセス (配置配線) によって自動的に推定されます。

実際には、立ち上がりクロック エッジの前後の数ナノ秒間、入力を安定に保つ必要があります。

これらの重要な時間は、セットアップ時間とホールド時間として知られています。幸いなことに、これは通常、考慮する必要があるものではありません。純粋にクロック ロジックを使用する場合、これらの問題は VHDL コードをネットリストに変換するソフトウェアによって処理されます。

テイクアウト

- シンクロナイズド リセットを使用したクロック プロセスは、センシティビティ リストにクロック信号しかありません

if rising_edge(Clk)プロセスがクロックの立ち上がりエッジでのみウェイクアップすることを保証します- 同期設計では、アクティブなクロック エッジでのみ発生します

基本的な VHDL クイズに答える – パート 3 »

または

次のチュートリアルに進む »

VHDL