デュアルゲートTFETに基づく無容量1TDRAMのプログラミング最適化

要約

コンデンサの容量が大きく、トランジスタのリーク電流が大きいことは、従来の1つのトランジスタ(1T)-1つのコンデンサ(1C)ダイナミックランダムアクセスメモリ(DRAM)に固有の欠点になっています。最近、トンネル電界効果トランジスタ(TFET)は、オフ状態電流が低く、スイッチング比が高いため、DRAMセルに適用されています。コンデンサレス構造のデュアルゲートTFET(DG-TFET)DRAMセルは、優れた性能を備えています-より高い保持時間(RT)と弱い温度依存性。ただし、TFETDRAMセルの性能はプログラミング条件に敏感です。このホワイトペーパーでは、シミュレーションツールであるSilvaco Atlasを使用して、プログラミングの最適化のガイドラインについて詳しく説明します。 DG-TFET DRAMの書き込み操作と読み取り操作はどちらも、帯域間トンネリング(BTBT)に依存します。書き込み操作中、Gate2によって管理されるBTBTからの穴は、Gate2の下のポテンシャル井戸に格納されます。 「1」を保持している間、ゲート2に小さな負の電圧を印加して、穴を長時間保持します。 Gate1によって制御されるBTBTは、主に読み取り電流に影響を与えます。最適化されたプログラミング条件を使用して、DG-TFET DRAMは、読み取り値「1」と読み取り値「0」のより高い電流比を取得します(10 7 )および2秒を超えるRT。 RTが高いほど、DRAMのリフレッシュレートと動的消費電力が削減されます。

背景

ダイナミックランダムアクセスメモリ(DRAM)は、モバイルおよびコンピューティングシステムの不可欠なメモリセルになりました[1,2,3]。デバイスの形状が縮小するにつれ、コンデンサの量が多いことは、従来の1トランジスタ(1T)-1コンデンサ(1C)DRAMセルに固有の欠点であり、大規模なアプリケーションを制限します。フローティングゲートトランジスタをベースにしたコンデンサレス1TDRAMセルは、メモリの高密度パッケージングにおいて、従来の1T-1CDRAMと比較して潜在的な利点を示しています[4]。フローティングゲートトランジスタでは、基板領域の電荷は、ファウラー-ノルドハイムトンネリングによってフローティングゲート領域に蓄積されます。また、読み取り動作は熱電子放出に依存します[5、6]。これは金属酸化物半導体電界効果トランジスタ(MOSFET)と同じです。その結果、フローティングゲートトランジスタを備えたDRAMの読み出し電流は温度に強く依存します。さらに、熱電子放出により、トランジスタのサブスレッショルドスイング(SS)が60 mV / decを超えるため、高いリーク電流と消費電力が大きな課題になります[7,8,9]。

最近、トンネル電界効果トランジスタ(TFET)は、将来の低電力電気デバイスの有望な候補と見なされています[10、11、12]。 TFETの主な伝導メカニズムは、熱電子放出ではなくバンド間トンネリング(BTBT)です。これにより、サブ60 mV / dec SS、低いオフ状態リーク電流、弱い温度依存性などのいくつかの利点が得られます。 [13、14]。これまでのところ、TFETに関する多くの研究は、主に単一TFETのデバイス性能の研究に焦点を合わせており、いくつかの単純な回路はTFETで構成されています。ただし、高い I on / 私 オフ TFETの機能により、DRAMセルに使用できます[15]。特に、オフ状態のリーク電流が少ないと、読み取り値の「0」電流とDRAMセルの消費電力を減らすことができます。研究者らは、コンデンサレス構造のデュアルゲートTFET(DG-TFET)DRAMを設計しました[16]。 DG-TFET DRAMでは、書き込み動作中の電荷蓄積は、主にGate2によって生成されるチャネルとドレイン間のBTBTに基づいています。同時に、電子のトンネリングは、Gate2の下のチャネル領域での正孔の蓄積を促進します。 Gate1は主に読み取り操作を担当します。 DGTFET DRAMの読み取り電流は、主にソース領域とチャネル領域の間のBTBTに依存します。 DG-TFETDRAMの読み取り電流は温度に弱い依存性があることを実証したいくつかの研究グループがあります。また、DG-TFET DRAMは、ターゲット(64ミリ秒)よりも長い保持時間を取得できます[17]。ただし、プログラミング条件が最適化されていないため、現在の読み取り値「1」と読み取り値「0」およびRTの比率は最適値ではありません。

TFET DRAMの性能、特に「1」の読み取り値と「0」の読み取り値の現在の比率は、プログラミング条件に大きく依存します。 Gate2は、主に書き込み操作中にBTBTに影響を与えます。これは、Gate2の下の電荷とポテンシャルのストレージ領域を支配します。 Gate1は、読み取り動作中にBTBTを制御します。これは、主に読み取り「1」電流に影響を与えます。 Gate1とGate2の両方に適切なバイアスをかけると、DGTFETDRAMの電流比を高くすることができます。プログラミング条件が読み取り電流に与える影響を研究している文献はほとんどありません。この論文では、書き込み、保持、および読み取り操作を含む、詳細なプログラミング最適化ガイドラインを提案します。最適化されたプログラミング条件を適用することにより、DG-TFET DRAMは、最大10 7 の読み取り電流比という最適なパフォーマンスを実現します。 2秒以上のRT。また、最適化されたプログラミング電圧を適用すると、読み取り値の「0」電流は、参考文献[16、18]で報告されている電流よりもはるかに低くなり、消費電力の削減に役立ちます。

メソッド

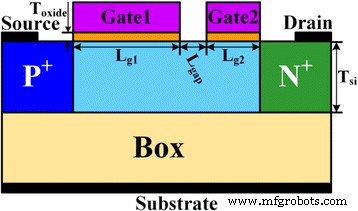

この論文で調査したDG-TFETの構造を図1に示します。両方のP + のドーピング濃度 ソースとN + ドレインは1×10 20 / cm 3 。固有チャネルは、ゲート1とゲート2の2つのセグメントに分割され、ゲート1とゲート2の間に短いギャップがあります。 Gate1とGate2はN + です ポリシリコンとP + それぞれポリシリコン。 P + ポリシリコンGate2は、電荷蓄積のための物理的ウェルを作成および維持し、P + を利用する従来のTFETベースのDRAMを置き換えることができます。 収納エリアとしてのポケット領域。 N + の場合 ポリシリコンGate1、Gate1とGate2の間のアンダーラップ領域の正孔濃度は低く、読み取り操作に役立ちます。したがって、P + ポリシリコンGate2は、N + でありながら、より長い保持を促進できるより深いストレージ領域を持つように選択されています。 ポリシリコンGate1は、読み取り操作中にトンネリングメカニズムを制御するために選択されています[18]。

DG-TFETDRAMセルの概略図。この図は、Gate1、Gate2、ソース、ドレイン、およびチャネルを含む、デュアルゲートTFET(DGTFET)DRAMセルの回路図を示しています。この設計では、ソース領域とドレイン領域はP + です。 ドーピングとN + それぞれドーピング。 Gate1とGate2はN + です ポリシリコンとP + それぞれポリシリコン

シミュレーションでの詳細なデバイスパラメータは次のとおりです。バルクシリコンの厚さ( T si )は20nmです。 Gate1の長さ(Lg 1 )およびGate2(Lg 2 )はそれぞれ400nmと200nmです。ギャップの長さ( L ギャップ )Gate1とGate2の間は50nmです。ゲート酸化物の厚さ(HfO 2 )( T 酸化物 )は3nmです。最適化されたプログラミング条件を表1に示します。プログラミング条件の最適化ガイドラインについては、次のセクションで詳しく説明します。

<図>すべての分析は、非ローカルBTBTモデルを使用してSilvaco-Atlasツールで実行されます[19]。非局所BTBTは、電子と正孔の非局所生成を考慮に入れるため、トンネリングプロセスをより正確にモデル化できます。トンネリングモデルのパラメータは、参考文献[20]の実験データに従って調整されています。さらに、Shockley-Read-Hall再結合、フェルミ統計、ドーピング、電界依存移動度などの物理モデルも使用されます。 [16、18]のアプローチによれば、電子と正孔の寿命は100nsに設定されています。デフォルトの温度は300Kです。

結果と考察

DG-TFET DRAMセルの動作原理は、従来のDRAMの動作原理とは異なります。書き込み操作と読み取り操作はどちらもBTBTに基づいていますが、それぞれ機能が異なります。 「1」の書き込み中のBTBTは、ゲート2の下のポテンシャル井戸にホールを格納するように導きます。これにより、読み取り「1」の電流が増加する可能性があります。読み出し動作中のドレイン電流は、主にソース側付近のBTBTに依存します。さらに、2つのゲートは異なる役割も果たします。Gate1とGate2は、主にそれぞれ読み取り操作と書き込み操作を決定します。

書き込み操作

「1」の書き込み中に、負のバイアスを持つGate2は、Gate2の下のチャネルのエネルギー帯域をブーストします。これにより、バリア幅が減少し、チャネルとドレインの間にBTBTが生成されます。また、この負のGate2バイアスは、Gate2の下に深いポテンシャルを誘導します。チャネルからドレインへの電子のトンネル効果により、Gate2の下のチャネル領域は完全に枯渇し、このポテンシャル井戸に多くの正孔が蓄積されます。 「0」の書き込み中に、正のバイアスを持つGate2は、ドレイン側で再結合するポテンシャル井戸から穴を排出します[21]。

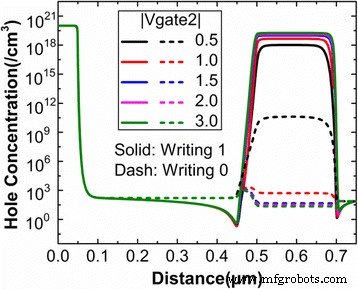

一般に、Gate2電圧の絶対値は、「1」の書き込みと「0」の書き込みで変化しません。図2に、書き込み動作後のGate2電圧による正孔濃度の変化を示します。 Gate2の電圧が0.5Vの場合、ポテンシャル井戸が存在するため、「0」を書き込んだ後の正孔濃度が高くなり、状態「0」に悪影響を及ぼします。 Gate2電圧の絶対値が1Vを超える場合、「0」と「1」の両方を書き込んだ後の正孔濃度に明らかな変化はありません。これは、BTBTが「1」の書き込みで飽和状態にあり、「1」の書き込み中に蓄積されたすべてのホールが「0」の書き込み後にポテンシャル井戸から排出されることを示しています。また、「1」と「0」の書き込みの正孔濃度の違いは非常に明白であり、状態「1」と状態「0」を区別するのに役立ちます。

書き込み操作後のチャネル表面の穴の集中。この図は、さまざまなGate2電圧による正孔濃度の変化を示しています。カットラインは、デバイスの表面でソース領域からドレイン領域まで取得されます。この図で、実線と破線はそれぞれ「1」と「0」を書き込んだ後の正孔濃度を表しています

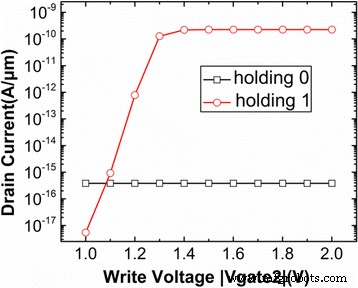

。しかし、書き込み動作中のGate2バイアスは、正孔濃度だけで決定することはできません。図3は、書き込み動作中のGate2バイアスが、保持動作後のドレイン電流に大きな影響を与えることを示しています。保持動作中のプログラミング電圧のセットについては、次のセクションで説明します。図3は、書き込み電圧の絶対値が1.3 Vを超える場合、保持動作後のドレイン電流に明らかな変化がないことを示しています。したがって、-1.3および1.3 Vは、書き込み「1」および書き込み中の最適なGate2電圧と見なされます。それぞれ「0」と書く。

「0」を押しながら「1」を押した後、DG-TFETの電流を流します。この図は、書き込み電圧に対して「0」と「1」を保持した後のドレイン電流の変化を示しています

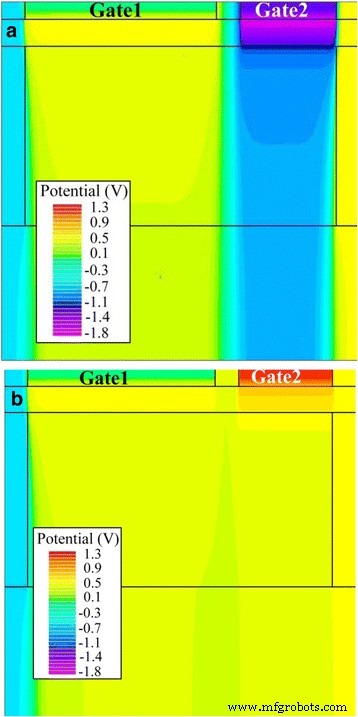

図4a、bはそれぞれ、書き込み電圧の絶対値が1.3 Vの場合に、「1」と「0」を書き込んだ後のポテンシャルの輪郭を示しています。明らかに、「図4aに示すように、1インチ。蓄積された穴は、「1」の書き込み中にこのポテンシャル井戸に保存されます。ただし、「0」を書き込んでいる間、蓄積された穴はこのポテンシャルからうまく逃げます。

a 後の潜在的な輪郭 「1」と b を書く Gate2電圧の絶対値が1.3Vの場合、「0」を書き込みます。 a 、 b それぞれ「1」と「0」を書き込んだ後の潜在的な輪郭。この図の潜在的な等高線は、Gate2電圧の絶対値が1.3Vに設定されている場合に抽出されます

保持操作

保持プロセスは、主に電荷の保持を変更するために使用されます。通常、消費電力を削減するために、保持動作中にゼロバイアスが使用されます[22]。保持操作中、ポテンシャル井戸の深さが減少するため、ポテンシャル井戸に蓄積された穴は徐々に再結合します。したがって、保持操作の最適化の主な目的は、「1」を保持する際の穴の再結合を回避することです。この設計では、Gate2に小さな負のバイアスを適用して、「1」を保持した後にポテンシャル井戸に穴を保持しますが、「0」を保持した後、ポテンシャル井戸は穴を使い果たします。

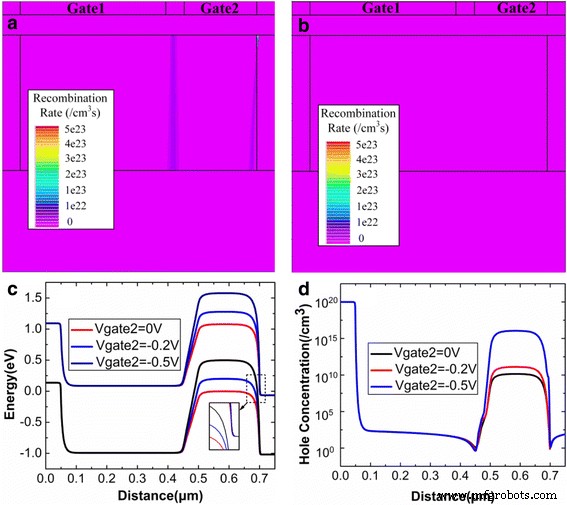

図5a、bに示すように、保持動作中のGate2電圧が負の値(-0.5 V)になると、「1」を保持した後の正孔の再結合がなくなります。穴の再結合を排除することは、「1」を保持している間、穴を保持するのに有益です。小さな負のバイアスがGate2に適用され、ポテンシャル井戸の深さを強化し、穴を長期間保持します。これは、DGTFETDRAMの保持時間に役立ちます。 「0」を保持している間、負のGate2バイアスは、Gate2の下のチャネル領域のエネルギーバンドを引き上げることができます。これにより、ソースとチャネルの間のBTBTから電子がドレイン側に流れるのを防ぐことができます。したがって、負のGate2を使用すると、読み取り値の「0」電流を減らすことができます。ただし、図5cに示すように、負の電圧(-0.5 V)が大きいGate2は、ドレイン側付近のトンネル距離を短くします。このトンネル距離の減少により、図5dに示すように、保持「0」の間に排水側の近くにBTBTが発生し、保持「0」の間にポテンシャル井戸に穴が蓄積しやすくなります。したがって、「0」を保持している間のより負のGate2電圧(-0.5 V)は、状態「0」を低下させます。したがって、「1」を保持しているときと「0」を保持しているときの正孔の再結合とBTBTを排除するために、-0.2Vが保持操作中の最適なGate2バイアスと見なされます。

Gate2電圧が a のときに「1」を保持した後の、DG-TFETDRAMセルの再結合率 0Vおよび b −0.5 V; c エネルギーバンド図と d 「0」を保持した後の正孔濃度。 a 、 b Gate2の電圧がそれぞれ0Vと-0.5Vに設定されている場合に、「1」を保持した後の再結合率。 c ソース領域からドレイン領域までのデバイスのエネルギー帯域。 d 「0」を穴あけした後のデバイスの穴濃度。エネルギーバンドと正孔濃度は、ゲート酸化物の下3nmで抽出されます

読み取り操作

続いて、読み取り操作の最適化についても調査します。読み取り操作は、P + 間のBTBTに強く依存しています。 ソースとチャネル。 「1」の読み取り中、Gate1は主にソース側でBTBTを促進しますが、高電圧のGate2は、チャネルからドレインへの電子の流れに抵抗するエネルギー障壁を低下させます。ただし、「0」の読み取り中は、電圧の小さいGate2が、チャネルからドレインに電子が流れるのを防ぐことができる必要があります。したがって、Gate1とGate2の両方の電圧の最適化は、読み取り操作にとって非常に重要です。

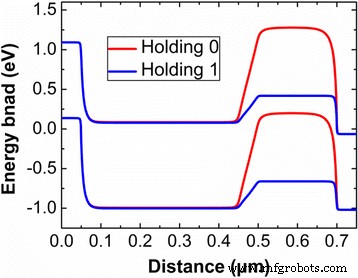

図6は、「1」を押した後と「0」を押した後のさまざまなエネルギーバンド図を示しています。 「1」の読み取り中と「0」の読み取り中は、ゲート側に同じ電圧が印加されます。読み取り動作中は正のゲートバイアスが使用されるため、「1」または「0」を読み取るたびにエネルギー帯域が下げられます。 「0」を保持した後のGate2の下のチャネルのエネルギーバンドは、「1」を保持した後のエネルギーバンドよりも高く、このエネルギーバンドは、「1」を読み取ったときよりも「0」を読み取ったときの方が高くなります。 Gate2の下のチャネルのエネルギーが高いと、ドレイン側に流れる電子に抵抗する効果的なバリアが作成され、読み取り値の「0」電流が減少します。

a 後のエネルギーバンド図 「1」と b を押したまま 「0」を押したままにします。 a 、 b それぞれ「1」と「0」を押した後のデバイスのエネルギーバンド。エネルギーバンドは、ゲート酸化物の下3nmで抽出されます

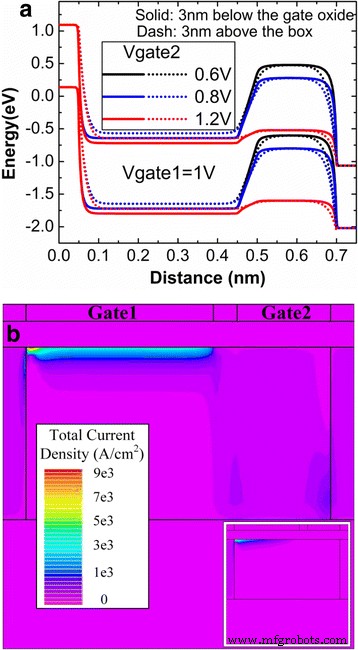

読み取り動作中は、ドレイン電流をDG-TFETで読み取ることができるように、ドレインバイアスが1Vに設定されます。まず、Gate1の電圧を1 Vに保ちながら、Gate2のバイアスを変更して、最適なGate2の電圧を選択します。 Gate2電圧は主に読み取り値「0」の電流に影響を与えるため、Gate2電圧の最適化は読み取り値「0」メカニズムによって分析されます。図7aは、「0」を読み取った後のGate2電圧によるエネルギー帯域の変化をプロットしたものです。 Gate2の電圧が低い場合(0.6または0.8 V)、Gate2の下のチャネルは完全に空になります。ただし、Gate2の電圧が1.2 Vに上昇すると、Gate2の下のチャネルのプルダウンエネルギーバンドは、電子がドレイン側に流れるのを防ぐ効果的なバリアを作成できません。図7bとその挿入図は、それぞれ、Gate2電圧が1Vと0.8 Vの場合に「0」を読み取った後の合計電流密度を示しています。明らかな電流密度は、Gate2電圧が1 Vの場合、Gate2の下のチャネル領域で明確に確認できます。より高い読み取り値の「0」電流を発生させます。したがって、0.8 Vは、読み取りプロセスに最適なGate2電圧と見なされます。

a エネルギーバンド図と b 「0」を読み取った後の総電流密度。 a 、 b それぞれ「0」を読み取った後のエネルギーバンドと総電流密度。エネルギーバンドは、ゲート酸化物の下3nmで抽出されます

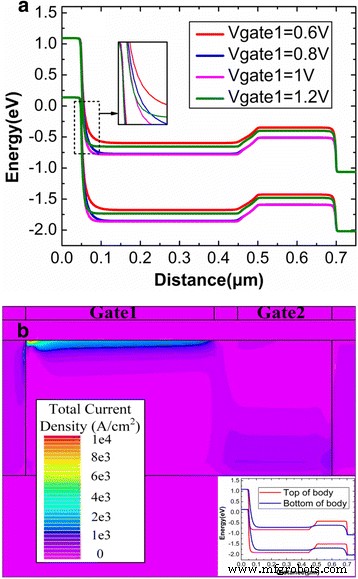

最後に、Gate1バイアスの最適化も実行されます。図8aは、Gate1電圧によるトップエネルギーバンドの変化を示しています。ソース側のBTBTバリア幅は、Gate1電圧の増加とともに徐々に減少しますが、Gate1電圧が1 Vを超えると、この減少傾向は飽和し始めます。また、Gate1電圧が1 Vの場合、「0」の読み取りに重大な影響を与えることはできません。 」の動作。これは図7bで示されています。したがって、1Vは読み取り動作中の最適なGate1バイアスと見なされます。

a エネルギーバンド図と b 「1」を読み取った後の総電流密度。 a 、 b それぞれ「1」を読み取った後のエネルギーバンドと総電流密度。エネルギーバンドは、ゲート酸化物の下3nmで抽出されます

上記の分析により、深ポテンシャル井戸は、「1」を書き込んだ後、Gate2の下のチャネルの上部にのみ形成されます。したがって、Gate2の下のチャネル領域では、チャネルの上部のエネルギーバンドは、チャネルの下部のエネルギーバンドよりもはるかに高くなります。これは、「1」の読み取り中にGate2の下のチャネルの上部にバリアがあることを示しています。図8bの挿入図は、「1」を読み取った後のチャネルの上部と下部の両方でのエネルギーバンドをプロットしています。チャネルの上部にあるGate1とGate2の間に高いチャネルバリアが存在することが明確にわかりますが、このバリアはチャネルの下部には存在しません。したがって、伝導経路は、「1」の読み取り中、Gate1の下のチャネルの上部とGate2の下のチャネルの下部にあります。これは、図8の電流密度によって明確に示されます。

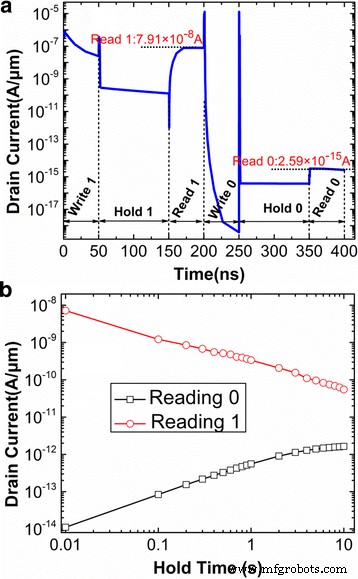

上記の最適化されたプログラミング条件を適用した場合のDG-TFETDRAMセルの過渡応答を図9に示します。書き込み時間と読み取り時間の両方が50nsに設定され、保持時間が100nsに設定されています。図9aでは、「1」の読み取り値と「0」の読み取り値の現在の比率は10 7 と高くなっています。 、10 2 よりはるかに高い 〜10 3 参考文献[16、18、23]。さらに、保持時間が10秒に増加しても、電流比は10を超えます。参考文献[16]では、保持時間が2秒に増加すると、電流比は約10になります。したがって、DG-TFETのRTはプログラミング条件が最適化されたDRAMは2秒より長くなっています。したがって、最適化されたプログラミング条件により、DG-TFET DRAMセルは、より高い読み取り電流比だけでなく、より大きなRTも取得できます。さらに、最適化されたプログラミング電圧での読み取り「0」電流は、リファレンス[16、18、22、23]の読み取り電流よりもはるかに少ないため、低電力アプリケーションに対応できます。

a 操作のシーケンスにおける一時的なドレイン電流。 b 保持時間による読み取り電流の変化。 a 書き込み、保持、および読み取り操作中のDGTFETDRAMセルの過渡電流。 b 異なる穴あけ時間での「1」の読み取りと「0」の電流の読み取りのバリエーション

結論

DG-TFET DRAMのプログラミング条件の詳細な最適化ガイドラインは、Silvaco-Atlasシミュレーションツールを使用してこの論文で提案されています。 「1」の書き込み中に、負の電圧(-1.3 V)のGate2がポテンシャル井戸を作成し、チャネルとドレイン間のBTBTにより、このポテンシャル井戸に正孔が蓄積されます。 「0」の書き込み中、正の電圧(1.3 V)のGate2は、ポテンシャル井戸から穴を逃がします。保持動作では、ゲート2に小さな負の電圧(-0.2 V)を印加して穴を保持します。これにより、読み取り値の「1」電流を改善できます。 「0」を保持した後、Gate2の下のチャネルのバリアは、ドレイン側に向かって流れる電子に抵抗して、読み取り「0」電流を減らすことができます。読み取り動作を最適化するために、読み取り中にソース側でBTBTを強化するために、より大きなGate1電圧(1 V)が主に使用されます。一方、読み取り中にドレインに向かって流れる電子に抵抗するために、適切なGate2電圧(0.8 V)が使用されます。 「0」。最適化されたプログラミング条件により、DG-TFET DRAMはより高い電流比(10 7 )を取得します。 )「1」の読み取りから「0」の読み取り、および2秒を超える保持時間。また、読み取り値が非常に低い「0」電流は、消費電力の削減に役立ちます。

ナノマテリアル

- リモート監視、リモートプログラミング、予知保全のメリット

- マルチコアプログラミングとデバッグの課題をマスターする

- Atmel Studio7でのATmega328PとATtiny45のブレッドボードとプログラミング

- 組み込みCプログラミング言語を学ぶ:Unionデータオブジェクトを理解する

- 建設現場でのIoTベースのテクノロジーの活用

- 人間の心拍に基づく生体認証セキュリティシステム

- コメント:ロボットプログラミングの方法を理解する

- プラント自動化の設計と実装プロセス

- 空欄を埋める CNC プログラミング演習 複数の円弧

- 空欄を埋める CNC プログラミング フライス加工の演習

- 空欄を埋める CNC プログラミング演習