Pt / Nd:SrTiO3接合におけるマルチレベル抵抗スイッチングメモリとメモリ状態依存光起電力に関する研究

要約

Pt / Nd:SrTiO 3 (STO)/ Inデバイスは、ショットキー接触Ptおよびオーミック接触In電極をNdドーピングを施した単結晶STO上に堆積させることによって製造されました。 Pt / Nd:STO / Inデバイスは、マルチレベルの抵抗スイッチング(RS)メモリとメモリ状態に依存する光起電力(PV)効果を示します。これらは、適用されるパルス幅または大きさによって制御できます。 RSとPVはどちらも、Pt / Nd:STOインターフェースで、高さと幅の両方で、バイアスによって引き起こされるインターフェースバリアの変調に関連しています。結果は、RS / PV効果と印加電界によってトリガーされるNd:STOインターフェースの変調との間に強い関係を確立し、複数の不揮発性メモリ状態を非破壊的に検出するための開回路電圧を使用することによって新しいルートを提供します。

背景

SrTiO 3 (STO)は、大きなバンドギャップ(3.2 eV)の絶縁体です。広い温度範囲での単純な立方晶構造から、モデルペロブスカイト材料と考えられています[1]。 STOは豊富な光電性能を備えており、ドナー型またはアクセプター型の遷移金属をドープすることで直接操作できます。 STOシステムの適用範囲は非常に広い[2、3]。最近、STOシステムは抵抗変化型メモリ(RRAM)を構築するための良い候補と見なすことができる抵抗変化型(RS)現象のために大きな科学的注目を集めています[4、5]。

STOに基づくRSデバイスは、通常、金属/ STO /金属構造です。 STOシステムのRS特性、つまりアクセプターからドナーをドープしたSTOまで、広く研究されてきました。スイッチング動作を説明するために、さまざまな物理メカニズムが提案されています。アクセプタードープ(例えば、FeおよびCr)STOの場合、研究は結晶バルクの特性変化を強調します。RSは、転位に沿った酸素空孔の高速輸送のいずれかである、電場駆動の酸素空孔の移動に起因します。または高い電気的ストレス下での酸素空孔配列の形成[6,7,8,9,10,11]。一方、ドナードープ(Nbなど)STOをベースにしたRSデバイスでは、金属とn型Nb:STOのショットキー型接触が必要であり、多くの研究で強調されています。ただし、一部の報告では、RSを金属/ Nb:STO接合の電子空乏層の変化と関連付けています。これは、薄い界面層内の酸素化学量論[12、13、14]または公称陽イオン化学量論からの逸脱によって引き起こされます。表面近くの領域[15、16]といくつかの報告では、RSプロセス中、界面バリアは変化しないままであると示唆されていますが、導電性フィラメントが抵抗変化に重要な役割を果たしています[17、18、19]。

以上の点から、ドナー型STOの切り替えメカニズムについてはコンセンサスが得られていないことは明らかである。これまでのところ、インターフェースとバルク抵抗の変化に関する2つの見方が共存しています。 RSの具体的な理由としては、まだ多くの物理的メカニズムが報告されています。不明確な物理的メカニズムは、STO材料に基づくRRAMの進歩の妨げになっています。 RSメカニズムを明らかにし、ドナー型STOシステムに基づくRRAMデバイスを開発するには、さまざまな金属ドープSTO材料を研究することが有利です。

STOの電子輸送特性は、遷移金属をドープすることで変調できます[20]。薄膜と比較して、単結晶は全領域にわたって均一な特性を持ち、確立された欠陥の物理学と化学を持っています。これまで、RSデバイスで報告されたNb元素を含むドナードープSTO単結晶のみが見つかりました。 NdドープSTO単結晶(Nd:STO)の場合、Sr 2+ のイオン半径 、Ti 4+ 、およびNd 3+ (Nd 2+ )はそれぞれ0.118、0.0605、0.0983(0.129)nmであり、Nd 3+ Sr 2+ を簡単に置き換えることができます Ti 4+ ではなく Nd 3+ 間の半径が類似しているため およびSr 2+ [21]。この置換部位は、n型Nb:STOとは異なります。したがって、Nd:STO単結晶はドナードープ材料であり、n型導電率であり、後でホール効果によって認定されます。 Nd:STO単結晶はRS用の新しいn型STOであり、これまでに報告された作品は見つかりませんでした。

光起電力(PV)効果は内部電界に関連していることが一般的に知られています[22、23、24、25、26]。したがって、RSが主に金属とn型STO界面近くの空乏層によって決定される場合、PV効果はメモリ状態に依存すると予想されます。逆に、RSが導電性フィラメントによって誘導される場合、PVはメモリ状態とは無関係です。この作業では、n型Nd:STO単結晶上にショットキー接触Ptおよびオーミック接触In電極を作製しました。 Pt / Nd:STO / Inデバイスのスイッチングメカニズムを明らかにするために、RSメモリとPV効果を一緒に研究しました。興味深いことに、結果は、Pt / Nd:STO / Inデバイスがマルチレベルメモリとメモリ状態制御のPV効果を持ち、スイッチングバイアスによって変調できることを明確に示しています。この結果は、RSとPVの共通のメカニズムが、キャリアの注入とトラップまたはデトラップによって引き起こされるPt / Nd:STOインターフェイスバリアの変調に関連していることを示唆しています。

メソッド

サイズが5mmの単結晶Nd:STO(100)× 5 mm × 基板として、0.05 wt%のNdドーピングを含む0.5mmを選択しました。 In電極(オレンジ電極)をNd:STOの粗い表面に直接押し付けて、オーミック接触を形成しました。直径0.1mmのPt電極を、シャドウマスク(青い電極)を介してNd:STO単結晶にスパッタリングしました。 2つの近接したPt電極間の距離は0.5mmでした。図2aの挿入図は、Pt / Nd:STO / InおよびIn / Nd:STO / Inデバイスの構成を示しています。電流-電圧(I-V)およびRS特性は、Keithley 2400SourceMeterで測定されました。正の電界は、InからPt電極に流れる電流として定義されます。

ホール効果は、Ndドーピングによって誘発されるキャリア濃度を調査するために、EcopiaHMS-3000ホール測定システムを使用して実行されました。 STOの結晶構造は、CuKα線を使用したX線回折(XRD、Bruker、D8-Advance)によって調べられました。ラマン散乱測定は、励起源として波長632.8 nmの可視レーザー光を使用して、共焦点マイクロラマン分光計(レニショーR-1000)で実行されました。

結果と考察

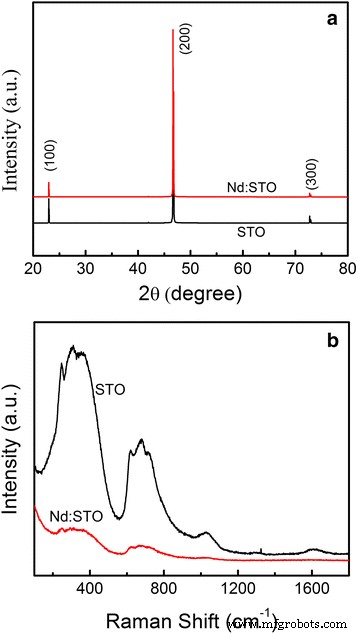

図1aは、ドープされていないSTOおよびNd:STO単結晶のXRDパターンを示しています。すべてのピークはペロブスカイト相に対応しており、格子定数a≈3.905Åの立方空間群Pm3mにインデックスを付けることができます。ピークは、Nd注入後に観察可能な変化を示さず、Ndドーピングがバルク構造にほとんど影響を与えないことを示しています。ドープされていないSTOおよびNd:STO単結晶のラマンスペクトルを図1bに示します。ドープされていないSTOのラマンスペクトルは、200〜400 cm -1 を中心とする、2次散乱に由来する2つの異なる広帯域を示しています。 および600〜800 cm -1 理想的な立方ペロブスカイト構造に属しています。これらの2つのバンドの位置は、公開されている文献[27、28]と一致しています。 Nd:STOの2次広帯域が減少した幅の広い線も観察され、Ndドーピングによって誘発された局所的な無秩序の結果として中心対称性が弱いことを示しています。 XRDパターンと比較すると、ラマン結果は、Nd:STO単結晶の表面にいくつかの構造欠陥が存在することを示しています。これは、Ndドーピングによって引き起こされるはずです。

a XRDパターンと b 非ドープSTOおよびNdドープSTO単結晶のラマンスペクトル

ドープされていないSTO単結晶は絶縁材料であることが一般的に知られています。 STO単結晶の電気的特性に対するNdドーピングの影響を調査するために、ホール効果を測定しました。ホールの結果は、Nd:STO単結晶がn型導電率であり、キャリア濃度が約2 ×であることを示しています。 10 19 cm -1 。このn型導電率は、Nd 3+ の置換に起因する可能性があります。 Sr 2+ に サイト。

図2aの挿入図は、In / Nd:STO / InおよびPt / Nd:STO / Inデバイスの概略図を示しています。 私 – V In / Nd:STO / InデバイスとPt / Nd:STO / Inデバイスの両方の特性が、それぞれ図2a、bにプロットされています。掃引電圧は、50mAのコンプライアンス電流で0V→5V→0V→− 5V→0Vとして印加されました。 In / Nd:STO / Inデバイスには線形の I があります – V 曲線(図2aに示す)であり、プレスされたIn電極とNd:STO単結晶の間に良好なオーミック接触を示しますが、RS効果は現れませんが、Pt / Nd:STO / Inデバイスは可逆的なRS特性を示します。図2b。印加電圧が高くなると抵抗遷移が発生し、遷移方向は印加電圧の極性に依存します。印加電圧が低下すると、高抵抗状態と低抵抗状態(HRSおよびLRS)が維持され、形成後の抵抗状態が安定して不揮発性であることを示します。大きな私 – V ヒステリシスは、Pt / Nd:STO / Inデバイスにメモリプロパティがあることを示しています。プロトタイプのダイオードの動作は、ショットキー障壁がPtおよびn型Nd:STOインターフェースで形成され、Pt / Nd:STO / Inデバイスの抵抗を支配することを示しています。したがって、Pt / Nd:STO / InデバイスのRS効果は、PtとNd:STO単結晶の間のショットキー界面に由来すると簡単に結論付けることができます。この結果、RSはショットキーインターフェースに依存しており、n型Nb:STO単結晶に関する報告された研究と一致しています[29]。

私 – V a の特徴 In / Nd:STO / Inおよび b Pt / Nd:STO / Inデバイスの電圧範囲は0V→5V→0V→− 5V→0V、コンプライアンス電流は50mAです。挿入図はデバイスの概略図を示しています

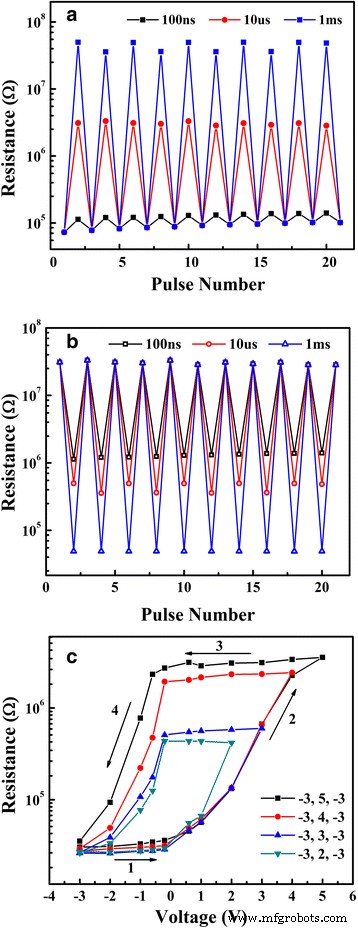

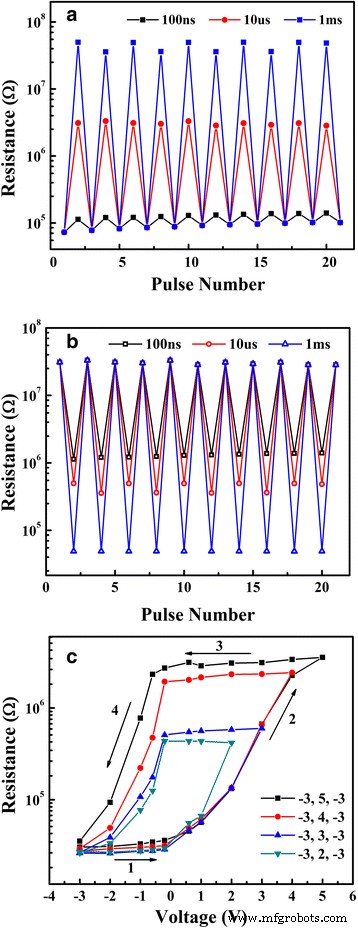

マルチメモリでのPt / Nd:STO / Inデバイスの適用の可能性を評価するために、抵抗状態に対するパルス幅と振幅の影響を調査し、図3a〜cに示しました。デバイスは、最初に100ms幅の-5VパルスによってLRSに設定され、次に100 ns、10μs、および10msのさまざまなパルス幅の+ 5-Vパルスによって適用されました。抵抗は0.1Vで読み取られました。図3aに示すように、LRSから中間抵抗状態またはHRSへの対応する抵抗遷移が達成されました。図3bは、反対の極性のパルスによって誘導されたHRSからLRSへの連続したRSサイクルを示しています。結果は、マルチレベル抵抗が異なる幅のパルス電圧によって得られることを確認します。各抵抗状態の保持特性をさらに調査したところ、抵抗の大きさに大きな変化は見られませんでした(追加ファイル1:図S1に示されています)。図3cは、パルス電圧によって制御される一般的な不揮発性抵抗変化型メモリループを示しています。 Pt / Nd:STO / Inデバイスは、最初に-3 VのパルスによってLRSに設定され、次にパルス電圧を+ 2 V(または+ 3、+ 4、および+ 5 V)にスイープし、-3に戻しました。パルス幅100msのV。抵抗は0.1Vで読み取られました。パルスの大きさを調整することで、一連の中間抵抗状態を実現できます。図3a–cから、パルス幅または大きさを調整することにより、Pt / Nd:STO / Inデバイスのマルチレベル抵抗状態を実現できるという結果が得られました。これは、デバイスがメモリスタとして動作することを示しています[23、30 ]。

連続したRSサイクル a LRSからHRSおよび b HRSからLRSへ。デバイスは、最初に100ms幅の-5V(+ 5 V)パルスによってLRS(HRS)に設定され、次に100 ns、10μsのさまざまなパルス幅の+ 5 V(-5 V)パルスによって適用されました。それぞれ10ミリ秒。 LRS(HRS)から中間抵抗状態またはHRS(LRS)への対応する抵抗遷移。 c R – V パルス電圧によって制御されるヒステリシスループ。 Pt / Nd:STO / Inデバイスは、最初に-3 VのパルスによってLRSに設定され、次にパルスを+ 2 V(または+ 3、+ 4、および+ 5 V)にスイープし、-3Vに戻しました。 100msのパルス幅で。すべての抵抗は0.1Vで読み取られました

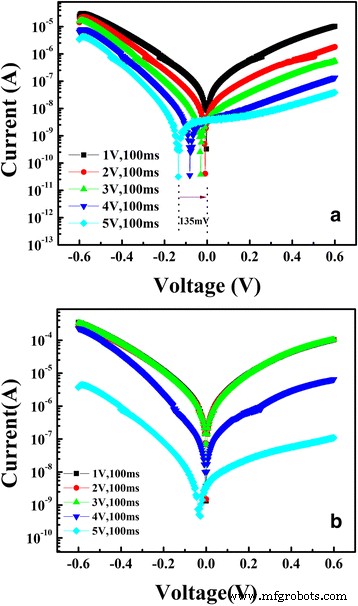

電荷キャリアの光励起は、照射された波長が活物質の光学バンドギャップと一致するときに発生することが一般的に知られています。生成された電子と正孔は内部電界によって分離され、PV効果につながります[23、24、25]。 Pt / Nd:STO / Inデバイスの場合、マルチレベルメモリ状態が主にPt / Nd:STOインターフェイス近くの空乏層によって決定される場合、PV効果はのメモリ状態に依存すると予想されます。端末。逆に、RSプロセス中に空乏層が変化しない場合、PVはメモリ状態とは無関係です。さらに興味深いことに、Pt / Nd:STO / Inデバイスのメモリ状態に依存するPV効果が見つかりました。図4a、bは、 I を示しています – V 明るい照明と暗い場所で100ms(LRSから中間抵抗状態およびHRSに切り替える)で+1から+5 Vまでの一連のパルスで切り替えた後の、低バイアス領域(− 0.6〜 + 0.6 V)の曲線、 それぞれ。光の照明の下で、 I – V HRSの曲線は、電圧軸に沿って顕著なシフトを示し、開回路電圧(Voc)(ゼロ電流での電圧)は約135mVと高くなっています。一連の中間抵抗状態に対応して、Vocはデバイス抵抗の減少とともに徐々に減少し、LRSでは無視できるほど小さくなります。 I ではほとんどシフトが見られませんでした – V 暗闇で測定された曲線。同様の結果がHuらによって得られました。 [23]。さらに、Vocの試験方法がShangらによって報告されました。 [24、25、26]。この方法によれば、VocはLRSとHRSでさらに測定されました。予想どおり、電圧の上昇は光の照明によって発生し、Vocは接合抵抗に依存します(追加ファイル1:図S2を参照)。上記の結果は、Vocの大きさがPt / Nd:STO / Inデバイスのメモリ状態に依存することを証明しています。

私 – V aの下で100ms(LRSから中間抵抗状態およびHRSへの切り替え)で+1から+5 Vまでの一連の電圧パルスで切り替えた後の低バイアス領域(-0.6から+ 0.6 V)の曲線 光の照明と b それぞれ暗い

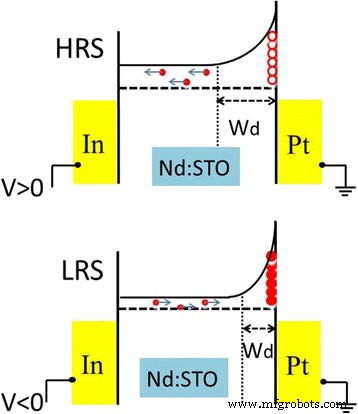

Pt / Nd:STO / Inデバイスのマルチレベルメモリおよびメモリ状態に依存するPV効果は、メモリ状態が主にPt / Nd:STOインターフェイス近くの空乏層によって決定されることを明確に示唆しています。言い換えると、Pt / Nd:STOインターフェース付近のショットキー障壁の幅と高さは、掃引電圧によって変調されます。図1bのラマン結果によると、Nd:STO表面にいくつかの欠陥(酸素空孔など)が存在します。負の電圧またはパルスがデバイスに印加されると、In電極から注入された電子は、Pt / Nd:STO界面の欠陥によってトラップされました。トラップされた電子は、ショットキー障壁をより狭く、より低くし、LRSをもたらします。対照的に、次の正のバイアス掃引中に、空乏領域が存在するためにトラップされた電子が放出され、HRSが発生します。さらに、欠陥の空間分布は不均一でなければなりません。高密度欠陥でフェルミピンが形成される可能性があるため、印加されたバイアスを取り除いてもHRSとLRSを維持できます。空乏層はパルス幅または大きさによって調整できるため、マルチレベルのメモリ状態が観察されました。図5は、Pt / Nd:STOインターフェースでの電子トラップまたはデトラップのプロセスの概略図を示しています。

HRSおよびLRSでのエネルギーバンド構造と界面状態Pt / NSTO / Inシステムの概略図。境界面にある赤い中空球と中実球は、それぞれ、占有されていない境界面と占有されている境界面の状態を表しています。

メモリ状態に依存するPV効果は、さまざまなメモリ状態でのPt / Nd:STOインターフェイスバリアのさまざまな幅と高さによって引き起こされます。より広い空乏領域を持つHRSは、光照射下で空乏領域で生成されるより多くの電子正孔対をもたらします。光生成された電子は、HRSの強い上向きのバンドベンディングによって、Nd:STOバルクに打ち込まれ、正孔はバリアを通り抜け、Vocが高くなります。逆に、空乏領域がより低く、より狭いLRSは、より低いVocをもたらします。一般に、Vocは、Pt / Nd:STO / Inデバイスのマルチレベルメモリ状態に対応するインターフェイスバリアの幅と高さに依存します。

メモリ状態とPV効果の両方がスイッチングバイアスへの同様の依存性を示し、Nd:STO界面での電子の枯渇/蓄積に関連する共通のメカニズムを示し、界面バリアと界面電荷の再分布の重要性を明らかにしていることに注意してください(図。 5)。 PV効果は、内部電場によって分離された光生成された電子と正孔によって引き起こされます。したがって、Pt / Nd:STO / Inデバイスで観察されたメモリ状態に依存するPV効果は、RSが、導電性フィラメントの形成ではなく、Pt / Nd:STO界面のショットキーバリアのバイアス誘起変調によって誘起されることを証明します。 Vocはメモリ状態に依存するため、このような抵抗状態に依存するPV効果は、従来の抵抗読み取りに加えて、RSデバイスのメモリ状態を検知するためにVocを使用することによって新しいルートを提供します[23]。この新しい読み取りルートは、光の照明によってデバイスのメモリ状態が変化しないため、非破壊的で信頼性があります。

結論

要約すると、単結晶Nd:STOベースのメモリスティブデバイスのRSおよびPV特性を調査しました。 RS効果は、Ptとn型Nd:STO単結晶の界面近くのショットキー接合に関連しています。メモリの状態は、パルス幅またはパルスの大きさによって変調できます。 Pt / Nd:STO / Inデバイスのメモリ状態に依存するPV効果は、スイッチング電圧によって得られます。これらの補完的な効果は、Pt / Nd:STOインターフェースでのキャリア注入とトラップ/デトラッププロセスによって引き起こされる、Pt / Nd:STOインターフェースでの、高さと幅の両方でのインターフェースバリアのバイアス誘起変調に起因します。 。この結果は、RS / PV効果と、印加された電界によってトリガーされるNd:STOインターフェイスの変調との間に強い関係を確立し、Vocを使用して複数の不揮発性メモリ状態を非破壊的に検出する新しいルートを提供します。

略語

- HRS:

-

高抵抗状態

- I – V :

-

電流-電圧

- LRS:

-

低抵抗状態

- PV:

-

光起電力

- RRAM:

-

レジスタンスランダムアクセスメモリーズ

- RS:

-

抵抗スイッチング

- XRD:

-

X線回折

ナノマテリアル

- 新規ナノ粒子増強ワーム状ミセルシステムの研究

- ボロフェンの安定性とSTM画像に関する第一原理研究

- らせん状溝管内のTiO2-水ナノ流体の流れと熱伝達特性に関する実験的研究

- 抵抗変化型メモリのモデリングとシミュレーションに関する集合的研究

- サイズ、修正、欠陥、およびドーピングによるグラフェン仕事関数の設計と調整:第一原理理論研究

- Ag n V(n =1–12)クラスターの構造的、電子的、および磁気的特性の調査

- ポリオール媒介プロセスによるZnOナノクリップの製造と特性評価

- <100>引張荷重下のタンタル単結晶の弾性特性の温度および圧力依存性:分子動力学研究

- 天然および合成ナノ材料の電気化学的、生物医学的、および熱的特性の比較研究

- 新規SrTiO3 / Bi5O7Iナノコンポジットの製造と光触媒特性

- 新しい研究:作業と自動化の将来に対するCOVID-19の影響