両側ゲート制御S / D対称および交換可能双方向トンネル電界効果トランジスタの構造パラメータと内部メカニズムの効果に関する研究

要約

この論文では、双方向ゲート制御のS / D対称および交換可能な双方向トンネル電界効果トランジスタ(B-TFET)を提案します。これは、従来の非対称TFETと比較して双方向スイッチング特性とCMOS集積回路との互換性の利点を示しています。構造パラメータの影響、たとえば、N + のドーピング濃度 リージョンとP + 領域、N + の長さ 伝達特性などのデバイス性能に関する固有領域の領域と長さ I on – 私 オフ 比率とサブスレッショルドスイング、および内部メカニズムについて詳しく説明します。

はじめに

消費電力は、集積回路業界の主要な問題の1つです。デバイスがオン状態で動作する場合、その導通電流は特定の臨界値に到達する必要があります。電流が臨界値に達すると、対応するゲート電圧がしきい値電圧として定義されます。デバイスがオフ状態の場合、対応するゲート電圧は、クリティカルオン状態の値とは異なる値である必要があります。これは、オフ状態電圧と呼ばれることがよくあります。サブスレッショルドスイング(SS)の概念は、オフ状態とクリティカルオン状態の間で動作するデバイスに適用できます。これは、電流が1桁増加したときのゲート電圧の変化に相当します。デバイスが適切に設計されている場合、デバイスの臨界オン状態電流値、しきい値電圧、およびオフ状態電圧が決定されています。次に、SSが小さいほど、サブスレッショルド領域での電流変化が強くなり、オフ状態のデバイスの静的電流が小さくなり、デバイスの静的消費電力が低くなります。集積回路で広く使用されている基本ユニットセルである金属酸化物半導体電界効果トランジスタ(MOSFET)のSSは、デバイスの動作中に発生する電流の物理的メカニズムによって制限され、制限値の60を下回ることはできません。 mV / dec。この制限を打破するために、近年、シリコンベースの技術に基づくトンネル電界効果トランジスタ(PINまたはNIP TFET)が提案されています。従来のTFETは、 p の間に低ドーピングの真性半導体の層を追加することによって形成されます。 -および n タイプの半導体材料。 TFETは、MOSFETと比較して、感度が高く、静的消費電力が少ないという利点があります[1]。 TFETは、従来のMOSFETのようにバリアを介した熱電子放出を変調するのではなく、バリアを介して量子トンネリングを変調することによって切り替えられます。したがって、TFETは、キャリアの熱マクスウェル-ボルツマンテールによって制限されません。これにより、MOSFETのSSは室温で60 mV / decに制限されます[2](300Kで正確に63mV / dec)。コンセプトはチャンらによって提案されました。 IBMで働いている間[3]。 IBMのJoergAppenzellerと彼の同僚は、TFETのSSが60 mV / dec未満になる可能性があることを初めて実証しました。 TFETはエネルギー効率の高い電子スイッチとして使用でき[4]、MOSFETのボトルネックを打ち破り、ICの消費電力を大幅に削減します。製造工程はMOSFETと互換性があります。次世代集積回路の基本ユニットとしてMOSFETトランジスタに取って代わる可能性があります。そのため、近年、TFETが話題になっています[5、6]。 SS、順方向伝導電流、逆方向漏れの観点からTFETの性能を向上させるために、TFETデバイスの構造設計と最適化に関する多くの研究が行われ、主にデバイスチャネルとゲート電極の構造形状の改善に焦点が当てられています[7 、8、9、10、11、12]および異なる作業機能を備えたゲート誘電体材料。ゲート誘電体材料[13,14,15]と異なる誘電率を持つゲート誘電体[15,16,17,18,19,20]の特性分析と構造最適化が実行されました。デバイス物理学では、ダブルゲート構造[21,22,23,24,25,26,27]と周囲ゲート構造[28,29,30,31,32,33]を備えたTFETの分析モデリングもあります。広範囲に実行されました。 MOSFETと比較したシリコンベースのTFETの欠点の1つは、順方向電流が小さいことです。順方向電流の大きさは、トンネル電流生成の効率によって決まります。トンネル電流生成効率は、バンド間トンネル電流を生成するために使用される領域の価電子帯と伝導帯の間のバンドギャップを減らすことによって、またはトンネル領域の厚さを減らすことによって高めることができる。したがって、材料工学では、狭帯域ギャップ半導体材料とヘテロ接合トンネル構造に基づくTFETデバイスが広く開発されてきました[34、35、36、37、38]。一方、極薄の厚さのトンネル層としての二次元材料のTFETへの導入は広く研究されてきた[39,40,41,42,43,44]。さらに、いくつかの論文は、トンネリングバンドギャップインターリーブに対するソースドーピングの影響[45]、TFETのサブスレッショルド特性に対するトラップ支援トンネリングの影響[46]、およびランダムの影響など、TFETの信頼性を報告しています。デバイス性能摂動へのドーピング[47]。しかし、現在の研究成果は主にシングルTFETの基本的な動作特性と動作原理を目指しており、TFETの研究開発の最も重要な基本的な目的は、消費電力の少ない基本的な構造ユニットを提供し、既存のMOSFET構造を置き換えることです。 。この基本的な目標を達成するには、MOSFET技術との互換性を検証するために特定の回路に設定する必要があります。現在、アナログ・ミックスドシグナル回路[48,49,50]、デジタル論理回路[50,51]、パワーマネジメント回路設計[52]など、TFETデバイスに基づく回路設計戦略の研究が徐々に行われています。 MOSFETとTFETに基づくハイブリッド回路の設計に関する研究もあります[53]。しかしながら、ソース領域とドレイン領域のドーピングタイプは互いに反対であり、それはソース領域とドレイン領域の非対称性を生み出す。この非対称構造により、MOSFETをソース/ドレイン対称に完全に置き換えることは不可能です。

n を取る -例としてTFETを入力します。 p のある側 -タイプの不純物がソース領域として使用され、反対側は n ドレイン領域にはタイプ不純物を使用しています。デバイスが動作するとき、正の電位差をドレイン領域からソース領域に印加する必要があります。ソース電極とドレイン電極が交換されている場合、つまり p タイプの不純物領域は、 n に比べて高い電位に設定されています タイプの不純物領域、次に p によって形成されるPN接合 -タイプの不純物領域と n タイプの不純物領域は常に正のバイアス状態になり、ゲート電極の制御機能が失敗します。TFETはほとんどの場合オン状態になり、オフにすることはできません。つまり、TFETスイッチ機能の障害を引き起こします。言い換えれば、トランジスタの双方向スイッチング特性を使用して正常に動作する必要がある回路機能モジュール(伝送ゲートなど)は、これらの問題を解決するために、ソースとドレインの非対称構造を持つ従来のTFETを使用して実現することは困難です。 、ソースドレイン対称で交換可能な双方向TFET(B-TFET)[54]を提案しました。これは、従来の非対称TFETと比較して双方向スイッチング特性とCMOS集積回路との互換性の利点を示しています。本論文では、平面チャネルを備えた修正された両側ゲート制御B-TFETを提案した。 N + のドーピング濃度などの主要な構造パラメータの影響 リージョンとP + 領域、N + の長さ 伝達特性などのデバイス性能に関する固有領域の領域と長さ I on – 私 オフ 比率とサブスレッショルドスイングは、物理的分析に基づいて詳細に説明されています。その後、これらの主要な構造パラメータが最適化されます。

メソッド

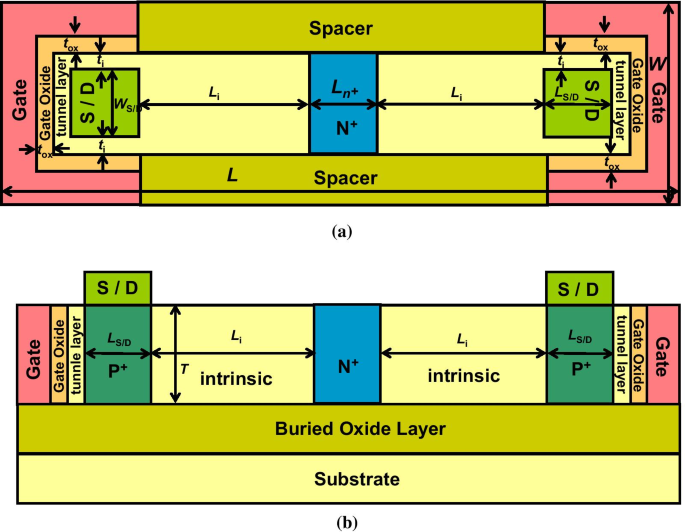

図1aは、平面チャネルを備えた両側ゲート制御N型B-TFETの概略上面図を示しています。図1bは、両側ゲート制御のN型B-TFETの断面図を示しています。従来のTFETとは異なり、提案されたB-TFETは完全に対称であり、ソース/ドレイン交換可能P + ドープされた領域はシリコン本体の両側にあり、ゲート電極はシリコン本体の両側にあります。デバイス構造全体が対称です。 N + ドープされた領域は、シリコン本体の中央部分にあります。 L および W は、それぞれ提案されたデバイスの全長と全幅です。 L i 固有領域の長さです。 L N + N + の長さです 領域; L S / D および W S / D P + の長さと幅です それぞれ、ソース/ドレイン交換可能領域。 \(T \)はシリコン本体の厚さです。 \(t _ {{{\ text {ox}}}} \)はゲート酸化物の厚さです。 \(t_ {i} \)は、S / D領域とゲート酸化物の間の固有のトンネル領域の厚さです。

a 平面チャネルを備えた両側ゲート制御N型B-TFETの概略上面図。 b 両側ゲート制御N型B-TFETの断面図

この論文では、フェルミ統計モデル、CVTモビリティモデル、オージェ再結合モデル、バンドギャップナローイングモデル、標準のバンド間トンネリングモデルなどのすべての物理モデルをオンにします。このホワイトペーパーのデバイスのすべてのパラメータを表1に示します。

<図>結果と考察

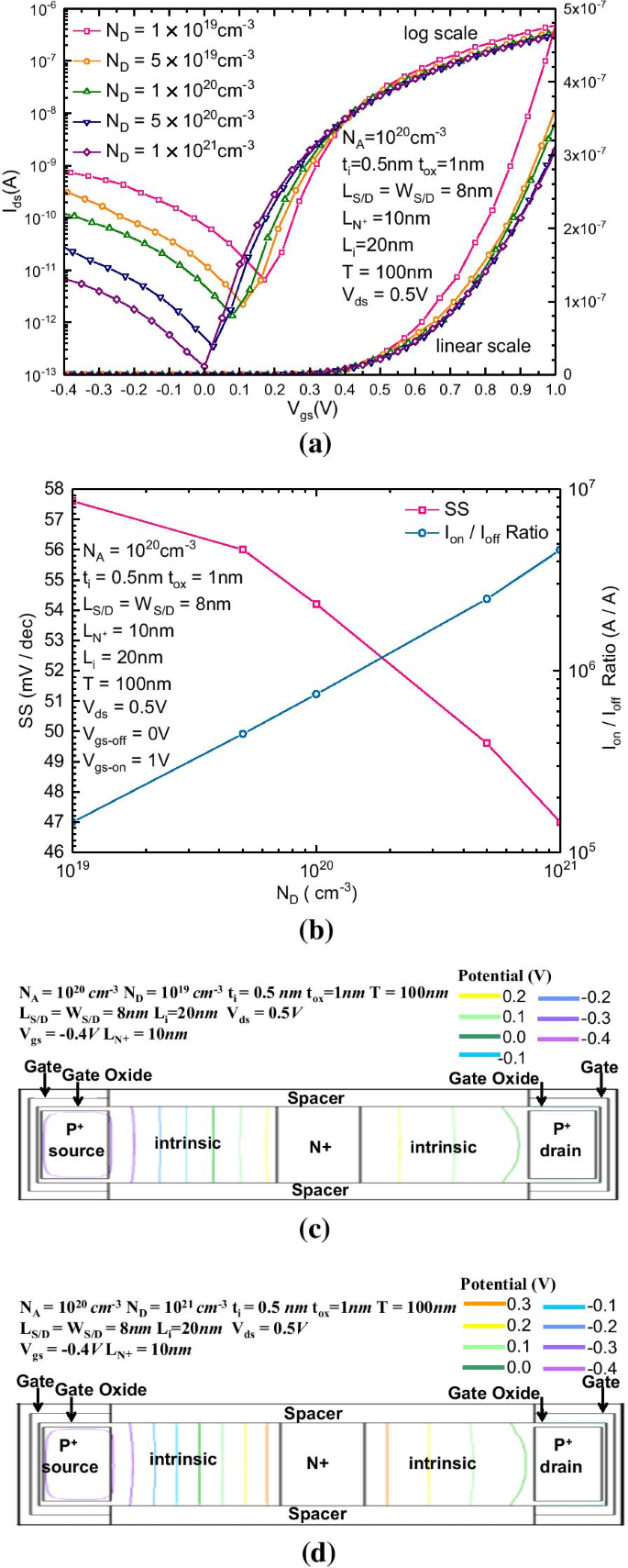

図2a、bは、伝達特性、\(I _ {{{\ text {on}}}} {-} I _ {{{\ text {off}}}} \)比、および異なる\(N_ { D} \)(\(10 ^ {18} \)– \(10 ^ {21} \、{\ text {cm}} ^ {--3} \))。図2aでは、\(N_ {D} \)は逆バイアスされたドレインからソースへのリーク電流の強度に影響を与えます。ドーピング濃度の増加に伴い、漏れ電流は大幅に抑制され、順方向電流は大幅に変化しません。図2bでは、SSと\(I _ {{{\ text {on}}}} {-} I _ {{{\ text {off}}}} \)も\(N_ {D} \ )。ドーピング濃度の増加に伴い、逆リーク電流が大幅に抑制されるため、静的動作点での電流が減少し、平均SSも減少します。順方向電流は逆方向リークよりもはるかに影響を受けないため、\(I _ {{{\ text {on}}}} {-} I _ {{{\ text {off}}}} \)比は増加とともに増加しますドーピング濃度で。図2c、dは、\(N_ {D} \)が10 19 に等しい提案されたB-TFETの2次元電位分布を示しています。 cm -3 および10 21 cm -3 、 それぞれ。ゲート電極が逆バイアスされると、順バイアスされたドレイン電極と逆バイアスされたゲート電極の間に強い電界が生成され、その結果、ドレイン領域の近くで強いバンド間トンネリングが発生します。結果として生成される電子正孔対の中で、電子はドレイン電極から直接流出できますが、価電子帯正孔はN + を通って流れる必要があります。 領域、続いてソース側の固有領域に続き、ソース電極によって放電されて、連続リーク電流を形成します。リーク電流を最小限に抑えるには、バンド間トンネリングによって生成されたホールがN +領域から流出するのを効果的にブロックする必要があります。低濃度のN +領域と比較して、高濃度のN +領域は、P +領域とN +領域の間に大きな電位差を形成します。つまり、固有領域とN +領域の境界での電位値が増加します。 \(N_ {D} \)の増加に伴い、濃度の高いN +領域では、ソースとドレインの間に大きな電子濃度差が生じる可能性があるためです。次に、より多くの電子をN +領域からN +領域の両側の固有領域に拡散させることができます。これにより、イオン化後のN +領域の正電荷(主にドナーで構成される)の量が増加し、その結果、電位が上昇します。 P +領域とN +領域の違い。ドーピング濃度の高いN +領域は、イオン化後のソース側とドレイン側の両方よりも電位が高いため、ドレイン領域の近くのバンド間トンネリングによって生成されたホールをより効果的にブロックでき、より効果的に減少します。漏れ電流。

a \(I _ {{{\ text {ds}}}} {-} V _ {{{\ text {gs}}}} \)転送特性と b SSの変動と、異なる\(N_ {D } \); c による逆バイアスされた2次元ポテンシャル分布 N D =10 19 cm -3 および d N D =10 21 cm -3

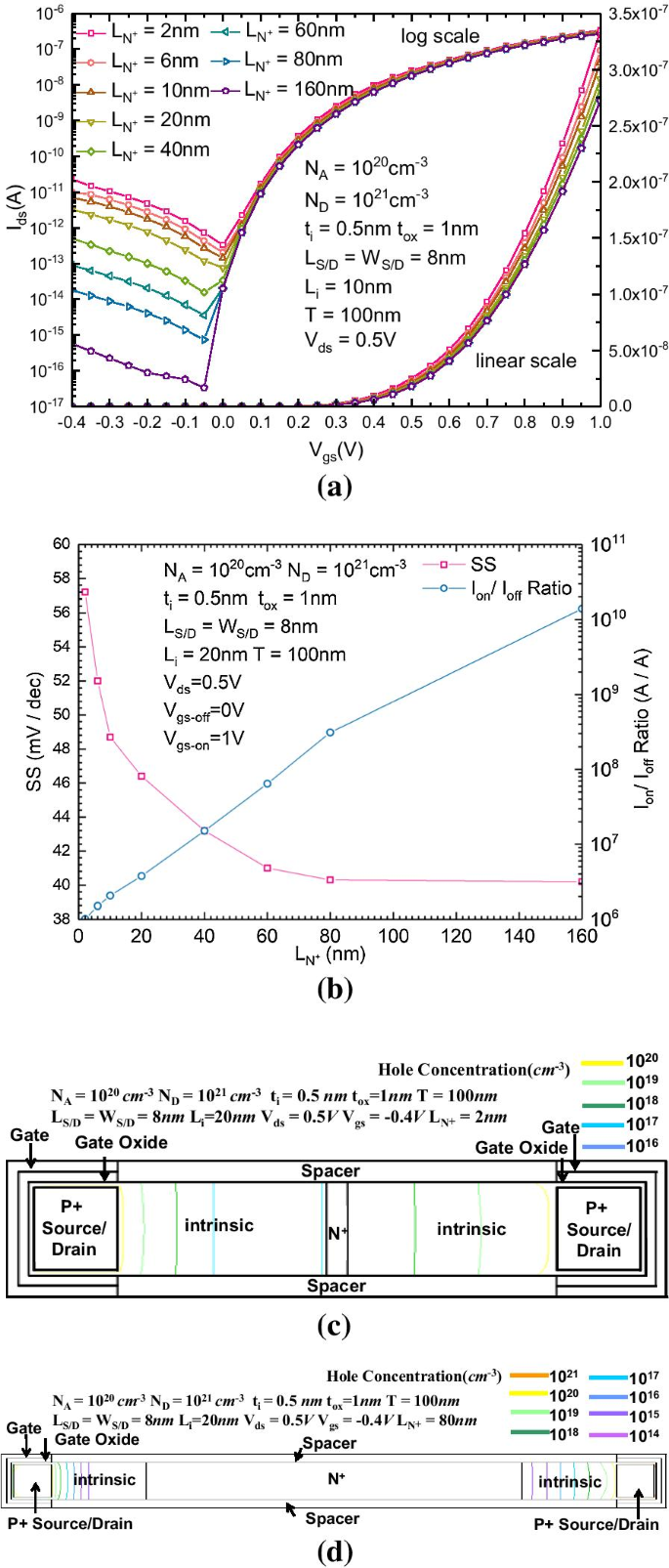

N +領域のドーピング濃度に加えて、逆バイアスされたリーク電流に大きな影響を与える可能性のあるN +領域のもう1つの重要なパラメータは、N +領域の長さです。図3a、bは、異なるを使用した提案されたB-TFETの\(I _ {{{\ text {ds}}}} {-} V _ {{{\ text {gs}}}} \)転送特性を示しています。 L N + 。逆バイアスされたリーク電流は、 L の増加とともに大幅に減少します。 N + 。図2bに示すように、サブスレッショルドスイングと\(I _ {{{\ text {on}}}} {-} I _ {{{\ text {off}}}} \)も L <の影響を受けます。 / i> N + 。 L の増加に伴い N + 、逆リーク電流が大幅に抑制されるため、静的動作点での電流と平均SSも減少します。順方向電流は逆方向リークよりもはるかに影響が少なく、\(I _ {{{\ text {on}}}} {-} I _ {{{\ text {off}}}} \)比は増加とともに増加します L で N + 。図3c、dは、 L を使用した提案されたB-TFETの2次元正孔濃度分布を示しています。 N + それぞれ2nmと80nmに相当します。 L の場合 N + が2nmに等しい場合、N +領域の最小正孔濃度は10 17 より大きくなります。 cm -3 、 L の場合 N + が80nmに等しい場合、最小正孔濃度は10 14 未満です。 cm -3 。 N +領域の長さが長くなると、ホールがN +領域を通過するのを防ぐ能力が向上します。 N +領域の非平衡少数キャリアとして、N +領域が長くなると、N +領域を通過する前に、より多くの正孔が電子と再結合するため、N +領域の長さの増加も形成する可能性があります。連続的な逆バイアスされたリーク電流。平均SSは40.2mV / decに下げることができ、\(I _ {{{\ text {on}}}} {-} I _ {{{\ text {off}}}} \)比は10 <を超えることができます。 sup> 10 。

a \(I _ {{{\ text {ds}}}} {-} V _ {{{\ text {gs}}}} \)特性; b SSの変動と、L が異なる提案されたB-TFETの\(I _ {{{\ text {on}}}} {-} I _ {{{\ text {off}}}} \)比N + ; L に対して逆バイアスをかけた場合の提案されたB-TFETの2次元正孔濃度分布 N + (3)2 nmおよび(4)80nmに等しい

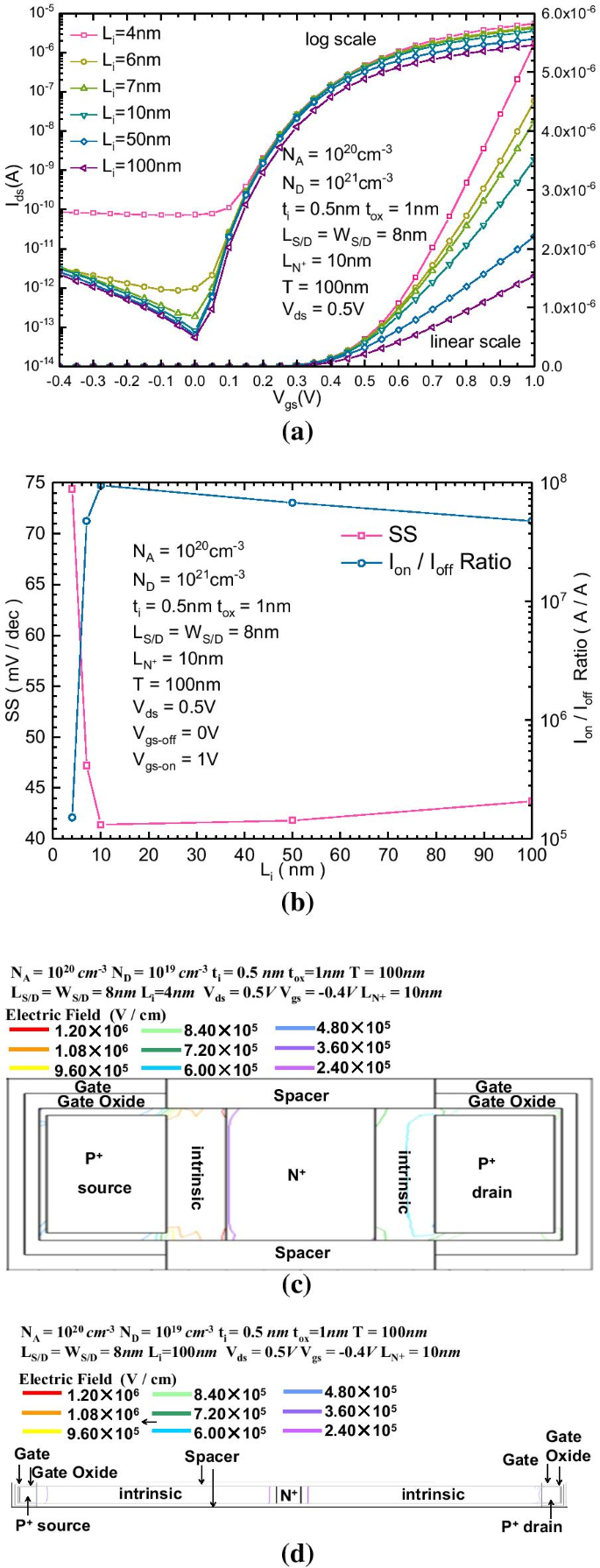

図4a、bは、\(I _ {{{\ text {ds}}}} {-} V _ {{{\ text {gs}}}} \)転送特性とSSおよび\(I _ {{{ \ text {on}}}} {-} I _ {{{\ text {off}}}} \)異なる L を持つ提案されたB-TFETの比率 i 、 それぞれ。順方向電流は L の増加とともに減少します i 固有領域の抵抗はそれ自体の長さに比例するためです。次に、順方向電流を最大化するには、固有領域の長さを最小化する必要があります。ただし、固有領域の長さが短くなると、ソースP +領域とN +領域の間の固有領域の電界が強化されるため、この領域の近くで曲がるバンドは、ドレイン電極の近くの固有領域よりも大きくなります。より逆にバイアスされたリーク電流。図4c、dは、 L に対して提案されたB-TFETの2次元逆バイアス電位分布を示しています。 i それぞれ4nmと100nmに相当します。最短の L i (4 nm)の場合、ソース電極の近くのソースP +領域とN +領域の間の固有領域の電界は、ドレインP +領域と近くのN +領域の間の固有領域の電界よりもはるかに強くなります。ドレイン電極。その場合、リーク電流はほぼ一定に保たれますが、これはゲート電圧の変化とは無関係です。図4bは、 L の最適値の範囲を示しています。 i は約7〜10 nmで、SSは41 mV / decの谷の値に減少し、\(I _ {{{\ text {on}}}} {-} I _ {{{\ text {off}}} } \)比率はほぼ10 8 の最大値に増加します 。

a \(I _ {{{\ text {ds}}}} {-} V _ {{{\ text {gs}}}} \)B-TFETと b の特性 SSの変動と\(I _ {{{\ text {on}}}} {-} I _ {{{\ text {off}}}} \)の比率が異なる\(L_ {i} \); L に対して提案されたB-TFETの2次元逆バイアス電位分布 i c に等しい 20nmおよび d 100 nm

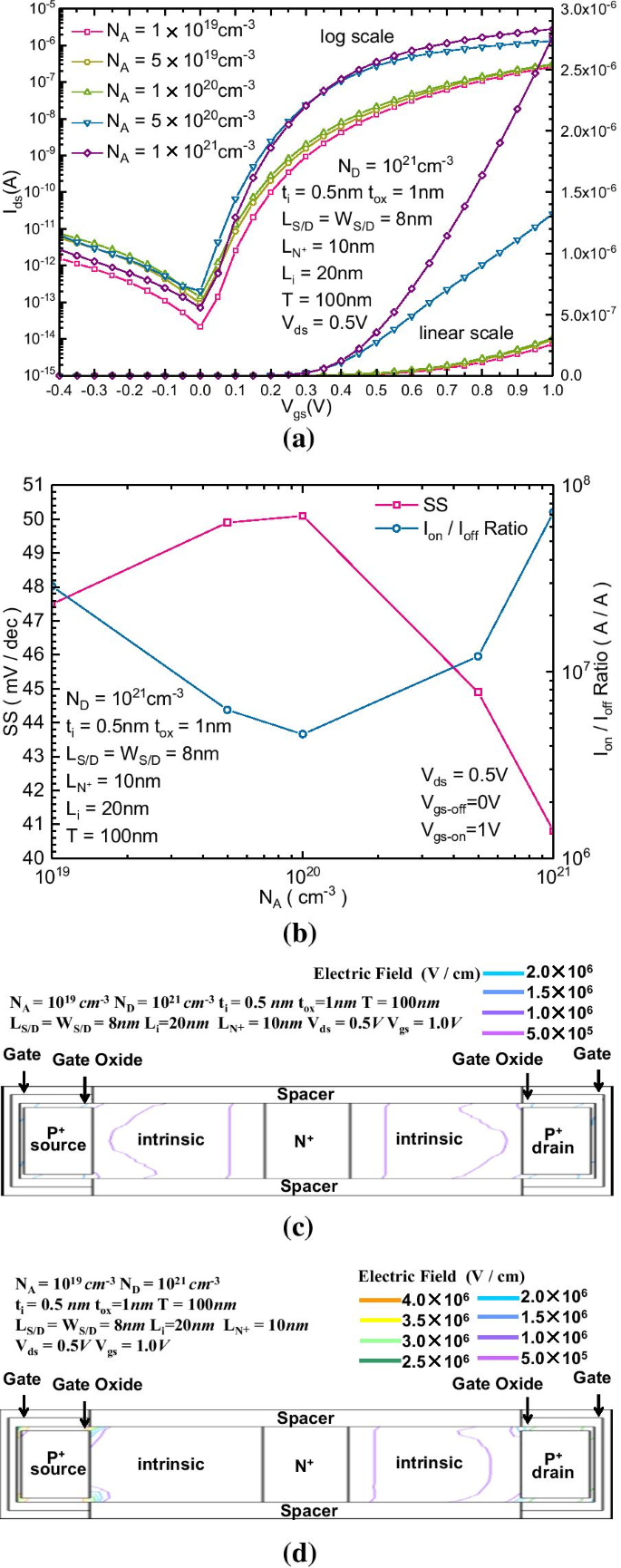

図5a、bは、\(I _ {{{\ text {ds}}}} {-} V _ {{{\ text {ds}}}} \)転送特性とSSおよび\(I _ {{{ \ text {on}}}} {-} I _ {{{\ text {off}}}} \)異なる\(N_ {A} \)を持つ提案されたB-TFETの比率。図5aは、P +ドープ領域の濃度を上げることにより、SSを減らし、順方向電流を大きくできることを示しています。逆バイアスされたリーク電流は、\(N_ {A} \)の変化による影響は明らかではありませんが、\(N_ {A} \)の増加に伴って順方向電流を増加させることができます。図5bでは、\(N_ {A } \)。図5c、dは、\(N_ {A} \)が10 19 に等しい提案されたB-TFETの2次元電界分布を示しています。 cm -3 および10 21 cm -3 、 それぞれ。 \(N_ {A} \)の増加は、固有のトンネル領域の電界を強化します。次に、バンド間トンネリングによってより多くの電子正孔対を生成できます。これにより、提案されたB-TFETの順方向電流が向上します。

a \(I _ {{{\ text {ds}}}} {-} V _ {{{\ text {gs}}}} \)転送特性、 b 異なる\(N_ {A}を持つ提案されたB-TFETのSSおよび\(I _ {{{\ text {on}}}} {-} I _ {{{\ text {off}}}} \)比の変動\)。 (3)10 19 に等しい\(N_ {A} \)の提案されたB-TFETの2次元逆バイアス電界分布 cm -3 および(4)10 21 cm -3

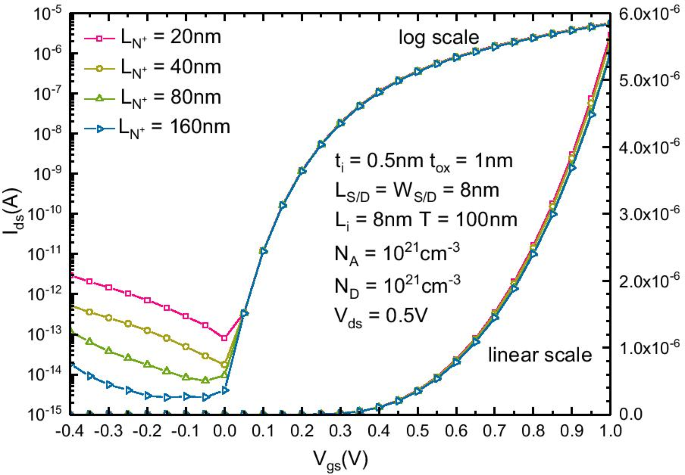

上記の説明によると、\(N_ {D} \)と\(N_ {A} \)の両方を可能な最大値に設定する必要があります。 L の最適値の範囲 i は7〜10nmです。ただし、静的消費電力と L の間にはトレードオフがあります。 N + 。図6は、さまざまな L <を使用した最適化されたB-TFETの\(I _ {{{\ text {ds}}}} {-} V _ {{{\ text {ds}}}} \)転送特性を示しています。 / i> N + 。 L N + さまざまな静的消費電力設計要件に従って選択できます。妥協案として、\(I _ {{{\ text {on}}}} {-} I _ {{{\ text {off}}}} \)の比率が10 8 > 、L N + 20nm以上にすることをお勧めします。オン電流は約6×10 –6 に増加します A、SSは38 mV / decに減少します。

\(I _ {{{\ text {ds}}}} {-} V _ {{{\ text {ds}}}} \)異なるL N + を使用した最適化されたB-TFETの伝達特性

結論

本論文では、両側ゲート制御S / D対称および交換可能双方向トンネル電界効果トランジスタの構造パラメータと内部メカニズムの影響を分析した。 N +領域の濃度と長さ、P +領域とN +領域の間の固有領域の長さ、P +領域の濃度などの重要なパラメータの影響について詳しく説明しました。従来のTFETと比較して、B-TFETには逆バイアスされたリーク電流に対する強い耐性という利点があります。その後、平均SSが低くなり、\(I _ {{{\ text {on}}}} {-} I _ {{{\ text {off}}}} \)比が高くなるなどの良好なパフォーマンスが得られます。さらに、構造の対称性とソース/ドレインの交換可能で双方向のスイッチング特性により、CMOS回路との互換性が高くなります。

データと資料の可用性

私たちは、「競合する利益」の下で、私たち自身のために、そして私たちの共著者に代わって、データと資料の入手可能性に関する声明を含めました。入手可能なすべてのデータと資料はオリジナルの作品です。すべてのデータは、追加のデータや補足資料なしで原稿に明確に提供されています。

略語

- L :

-

提案されたデバイスの全長

- W :

-

提案されたデバイスの全幅

- L i :

-

固有領域の長さ

- L N + :

-

N + の長さ 地域

- L S / D :

-

P + の長さ ソース/ドレイン交換可能領域

- W S / D :

-

P + の幅 ソース/ドレイン交換可能領域

- \(T \):

-

シリコンボディの厚さ

- \(t _ {{{\ text {ox}}}} \):

-

ゲート酸化物の厚さ

- \(t_ {i} \):

-

S / D領域とゲート酸化物の間の固有トンネル領域の厚さ

- MOSFET:

-

金属酸化物半導体電界効果トランジスタ

- TFET:

-

トンネル電界効果トランジスタ

ナノマテリアル

- ショックリーダイオード

- ボロフェンの安定性とSTM画像に関する第一原理研究

- 色素増感太陽電池の光学的および電気的特性に及ぼすTiO2中の金ナノ粒子分布の影響

- MnХFe3−XО4スピネルの構造的および磁気的特性に及ぼす接触非平衡プラズマの影響

- TIPS-ペンタセンベースの有機電界効果トランジスタの移動度と形態に及ぼすその場アニーリング処理の影響

- らせん状溝管内のTiO2-水ナノ流体の流れと熱伝達特性に関する実験的研究

- TiO2ナノチューブアレイ:ソフトハードテンプレートで製造され、電界放出性能の粒子サイズ依存性

- Pt / Nd:SrTiO3接合におけるマルチレベル抵抗スイッチングメモリとメモリ状態依存光起電力に関する研究

- サイズ、修正、欠陥、およびドーピングによるグラフェン仕事関数の設計と調整:第一原理理論研究

- 水性電解質中の対称スーパーキャパシタとしてのカーボンナノファイバーと活性炭の研究:比較研究

- Ag n V(n =1–12)クラスターの構造的、電子的、および磁気的特性の調査