AlドープHfO2薄膜に基づくマルチレベルメモリスタ

要約

不揮発性メモリ(NVM)は、モノのインターネットを含む次世代のデジタルテクノロジーで非常に重要な役割を果たします。特にHfO 2 に基づく金属酸化物メモリスタ は、そのシンプルな構造、高い統合性、高速な動作速度、低消費電力、および高度な(相補型金属酸化物シリコン)CMOSテクノロジとの高い互換性により、多くの研究者に支持されています。この論文では、20レベルの安定した抵抗状態がAlドープHfO 2 ベースのメモリスタが表示されます。そのサイクルの耐久性、データ保持時間、および抵抗率が10 3 を超えています 、> 10 4 s、および> 10。

背景

負性抵抗現象は、HickmottによってAl / Al 2 で最初に発見されましたが O 3 / Auは1962年に構造化され[1]、Chuaは1971年にメモリスタの概念を提案しました[2]。 StrukovらがTiO 2 を準備するまではありませんでした 2008年にベースのメモリスタ[3]は、人々がメモリスタの研究に注目し始めました。現在、研究者は、複数の複合酸化物[4、5]、ZnO [6]、TiO x などの金属酸化物を含む、数十を超える活性抵抗性材料を備えたメモリスタを準備しています。 [7]、TaO x [8]、および二次元材料[9、10]。 HfO 2 信頼性が高く、動作速度が速く、消費電力が少ないため、CMOSデバイスのhigh-kゲート誘電体として使用されてきました[11、12]。記憶に残る資料としても研究者に好まれています[13、14、15]。

マルチレベルメモリスタは、データストレージ[16、17、18]、論理計算[19]、電子シナプスデバイス[20、21、22、23]などとして広く使用できます。 Wang Y. [16]およびGaoB。etal。 [24] HfO 2 をドープしてマルチレベルメモリスタを作成 それぞれCuとGdを使用しますが、作成できるのは4レベルのストレージ状態のみであり、アプリケーションの要求を満たすことは困難です。したがって、HfO 2 に関する研究 マルチレベルのメモリスタは非常に重要です。

メソッド

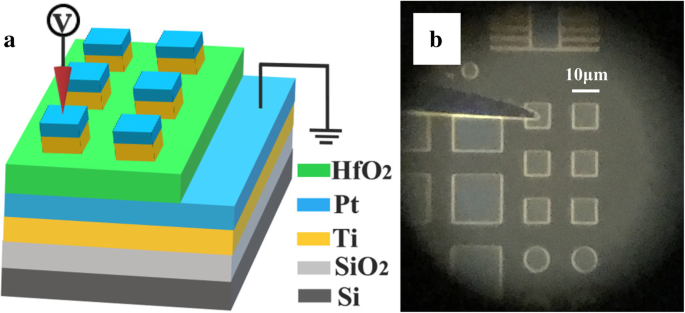

Ti / Al:HfO 2 / Ptデバイスは図1aに示すように製造されました。アクティブセル領域は、正方形のTi上部電極(TE)によって定義されました。 20 nmのTi接着剤層は、シリコン基板上に直流(DC)スパッタリングによって堆積され、次に100 nmのPt膜が下部電極(BE)として堆積されました。 20nmのAlドープHfO 2 機能層は、原子層堆積(ALD)リアクター(R-150、Picosun、エスポー、フィンランド)によって300°CでMeCp 2 を使用して堆積されました。 Hf前駆体としてのHfMe(OMe)(HfD-04と表記)、およびH 2 酸素源としてのO [25]。前駆体は高純度のN 2 によって運ばれました (> 99.999%)リアクターチャンバーに入れます。 Alドープ膜は、Al 2 の1サイクルを堆積することによって得られました。 O 3 HfO 2 の8サイクルごと Al源としてトリメチルアルミニウム(TMA)を使用し、H 2 酸素源としてのO。 6.2%のAl原子濃度は、ThermoFisherのTheta300 XPSシステムでX線光電子分光法(XPS、Axis Ultra DLD、Kratos Analytical、マンチェスター、英国)によって検出されます。 TEとしての50nmのTi膜および被覆層としての100nmのPtが、DCスパッタリングによって堆積された。デバイスは、光リソグラフィーとリフトオフプロセスによってTEをパターン化することによって得られます。図1bはデバイスの光学顕微鏡写真です。 5μm×5μmから500μm×500μmまでのさまざまな面積のデバイスを用意しました。

デバイスの構造。 a メモリスタの3Dモデル。 b デバイスの光学顕微鏡

結果と考察

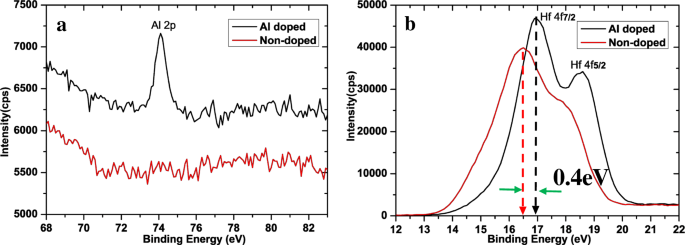

図2は、Alドープデバイスと非ドープデバイスのXPSを示しています。非ドープデバイスのスペクトログラムと比較すると、Alドープデバイスは図2aでAl2pの明確な74.1eVピークを示し、Hf4fの結合エネルギーは図2bで一定の増加を示しています。 Hf 4f 5/2 の比率 Hf 4f 7/2 へ ドープされたデバイスでも増加しました。それは他の報告と一致しています[14、26、27]。 Al原子はHfO2構造に結合して、Hf-Al-Oを形成します。これにより、Hf-O結合が弱くなり、壊れやすくなります。

Alドープおよび非ドープデバイスのXPS。 a Al2pおよび b Hf4fが比較されます

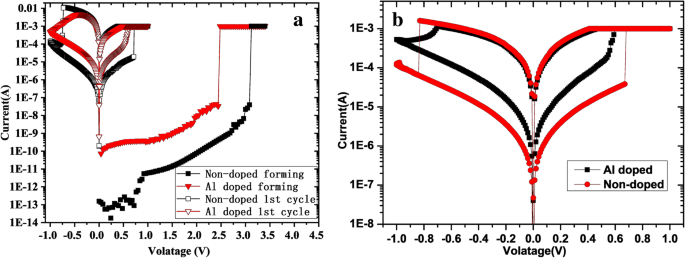

すべての電気的測定で、Pt BEが接地されている間、TiTEにバイアスがかかりました。 DCスイープは、ソース/測定ユニットを備えたB1500Aパラメーターアナライザー(サンタクララ、カリフォルニア州、米国)を使用して実行され、波形ジェネレーター/高速測定ユニットを使用したパルス電気測定も使用されます。すべてのデバイスは、必要な電気成形プロセスの前に高抵抗状態(HRS)を示します。図3aは、10μm×10μmのAlドープデバイスと非ドープデバイスの成形特性を示しています。デバイスを損傷から保護するには、成形中の電流コンプライアンスが必要です。非ドープデバイスの初期抵抗と形成電圧は大きくなります。ドープされていないデバイスの低電圧領域での発振は、電流が機器の測定限界よりも低いためです。図3aに示すように、成形ステップ後のリセットプロセスは負の電圧を印加することによって動機付けられ、次に最初のセットプロセスが動機付けられます。リセットの電圧振幅が増加すると、2つのデバイスの両方の電流は、形成の制限電流よりも大きくなる最大値まで増加し、その後減少します。 2つのデバイスのHRS電流は、同じ電圧での初期状態のHRS電流よりも数桁大きくなります。これは、リセット後に完全に融合できない導電性フィラメントがまだ存在することを示唆しています。図3bの典型的なセット/リセットI–V曲線は、これら2つのデバイスの両方の類型がバイポーラ動作モードであることを示しています[28]。 Alドープデバイスのスイッチング比とセット/リセット電圧は非ドープデバイスよりも小さいですが、その抵抗状態変換プロセスはより穏やかで、多値ストレージデバイスとして適しています。

デバイスのI / V特性。 a 成形プロセスと最初のサイクル。 b 典型的なセット/リセットプロセス

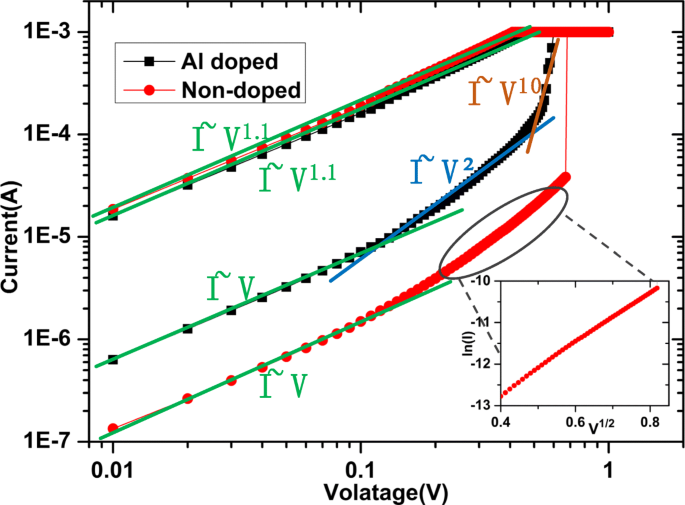

デバイスのスイッチングメカニズムを明確にするために、I–V曲線を図4に二重対数スケールで再プロットします。どちらの種類のデバイスでも、低抵抗曲線は線形オーム挙動を示します。これは、 HfO 2 設定中のフィルム[29、30]。ただし、これら2種類のデバイスでは、高抵抗曲線が大きく異なります。ドープされたデバイスの場合、オーミック領域(I∝V)、チャイルドロー領域(I∝V 2 )の3つの領域で構成されます。 )、およびトラップ制御空間電荷制限電流(SCLC)の典型的なI–V特性と一致する急電流増加領域[31、32]。非ドープデバイスの高抵抗曲線は、2つの領域で構成されています。低電圧領域でのオーム伝導(I∝V)と、lnI-V 1/2 > 高電圧領域(図4の挿入図)で、ショットキー放出メカニズムを確認します[15、33]。

二重対数座標でのSETプロセスのカーブフィッティング

上記の特徴によると、メモリスタの微視的メカニズムは次のように要約されます。ドープされていないデバイスの場合、チタン電極に印加される正の電圧が増加すると、HfO 2 で生成される酸素イオンがますます増えます。 チタン電極に向かって移動し[34]、酸化チタンを生成します[35]。同時に、白金電極とHfO 2 の間の界面に酸素空孔が蓄積します。 、導電性フィラメントを徐々に形成する[36]。したがって、電流は電圧とともに徐々に増加します。フィラメントを伝導する酸素空孔がTEとBEを接続すると、デバイスは低抵抗状態(LRS)に変わります。チタン電極に負の電圧が印加されている間、酸素イオンはHfO 2 で酸素空孔と結合します。 / Ptインターフェース[37]。これにより、酸素空孔濃度が低くなり、ショットキー障壁が高くなります。リセット電圧に達すると、導電性フィラメントが切断され、デバイスがHRSに変更されます。

Alドープデバイスの場合、Al原子はHfO2構造に結合して、Hf-Al-Oを形成します。その結果、Hf–O結合が弱くなり、壊れやすくなります。酸素空孔の形成エネルギーが減少します。したがって、ドーピングデバイスは、より小さな抵抗およびより低い遷移電圧を有する。ドープされていない膜では、酸素空孔は粒界に沿って蓄積する傾向があります[38、39]。その結果、導電性フィラメントは少なく、太くなります。デバイスの抵抗は、導電性フィラメントの導通と破損によって大きく異なります。ドープされた膜では、酸素空孔は不純物原子の近くに容易に形成されます[35、40、41]。薄膜中の大量の不純物の均一な分布は、導電性フィラメントが酸素空孔によって形成されることをより制御しやすくします。したがって、複数の抵抗値を達成する方が簡単です。

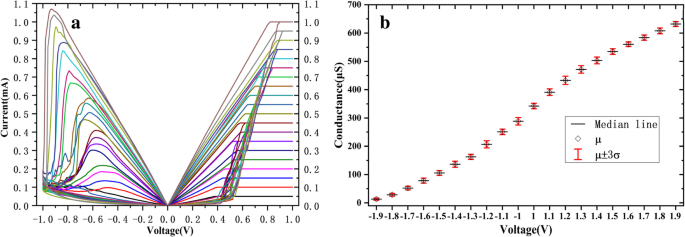

設定されたプロセスの現在のコンプライアンスを変更することにより、デバイスをさまざまな定常抵抗状態に設定できます。図5aの0.5mAのステップで0.5mAから10mAを形成する電流コンプライアンスを設定することにより、20の安定した抵抗状態が得られます。 DC掃引によって設定される抵抗状態のため、エネルギー消費量が大きく、操作が複雑になります。一方、大電流コンプライアンスを使用すると、抵抗値はLRSで簡単にロックされます。この方法でもHRSを調整することはできません。セットパルスとリセットパルスの電圧振幅を変更することにより、20レベルの抵抗状態が達成されます。電流のオーバーシュートやセット/リセットの失敗の可能性を回避するために、電圧振幅はSETの場合は1 V〜1.9 V、リセットの場合は-1 V〜-1.9Vに制限されます。箱ひげ図(図5b)から、許容電圧範囲が20の値に分割され、デバイスの歩留まりが3σレベル(99.73%)をはるかに超えていることがわかります。これは、本番環境での一般的な要件です。この方法の欠点は、デバイスをあるHRS(LRS)から別のHRS(LRS)に直接設定できないことですが、最初にLRS(HRS)にリセット(設定)してから、ターゲットHRS(LRS)に設定する必要があります。 。これにより、操作の複雑さと消費電力が増加します。

デバイスのマルチバリューストレージ。 a コンプライアンス電流を設定して抵抗状態を変換します。 b パルス電圧振幅を設定することで得られる20の安定した抵抗状態パルス幅と間隔は両方とも500μsです

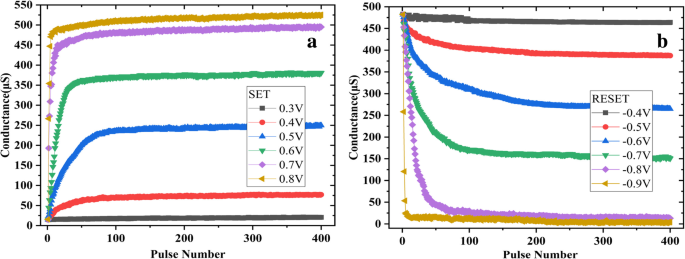

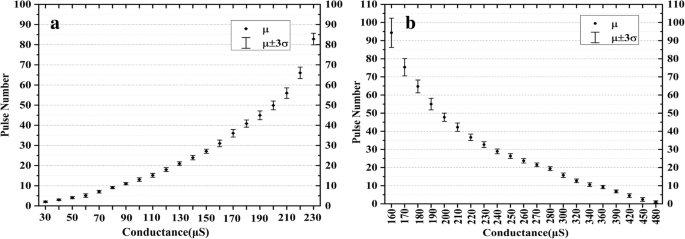

より良いアプローチを図6に示します。デバイスのコンダクタンスは、連続するパルスによって段階的に増加または減少します。パルス幅と間隔は両方とも10μsです。コンダクタンスは、各セット/リセットパルスの後に0.1Vの読み取りパルスによって測定されます。図6に示すように、デバイスをさまざまなレベルに設定/リセットするために必要なパルス数は、印加される電圧によって異なります。 SET電圧として0.5V、リセット電圧として-0.7 Vをそれぞれ選択することにより、セットとリセットによって20レベルの異なる抵抗像が得られます(図7)。デバイスは、目標ステータスに設定する前に毎回10 − 0.9Vの連続パルスでHRSにリセットされるか、調整前に10 0.8Vの連続パルスでLRSに設定されます。セットプロセスとリセットプロセスの両方に同じステータスが存在することを考慮すると、合計で35の異なるステータスが取得されます。セット(リセット)の2つの隣接する抵抗状態に必要なパルス数の偏差が3σレベルを超えています。欠点は、デバイスの抵抗値が大きく変化すると、必要なパルス数が多くなり、動作速度が遅くなることです。

連続するパルスによって調整される抵抗。 a プロセスと b を設定します リセットプロセス

設定に必要なパルス数( a )またはリセット( b )デバイスを20の異なるレベルに

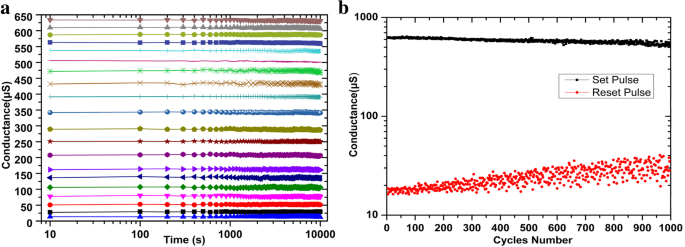

デバイスのデータ保持をテストするために、20個のデバイスが一連の異なる抵抗値に設定/リセットされ、85°Cの加熱テーブルに保持されます[42]。抵抗値は、100秒ごとに0.1Vの電圧で測定されました。図8aから、デバイスの抵抗は10 4 以降も安定していることがわかります。 s。デバイスのサイクル信頼性をテストするために、1.8V /500μsのセットパルスと-1.8V /500μsのリセットパルスでセットとリセットの動作を繰り返しました。 10 3 以降 サイクル中、デバイスのスイッチング比は図8bではまだ10を超えています。

デバイスの信頼性テスト。 a セット/リセットパルス動作後のデータ保持特性。 b セット/リセットパルス動作の耐久曲線を循環させます

結論

提案されたAlドープHfO 2 memristorは、段階的で安定したセット/リセットパフォーマンスを示します。 Alドープデバイスとアンドープデバイスのセットプロセスの曲線をフィッティングすることにより、HRSでは、アンドープデバイスはショットキー発光メカニズムに従い、AlドープデバイスはSCLC導電メカニズムに従うことがわかります。抵抗変化の微視的物理的メカニズムについても説明します。さらに、コンプライアンス電流を変更し、セット/リセットパルス電圧振幅を調整し、連続する短いパルスを使用することにより、デバイスの多値ストレージが確認されました。最後に、デバイスの信頼性をテストして、10 4 を超えるデータ保持があることを証明しました。 s(85°C)および10 3 後のスイッチング比が10を超える サイクル。

データと資料の可用性

この調査中に生成または分析されたすべてのデータは、この公開された記事に含まれています。

略語

- ALD:

-

原子層堆積

- BE:

-

下部電極

- CMOS:

-

補完的な金属酸化物シリコン

- HfD-04:

-

MeCp 2 HfMe(OMe)Hf

- HRS:

-

高抵抗状態

- LRS:

-

低抵抗状態

- NVM:

-

不揮発性メモリ

- SCLC:

-

空間電荷制限電流

- TE:

-

上部電極

- TMA:

-

トリメチルアルミニウム

- XPS:

-

X線光電子分光法

ナノマテリアル

- EclipseHonoでのX.509ベースのデバイス認証

- Nano書記素、シリコンベースの柔軟な透明メモリ

- 原子層堆積によって製造されたPtおよびTiNコーティング基板上のHfO2 / TiO2 / HfO2三層構造RRAMデバイスのバイポーラ抵抗スイッチング特性

- AFMチップベースの動的耕起リソグラフィーを使用したポリマー薄膜上での高スループットのナノスケールピットの製造

- ITO / PtRh:PtRh薄膜熱電対の調製と熱電特性

- 柔軟なポリ(フッ化ビニリデン)圧電フィルムに基づく超高感度ひずみセンサー

- Al / PTFEナノラミネートとの統合に基づく強化されたエネルギー性能

- フィルム摩擦電気ナノ発電機に基づく周波数選択性のためのバイオニック蝸牛基底膜音響センサーの設計

- グラフェン量子ドットで装飾されたZnOナノロッド/ GaN膜アイソタイプヘテロ接合に基づく高性能紫外線光検出器

- Ambarella、Lumentum、ON Semiconductorは、次世代AIoTデバイス向けのAI処理ベースの3Dセンシングで協力しています

- ニオブ窒化チタン薄膜コーティング