性能が向上した新しいドーピングレスフィン型SiGeチャネルTFET

要約

本論文では、ドーピングのないフィン型SiGeチャネルTFET(DF-TFET)を提案し、研究した。高効率のドーピングレスライントンネリング接合を形成するために、フィン型のSiGeチャネルとゲート/ソースのオーバーラップが誘導されます。これらの方法により、オン状態電流が高く、スイッチング比が12桁で、明らかな両極効果がないDF-TFETを得ることができます。高いκ 材料スタックゲート誘電体は、オフ状態のリーク、インターフェース特性、およびDF-TFETの信頼性を向上させるために誘導されます。さらに、ドーピングのないチャネルとフィン構造を使用することにより、ドーピングプロセスと非対称ゲートオーバーラップ形成の問題を解決することができます。その結果、DF-TFETの構造は、優れた製造適用性を備え、フットプリントを大幅に削減できます。この作業では、デバイスの物理的メカニズムとパフォーマンスに対するパラメータの影響を調べます。最後に、オン状態の電流( I オン )58.8μA/μm、最小サブスレッショルドスイング2.8 mV / dec(SS min )、平均サブスレッショルドスイング(SS avg )18.2 mV / decが得られます。改善された容量特性により、5.04GHzのカットオフ周波数と1.29GHzのゲイン帯域幅積を得ることができます。パフォーマンスと堅牢性が向上したDF-TFETは、超低電力アプリケーションにとって非常に魅力的な候補になります。

はじめに

MOSFETのスケールダウンにより、集積回路(IC)のスイッチング速度、高周波性能、密度、コスト、および機能が大幅に向上します[1]。しかし、電圧のスケールダウンが継続的に進行するにつれて、許容できない高電力消費が最新のICにとって深刻な問題になります[1、2]。バンド間トンネリングメカニズムの恩恵を受け、SSが急峻で消費電力が少ないトンネルFET(TFET)は、この問題に新しい解決策をもたらし、多くの注目を集めました[3,4,5,6,7,8,9 ]。しかし、従来のシリコンベースのTFETのアプリケーションは、かなり低いオン状態電流( I )によって制限されます。 オン )、低いスイッチング比、深刻な両極効果、および大きな平均サブスレッショルドスイング(SS)[1、7]。 TFETの性能を向上させるために、近年、TFETへの新しい構造と新しい材料の適用が提案されています。例えば、近年、トンネリングレートが向上した層を備えたTFETが提案されています[5、10、11]。この層を使用すると、トンネリングパスの有効長が短縮され、明らかにトンネリングレートが向上します。さらに、ゲート構造が改善されたTFETは、多くの研究グループによって研究されています[12、13、14、15、16、17、18、19、20]。ライントンネリングの概念はL-TFETで導入されています[17、18、19]。その結果、SS avg 42.8 mV / decadeおよび I オン の10 -6 A /μmはL-TFETで実現できます。 TFETの性能をさらに改善するために、T字型オーバーラップとデュアルソースを備えた改善されたTG-TFETが報告されています[20、21]。その結果、 I オン TG-TFETのは81μA/μmに達します。デバイスの性能をさらに向上させるには、トンネリング接合のドーピングプロファイルに対する高い要件が必要です。ファウンドリエンジニアは、厚さが数ナノメートルしかない超急勾配の急な接合部を作成する必要があり、これを実現するのは非常に困難です。この困難を回避するために、電荷プラズマの概念を使用した真性半導体薄膜上のドーピングレスTFET(DL-TFET)が研究グループによって報告されています[22、23]。 DL-TFETでは、超急峻な急激な接合を取り除くことで、製造の難しさを大幅に軽減できます。ランダムなドーパント変動によって引き起こされる性能低下を回避することができます。さらに、DL-TFETの製造は、ソースとドレインを作成するための高い熱バジェットを必要としないため、ガラス上の単結晶シリコンなどの他の基板上でTFETを実現する可能性が広がります。その結果、DL-TFETのSSが大幅に改善されました。ただし、ポイントトンネリング接合の効率が低いため、DL-TFETの電流は十分に高くなく、現代の回路アプリケーションの増え続ける要件を満たすことは困難です。

本論文では、新しいドーピングのないフィン型SiGeチャネルTFET(DF-TFET)を提案し、研究した。デバイスの性能と堅牢性を向上させるために、ライントンネリング接合とSiGe材料がDF-TFETに適用されます。一方、ゲート金属の仕事関数は、トンネル速度をさらに向上させるために最適化されています。さらに、ドーピングのないチャネルにより製造プロセスの難しさが軽減され、フィン構造により非対称ゲート/バックゲートの製造が可能になります。その結果、オン状態の電流( I オン )58.8μA/μm、オフ状態のリーク電流( I オフ )10 -11 付近 μA/μm、平均サブスレッショルドスイング(SS avg )18.2 mV / decおよび最小サブスレッショルドスイング(SS min )DF-TFETで2.8 mV / decに到達できます。ゲート容量が比較的小さい( C gg )およびゲートからドレインへの容量( C gd )、良好なアナログ/ RF性能を得ることができます。最後に、カットオフ周波数( f T )5.04 GHzに達し、ゲイン帯域幅積(GBW)は1.29GHzに達しました。

この論文の構成は次のとおりです。「デバイスの構造とシミュレーション方法」セクションでは、この作業のTCADシミュレーション方法を示します。 DF-TFETの構造とパラメータを紹介します。 DL-TFETおよびTG-TFETと比較したDF-TFETの違いと利点が示されています。 DF-TFETのメカニズム、特性、およびアナログ/ RF性能については、「結果と考察」のセクションで説明します。このセクションでは、DF-TFET、DL-TFET、およびTG-TFETの性能比較を行います。さらに、このセクションでは、パフォーマンスに対するデバイスパラメータの影響とDF-TFETの一般的なRFパラメータについて説明します。超低電力アプリケーションにおけるDF-TFETの可能性をさらに理解するために、低電圧バイアス下でのさまざまなTFETとDF-TFET間の電気的特性の比較が行われました。

デバイスの構造とシミュレーション方法

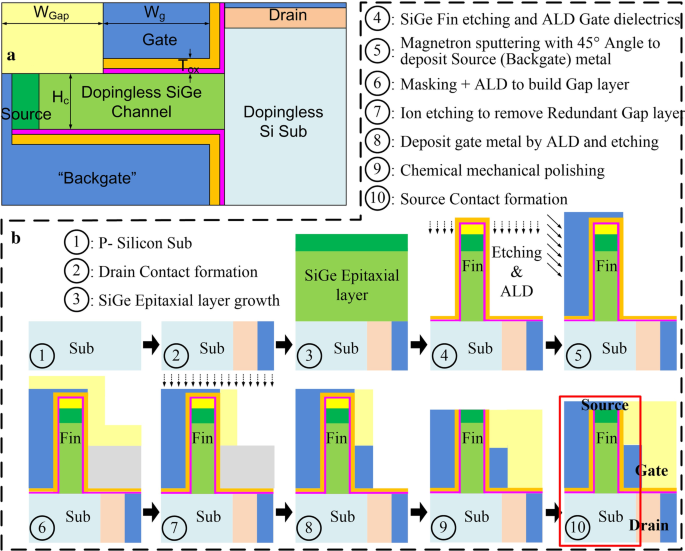

DF-TFETの提案された構造を図1aに示します。デバイスの性能を向上させるために、電荷プラズマの概念により、ドーピングのないフィン型のSiGeチャネルにライントンネリング接合が適用されます[24、25]。ゲート誘電体の厚さがトンネル電流に大きな影響を与える可能性があることが知られています。これは、式(1)に示すように、WKB近似[26]の結果であるためです。 (1)、トンネリング確率は有効スクリーニング長(λ)に依存します )、有効キャリア質量( m * )、エネルギーバンドギャップ( E g )および効果的なスクリーニングエネルギーウィンドウ(ΔΦ 。

$$ T _ {{{\ text {WKB}}}} \ approx \ exp \ left({-\ frac {{4 \ lambda \ sqrt {2m ^ {*}} \ sqrt {E _ {{\ text {g} }} ^ {3}}}} {{3q \ hbar(E _ {{\ text {g}}} + \ Delta \ Phi)}}} \ right)$$(1)

a 構造と b DF-TFETの製造フロー

ゲート誘電体の厚さを薄くするか、高いκを使用します 誘電体はλを減らします ΔΦを増やします 、これにより、トンネリング確率が指数関数的に増加します。したがって、高いκを使用する 誘電体と誘電体の厚さを減らすと、TFETのオン状態電流が大幅に増加する可能性があります。しかし、高いκの小さな誘電体の厚さと界面品質の問題 誘電体は深刻な信頼性の問題を引き起こします。したがって、0.5nmのAl 2 のスタックゲート誘電体 O 3 および2.0nmのHfO 2 は、良好なインターフェース品質を保証するように設定されています[27、28、29]。これにより、リーク電流を大幅に削減し、ゲート誘電体の信頼性を向上させることができます。ソース電極はフィン構造の上部にあります。同時に、フィンの片側の隣にもあり、ゼロバイアスを適用するための「バックゲート」として機能します。異なる金属仕事関数を持つゲート電極とソース電極を使用することにより、電荷プラズマの概念により、ドーピングのないフィン型のSiGeチャネルにライントンネリング接合を形成できます。バンド間トンネリング(BTBT)の方向は、チャネル/ゲート表面に垂直です。これは、 I を増やすのに役立ちます オン 有効なトンネリングジャンクションエリアを改善することによって。

高いスイッチング比( I オン / 私 オフ )は、オン状態の電流が大きいために得られます( I オン )および小さなオフ状態電流( I オフ )ライントンネリングジャンクションによって提供されます。さらに、DF-TFETにフィン構造を適用すると、プレーナーライントンネリングTFETと比較してフットプリントを大幅に削減できます[30、31]。図1bは、DF-TFETの構造を形成するために利用可能な製造フローを示しています。表1に、DF-TFETの主なプロセスパラメータを示します。最後に、急勾配で均一な急激なp-n接合を作成するのが困難になることなく、優れたデバイスパフォーマンスと堅牢性を実現できます。

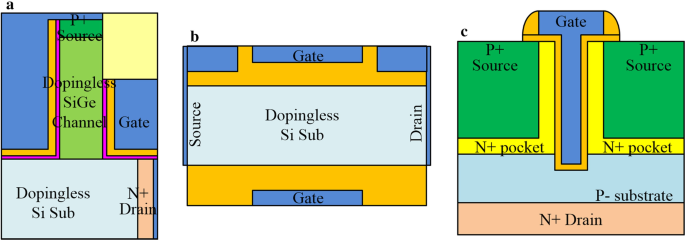

<図>DF-TFET、DL-TFET、TG-TFETの違いと利点をよりよく理解するために、図2にこれら3つのデバイスの構造を示します。ライントンネル接合により、L-TFETとTG-TFETは高いオン状態電流を得ることが期待されます。しかし、実験結果は、L-TFETの実際の性能が期待したほど高くないことを示しています[18、19]。最も重要な理由の1つは、完全な界面特性を備えた急勾配で均一な急激なp-n接合を形成することが難しいことです。 L-TFETの構造に基づいて、TG-TFETは I を大幅に改善します。 オン 。しかし、TG-TFETは、完全な突然のp-n接合を形成するという困難に依然として直面しています。したがって、望ましい良好な性能を得るには、厚さがわずか数ナノメートルの急勾配で均一な急激なp-n接合を得る必要がありますが、製造プロセスで実現することは非常に困難です。ドーピングレスチャネルを使用することにより、DL-TFETはこの問題を回避し、トンネル接合の近くでより良いインターフェース品質をもたらすことができます。ただし、急激なp-n接合を持つライントンネリングTFET [16、17、18、19、20、21]と比較すると、シミュレーション結果は I オン DL-TFETの割合は比較的低い[22、23]。さらなる改善のために、DF-TFETが提案され、この作業で研究されています。

a の構造 DF-TFET、 b DL-TFET、 c TG-TFET

DF-TFETのシミュレーションは、Silvaco AtlasTCADツールで実行されます。このシミュレーションでは、非ローカルBTBTモデルを導入して、エネルギーバンドの空間的変動を考慮に入れます。これにより、BTBTトンネリングプロセスの精度を向上させることができます。ロンバルディモビリティモデルは、チャネルモビリティを正確にするために考慮されています。バンドギャップナローイングモデルは、高濃度にドープされたオーミック接触領域に適合するように考慮されており、Shockley–Read–Hall再結合モデルもこの論文で考慮されています。

結果と考察

DF-TFET、DL-TFET、TG-TFETのメカニズムと比較

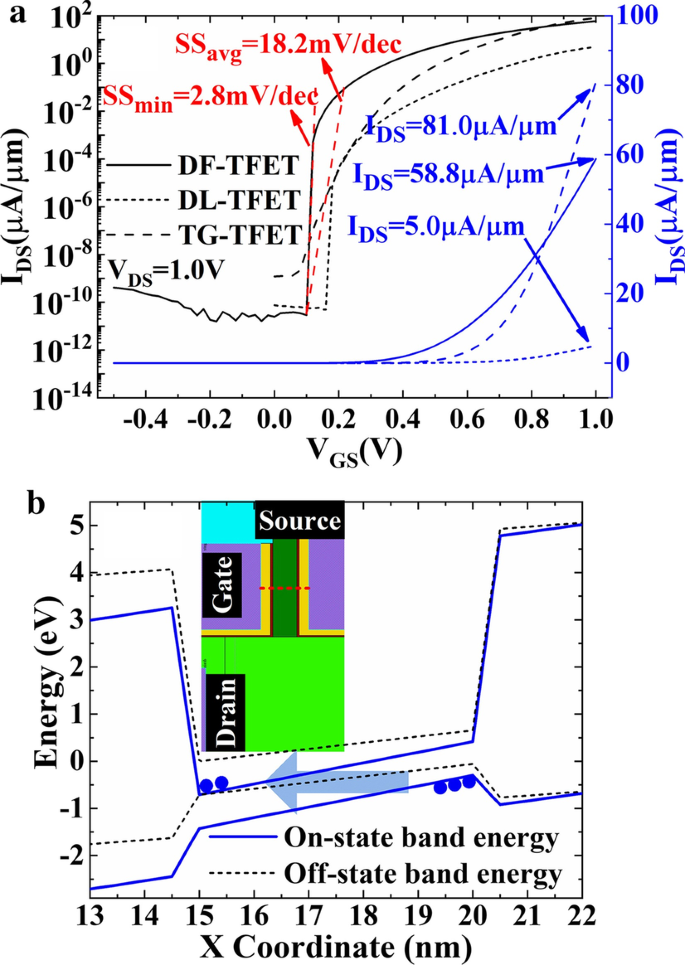

図3aは、DF-TFET、DL-TFET、およびTG-TFETの伝達特性の比較を示しています。フィン型のSiGeチャネルのライントンネル接合の恩恵を受けて、DF-TFETはオン状態の電流( I )に到達します。 オン )58.8μA/μmであり、明らかな両極効果が発生しない12桁を超える大きなスイッチング比を実現します。さらに、最小サブスレッショルドスイング(SS min )2.8 mV / decおよび平均サブスレッショルドスイング(SS avg )18.2 mV / decが得られます。その結果、DF-TFETの I は明らかに改善されています。 オン DL-TFETと比較して、TG-TFETと比較してサブスレッショルドスイング。 私 オン DF-TFETのサイズは、 V でDL-TFETよりも1桁以上大きくなります。 DS = V GS =1V。図3bは、DF-TFETのエネルギー帯域の状態を示し、フィン型チャネルでのトンネルウィンドウの形成を示しています。図3bの挿入図の赤い点線は、エネルギーバンド曲線が得られる位置を示しています。

a DF-TFET、DL-TFET、TG-TFETの伝達特性。 b さまざまな作業条件でのDF-TFETのエネルギーバンド条件(挿入図はカットラインの位置を示しています)

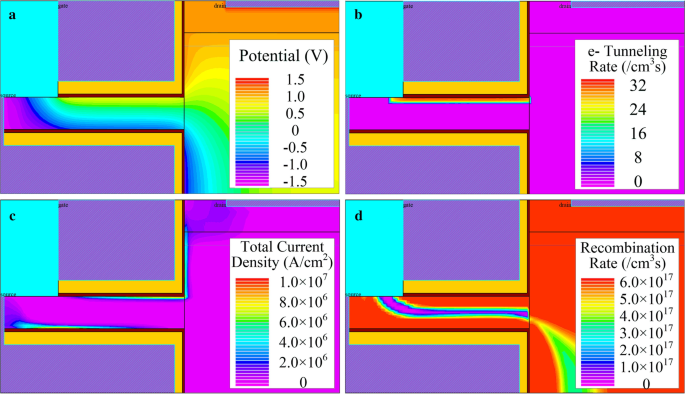

DF-TFETのトンネリングプロセスにおける重要な物理量の分布を図4に示します。これには、(a)電位、(b)eトンネリング速度、(c)総電流密度、および(d)再結合速度の分布が含まれます。状態の作業条件。図4aでは、ゲート/チャネル界面に垂直な明確な電位勾配を観察できます。このように、フィン状のチャネルに大きな電位差が生じ、これによりフィンチャネルの両側の電子と正孔の濃度が変調されます。同時に、フィン型のチャネルに急なエネルギーバンドの曲がりを形成することができます。その結果、ゲート/チャネル界面に平行なライントンネリング接合を形成することができます。図4bは、フィン構造チャネルの電子トンネリング速度を示しています。電子トンネリング速度のピーク値は、ゲート/チャネル界面の近くで、表面に平行に均一に分布しています。これは、ライントンネリングジャンクションがゲート/チャネルインターフェイスに平行であることを証明しています。図4cは、DF-TFETの電流パスを示しています。バックゲート/チャネル側からの価電子帯電子は、ゲート/チャネル側近くの伝導帯にトンネリングしています。ゲート電圧とドレイン電圧の影響下で、電子はフィンチャネルに沿ってドレイン電極に移動します。このようにして、DF-TFETにトンネル電流経路が形成されます。図4dは、DF-TFETの再結合率分布を示しています。これにより、トンネリングジャンクションの位置をより明確に示すことができます。 SiGeフィンチャネルの紫色の帯は、トンネリングジャンクションの位置を表すことができます。

a の配布 可能性、 b eトンネリングレート、 c 電流密度と d DF-TFETの再結合率

さまざまなパラメータとアナログ/ RF性能を備えたDC特性

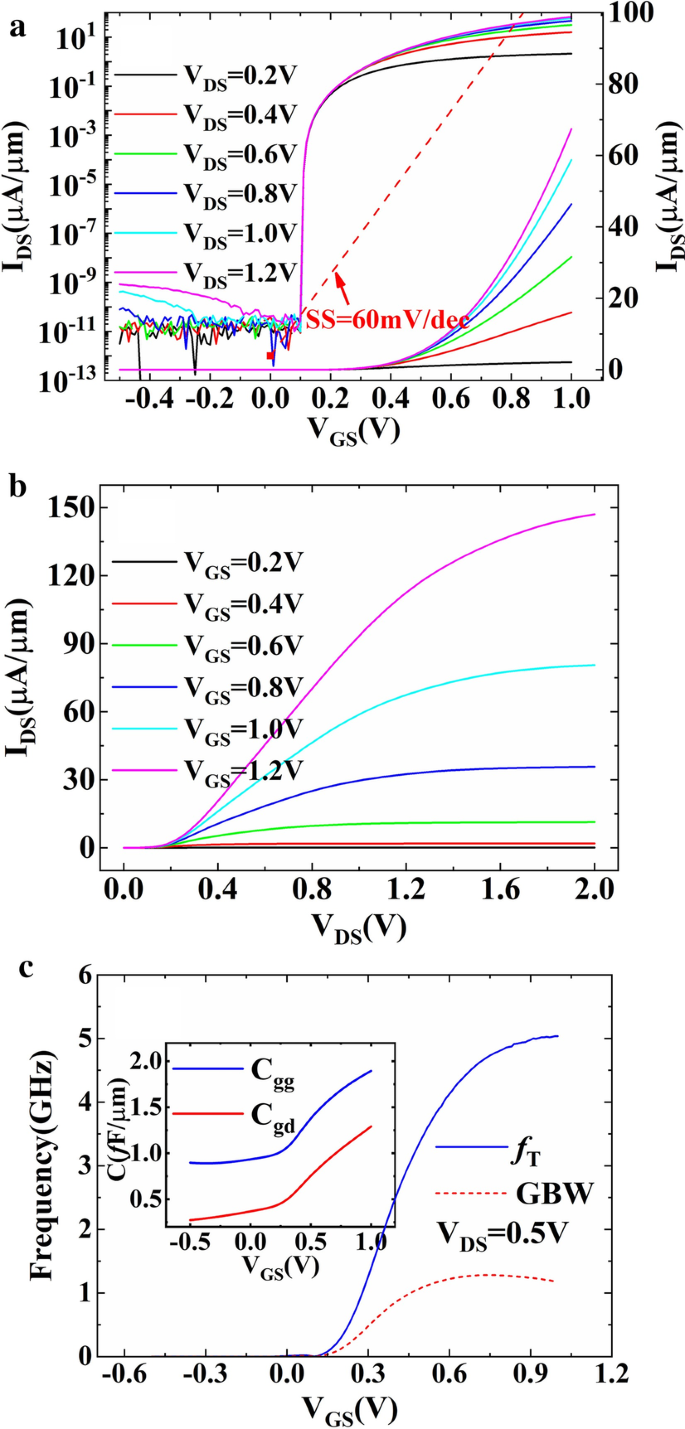

図5a、bは、さまざまなバイアス下でのDF-TFETの入力および出力特性を示しています。 V の増加 DS サブスレッショルドスイング特性にはほとんど影響しませんが、 I オン V の間、直線的に成長します DS 0.2から1.2Vに増加します( V で GS =1.0 V)。図5cは、カットオフ周波数( f )を示しています。 T )および式によって計算されたゲイン帯域幅積(GBW)。 (2)と(3)。結果は、5.04GHzのカットオフ周波数と1.29GHzのゲイン帯域幅積が得られることを示しています。

$$ f _ {{\ text {T}}} =\ frac {{g _ {{\ text {m}}}}} {{2 \ pi C _ {{{\ text {gs}}}} \ sqrt {1 + 2C _ {{{\ text {gd}}}} / C _ {{{\ text {gs}}}}}}} \ approx \ frac {{g _ {{\ text {m}}}}} {{2 \ pi \ left({C _ {{{\ text {gs}}}} + C _ {{{\ text {gd}}}}} \ right)}} =\ frac {{g _ {{\ text {m} }}}} {{2 \ pi C _ {{{\ text {gg}}}}}} $$(2)$$ {\ text {GBW}} =g _ {{\ text {m}}} / 2 \ pi 10C _ {{{\ text {gd}}}} $$(3)

a 入力、 b 出力と c DF-TFETの無線周波数特性

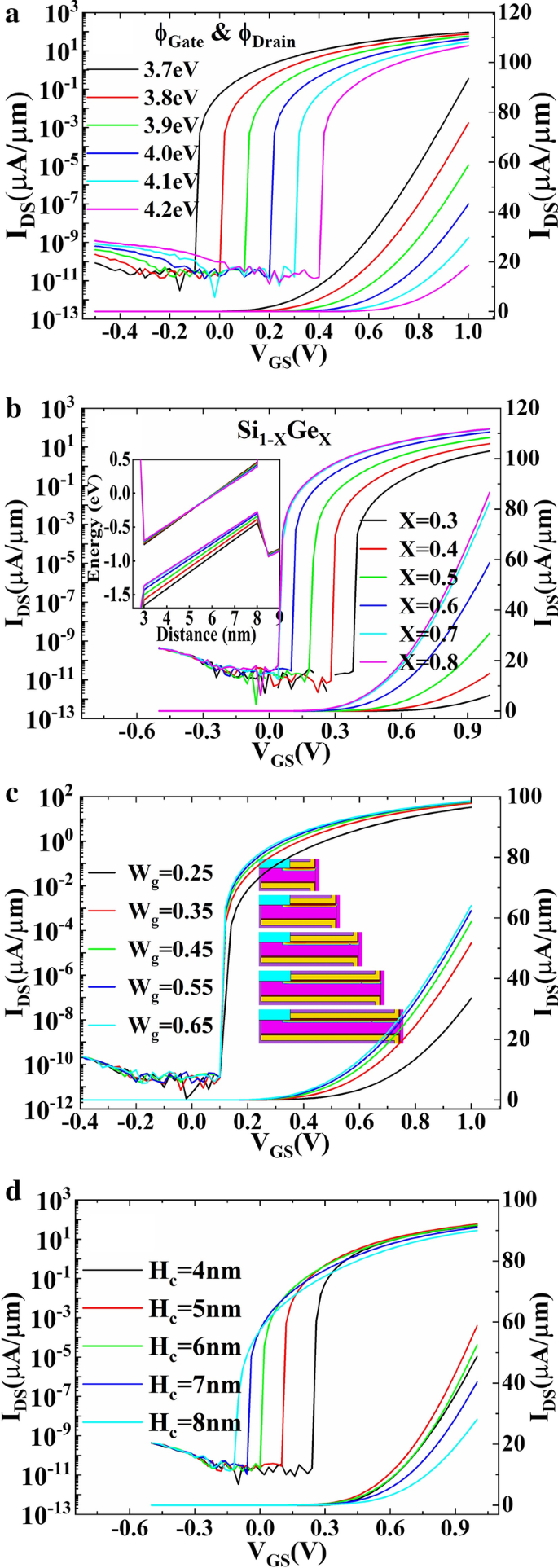

図6aは、ゲート仕事関数(φ)の効果を示しています。 ゲート )および排水仕事関数(φ ドレイン )DF-TFETの伝達特性について。仕事関数の増加に伴い、伝達特性曲線は正の方向にシフトします。仕事関数は3.7から4.2eVまで変化するため、 V th I が0から0.5Vまで直線的に増加します オン 93.4から18.6μA/μmまで直線的に減少します。これにより、 V を調整できます th さまざまなアプリケーション要件に適用します。図6bは、組成比 X の効果を示しています。 Si 1- X の Ge X 。図6bの挿入図に示すように、ゲルマニウム組成の増加は、エネルギーバンドギャップの減少とトンネリングウィンドウの増加につながります。最後に、結果は I オン 増加および伝達特性曲線は、負の方向に変換されます。ただし、 X の場合> 0.7、伝達特性曲線と I の両方 オン X の増加に伴う変化はほとんどありません 。これは、チャネルエネルギーバンド構造が X の影響を受けなくなるためです。 X の場合> 0.7、図6bの挿入図に示すように。図6c、dは、ゲート長( W )の影響を示しています。 g )およびチャネルの厚さ( H c )伝達特性について。図6cの挿入図は、さまざまな W でのデバイスチャネルの寸法を示しています。 g 。図6dから、DF-TFETが I に苦しむことを観察するのは難しくありません。 オン H のときに減少します c 小さすぎたり大きすぎたりします。したがって、適切な H c デバイスのパフォーマンスにメリットがあります。

異なる a の伝達特性 ゲート仕事関数(φ ゲート )および排水仕事関数(φ ドレイン )、 b SiGe組成比、 c ゲート長( W g )および d チャネルの厚さ( H c )

超低電力アプリケーションにおけるDF-TFETの可能性を理解するために、表2に、さまざまなTFETとDF-TFETの性能比較を示します。従来の高濃度にドープされたp–nトンネリング接合を備えたTFET [6、20、32、33、34、35]と比較して、DF-TFETはSSとスイッチング比に明らかな利点があります。これは、静電ドーピングを使用したDF-TFETの特性によるものです。他のドーピングレスTFET [22、23、36、37]と比較して、DF-TFETにはI ON で明らかな利点があります。 。これは、ライントンネル接合とSiGe材料を使用することでトンネル速度が向上したためです。 DF-TFETは、p–nトンネリング接合とドーピングレストンネリング接合の利点を組み合わせることにより、超低電力アプリケーションで高い動作電流と低い静的消費電力を提供できます。

<図>結論

この研究では、新しいDF-TFETを提案し、電気的特性をシミュレーション法で分析します。 DF-TFETの構造特性、物理的メカニズム、さまざまなパラメータでの性能、およびアナログ/ RF性能について説明および調査します。ドーピングレスフィン構造チャネル、スタックゲート誘電体、SiGeチャネル材料、および高効率ライントンネリング接合の恩恵を受けて、スイッチング特性およびアナログ/ RF特性で優れた性能を得ることができます。さらに、製造プロセスでの急激なp-n接合の形成を回避することにより、プロセス変動に対する高い一貫性と高い堅牢性を備えた均一なドーピングを実現できます。シミュレーション結果は、 I オン 58.8μA/μm、12桁のスイッチング比、明らかな両極効果なし、SS min 2.8 mV / decおよび f T 5.04 GHzは、DF-TFETによって実現できます。大きな動作電流、高いスイッチング比、急峻なSS、優れた信頼性、安定した製造プロセス、および優れた製造性により、将来の低電力ICおよび高感度センサーアプリケーションの有望な候補の1つとして期待できます。

データと資料の可用性

該当なし(この原稿は、TFETのアナログ/ RF性能に関する純粋に理論的な研究です。シミュレーションデータはこの原稿に記載されており、ここでは説明しません)。

略語

- DF-TFET:

-

ドーピングのないフィン型SiGeチャネルTFET

- IC:

-

集積回路

- TGTFET:

-

T字型ゲートデュアルソースTFET

- DL-TFET:

-

ドーピングレスTFET

- I オン :

-

オン状態電流

- I オフ :

-

オフ状態電流

- SS min :

-

最小サブスレッショルドスイング

- SS avg :

-

平均サブスレッショルドスイング

- C gg :

-

ゲート容量

- C gd :

-

ゲートからドレインへの静電容量

- f T :

-

カットオフ周波数

- GBW:

-

ゲイン帯域幅積

- λ :

-

有効なスクリーニングの長さ

- m * :

-

有効キャリア質量

- E g :

-

エネルギーバンドギャップ

- ΔΦ :

-

効果的なスクリーニングエネルギーウィンドウ

- W g :

-

ゲートの長さ

- W ギャップ :

-

ギャップの長さ

- T ox :

-

スタックゲート酸化物の厚さ

- H c :

-

チャネルの厚さ

- φ ゲート / φ ドレイン :

-

ゲートおよびドレンの仕事関数

- V DS :

-

ソース電圧へのドレイン

- V GS :

-

ゲートからソースへの電圧

ナノマテリアル

- 新しいアプローチにより、PUFの安定性が向上します

- 自動溶接でパフォーマンスを向上させる

- ブログ:優れたパフォーマンスを備えた医療用ウェアラブル

- 光触媒性能が向上した新規Bi4Ti3O12 / Ag3PO4ヘテロ接合光触媒

- グリセロール燃料電池の電気酸化用の新しい陽極PdAu / VGCNF触媒の性能の向上

- 窒化処理を施したHfO2ベースのRRAMの伝導メカニズムと耐久性の向上

- 光触媒性能を改善するための階層的ZnO @ NiOコア-シェルヘテロ構造の製造

- V溝キャビティを備えたチャネルプラズモンナノワイヤレーザー

- Ge / Siチャネル形成とデバイス性能に及ぼすエッチング変動の影響

- 表面構造が変更された高性能有機ナノ構造シリコンハイブリッド太陽電池

- リリース4.6でProtocaseDesignerを改善した6つの方法