エッジトリガーラッチ:フリップフロップ

これまで、イネーブル入力を備えたS-RおよびDラッチ回路の両方を研究してきました。ラッチは、イネーブル入力がアクティブになっている場合にのみデータ入力(S-RまたはD)に応答します。ただし、多くのデジタルアプリケーションでは、ラッチ回路の応答性を、イネーブル入力がアクティブ化される期間全体ではなく、非常に短い期間に制限することが望ましいです。

マルチバイブレータ回路を有効にする1つの方法は、エッジトリガーと呼ばれます。 、ここで、回路のデータ入力は、イネーブル入力が遷移している間だけ制御できます。 ある州から別の州へ。

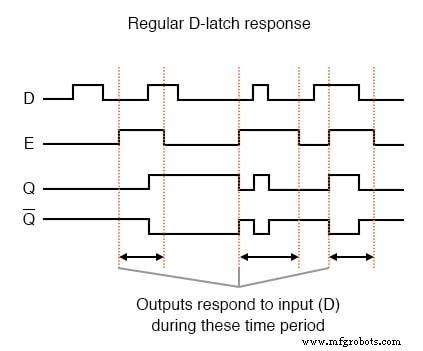

通常のDラッチとエッジトリガーのタイミング図を比較してみましょう:

最初のタイミング図では、イネーブル(E)入力がハイのときはいつでも、出力は入力Dに応答しますが、それがハイのままである間はいつでもです。イネーブル信号がロー状態にフォールバックすると、回路はラッチされたままになります。

2番目のタイミング図では、回路出力の応答が明らかに異なることに注意してください。これは、イネーブル信号が変化するその短い瞬間にのみD入力に応答します。 、またはトランジション 、低から高へ。これはポジティブとして知られています エッジトリガー。

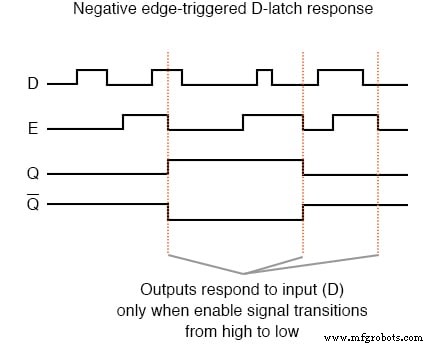

ネガティブのようなものがあります エッジトリガーも同様で、同じ入力信号に対して次の応答を生成します。

方形波イネーブル信号の遷移エッジでマルチバイブレータ回路をイネーブルする場合は常に、それをフリップフロップと呼びます。 ラッチの代わりに 。

したがって、エッジトリガーS-R回路はS-Rフリップフロップとしてより適切に知られ、エッジトリガーD回路はDフリップフロップとしてより適切に知られています。イネーブル信号の名前が clock に変更されます 信号。また、これらのフリップフロップのデータ入力(それぞれ、S、R、およびD)を同期と呼びます。 入力は、クロックパルスのエッジ(遷移)時にのみ有効であるため、データ入力の気まぐれではなく、出力の変化をそのクロックパルスと同期させます。

しかし、実際にこのエッジトリガーをどのように達成するのでしょうか。通常のS-Rラッチから「ゲート付き」S-Rラッチを作成するには、いくつかのANDゲートを使用するだけで十分ですが、立ち上がりエッジまたは立ち下がりエッジのみに注意を払うロジックを実装するにはどうすればよいですか。 変化するデジタル信号の?

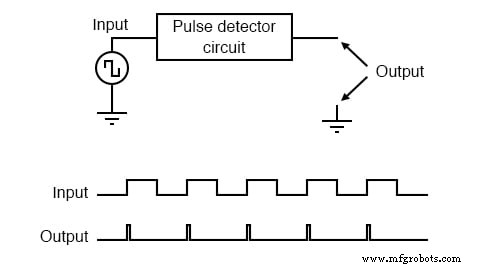

必要なのは、入力が任意の期間アクティブになるたびに短いパルスを出力するデジタル回路です。この回路の出力を使用して、ラッチを短時間有効にすることができます。ここでは少し先を進んでいますが、これは実際には一種の単安定マルチバイブレータであり、今のところパルス検出器と呼びます。 。

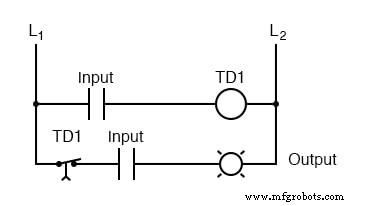

各出力パルスの持続時間は、パルス回路自体のコンポーネントによって設定されます。ラダーロジックでは、これは非常に短い遅延時間で時間遅延リレーを使用することで非常に簡単に実現できます。

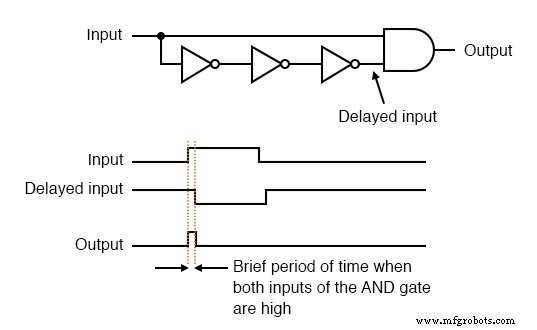

このタイミング関数を半導体コンポーネントで実装することは、すべての論理ゲートに固有の時間遅延(伝搬遅延として知られている)を利用するため、実際には非常に簡単です。 )。入力信号を取得して2つの方法で分割し、1つまたは一連のゲートをこれらの信号パスの1つに配置して少し遅延させ、元の信号と遅延した対応する信号の両方を入力します。遅延信号が非遅延信号の低から高への変化にまだ追いついていない短い時間の間、高信号を出力する2入力ゲート。低から高への入力信号遷移でクロックパルスを生成するための回路例を次に示します。

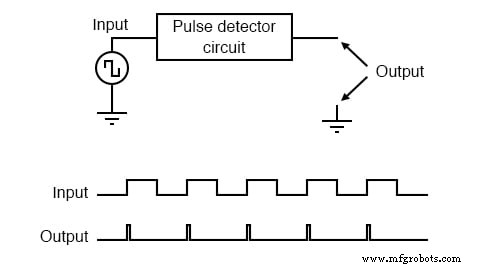

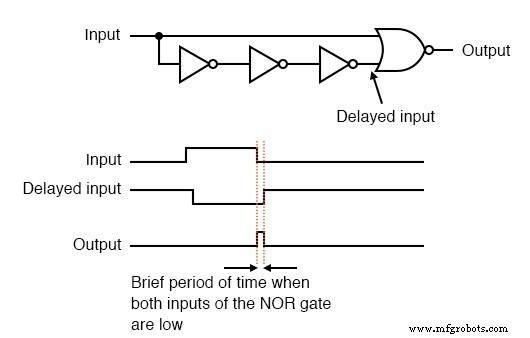

この回路は、最終ゲートをANDからNORに変更するだけで、ネガティブエッジパルス検出回路に変換できます。

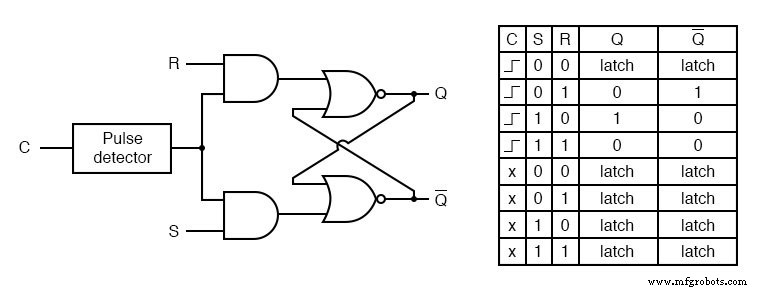

パルス検出器の作成方法がわかったので、ラッチのイネーブル入力に接続してフリップフロップに変換する方法を示します。この場合、回路はS-Rフリップフロップです:

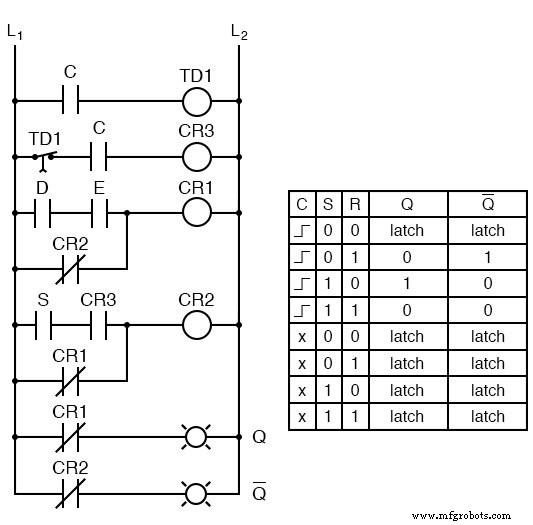

クロック信号(C)がローからハイに遷移しているときにのみ、回路はSおよびR入力に応答します。クロック信号(「x」)の他の条件では、回路はラッチされます。

S-Rフリップフロップのラダーロジックバージョンを次に示します。

リレー接点CR 3 ラダー図では、S-Rラッチ回路の古いE接点に取って代わり、Cが閉じて時間遅延接点TR 1 の両方が閉じている短時間の間にのみ閉じます。 閉じています。どちらの場合(ゲートまたはラダー回路)でも、Cがロー(0)状態からハイ(1)状態に遷移しない限り、入力SとRは効果がないことがわかります。それ以外の場合、フリップフロップの出力は以前の状態でラッチします。

S-Rフリップフロップの無効な状態が維持されるのは、パルス検出回路によってラッチを有効にすることができる短時間だけであることに注意することが重要です。その短い時間が経過すると、出力はセット状態またはリセット状態のいずれかにラッチされます。繰り返しになりますが、競合状態の問題 現れます。イネーブル信号がないと、無効な出力状態を維持できません。ただし、マルチバイブレータの有効な「ラッチ」状態(セットとリセット)は、相互に排他的です。したがって、マルチバイブレータ回路の2つのゲートは、優位性を求めて互いに「競合」し、どちらかが最初に高出力状態になった方が「勝ち」ます。

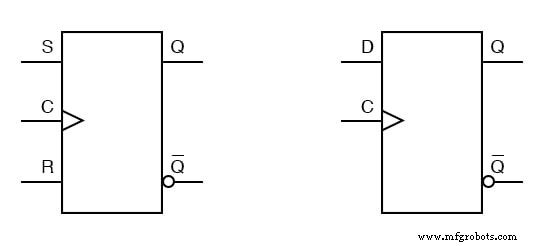

フリップフロップのブロックシンボルは、対応するラッチのブロックシンボルとは少し異なります。

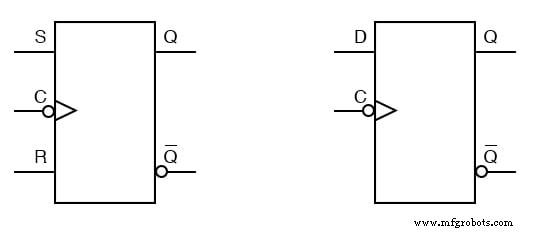

クロック入力の横にある三角形の記号は、これらがエッジトリガーデバイスであり、その結果、これらがラッチではなくフリップフロップであることを示しています。上記のシンボルは、ポジティブエッジでトリガーされます。つまり、クロック信号の立ち上がりエッジ(ローからハイへの遷移)で「クロック」します。ネガティブエッジトリガーデバイスは、クロック入力ライン上のバブルで表されます:

上記の両方のフリップフロップは、クロック信号の立ち下がりエッジ(ハイからローへの遷移)で「クロック」します。

レビュー:

- フリップフロップ は、イネーブル(E)入力に接続された「パルス検出器」回路を備えたラッチ回路であるため、クロックパルスの立ち上がりエッジまたは立ち下がりエッジのいずれかで短時間だけ有効になります。

- パルス検出器回路は、ラダーロジックアプリケーション用の時間遅延リレーから、または半導体ゲートから作成できます(伝搬遅延の現象を利用 。

関連するワークシート:

- ビーチサンダルワークシート

産業技術