シフトレジスタの概要

シフトレジスタは、カウンタと同様に、シーケンシャルロジックの形式です。 。

シーケンシャルロジックは、組み合わせロジックとは異なり、現在の入力だけでなく、以前の履歴の影響も受けます。

つまり、シーケンシャルロジックは過去のイベントを記憶します。

シフトレジスタは、デジタル信号または波形の離散遅延を生成します。

クロックに同期した波形 、繰り返される方形波は、「n」だけ遅延します 「n」の個別のクロック時間 はシフトレジスタのステージ数です。

したがって、4ステージシフトレジスタは、「データ入力」を4クロック遅延させて「データ出力」します。

シフトレジスタのステージは遅延ステージです。 、通常は「D」と入力します ビーチサンダルまたは「JK」と入力します ビーチサンダル。

以前は、非常に長い(数百ステージ)シフトレジスタがデジタルメモリとして機能していました。

この廃止されたアプリケーションは、初期のコンピュータメモリとして使用されていた音響水銀遅延線を彷彿とさせます。

メートルからキロメートルの距離にわたるシリアルデータ送信では、シフトレジスタを使用してパラレルデータをシリアル形式に変換します。

シリアルデータ通信は、多くの低速パラレルデータワイヤを単一のシリアル高速回路に置き換えます。

数十センチメートルの短距離のシリアルデータは、シフトレジスタを使用してマイクロプロセッサにデータを出し入れします。

アナログ-デジタルコンバーター、デジタル-アナログコンバーター、ディスプレイドライバー、メモリなど、多数の周辺機器がシフトレジスタを使用して、回路基板の配線量を削減しています。

一部の特殊なカウンタ回路は、実際にシフトレジスタを使用して繰り返し波形を生成します。

フィードバックの助けを借りて、より長いシフトレジスタは、ランダムノイズ、疑似ノイズのように見えるほど長いパターンを生成します 。

基本的なシフトレジスタは、次のタイプに従って構造によって分類されます。

- シリアルイン/シリアルアウト

- パラレルイン/シリアルアウト

- シリアルイン/パラレルアウト

- ユニバーサルパラレルイン/パラレルアウト

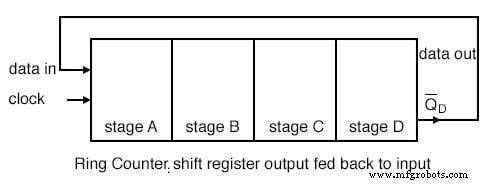

- リングカウンター

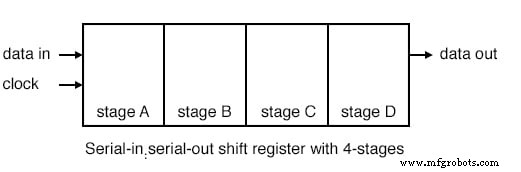

上に、4段の長さのシリアル入力/シリアル出力シフトレジスタのブロック図を示します。

入力のデータは、シフトレジスタの入力から出力まで4クロック周期遅れます。

上記の「datain」のデータは、ステージ A に表示されます。 最初のクロックパルスの後に出力します。 2番目のパルスステージの後 A データはステージ B に転送されます 出力され、「データ入力」がステージ A に転送されます 出力。 3番目の時計の後、ステージ C ステージ B に置き換えられます;ステージ B ステージ A に置き換えられます;ステージAは「データ入力」に置き換えられます。

4番目のクロックの後、「データ入力」に元々存在していたデータは、ステージ D にあります。 、「出力」。

「ファーストイン」データは、「データイン」から「データアウト」にシフトされるため、「ファーストアウト」になります。

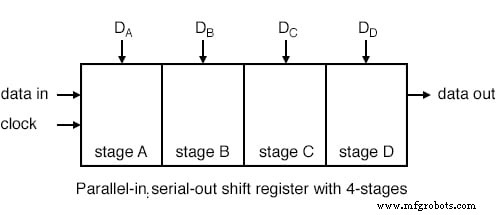

データは、パラレルイン/シリアルアウトシフトレジスタのすべてのステージに一度にロードされます。

次に、データはクロックパルスによる「データ出力」を介してシフトアウトされます。上に4ステージのシフトレジスタが示されているため、すべてのデータをシフトアウトするには4つのクロックパルスが必要です。

上の図では、ステージ D データは、最初のクロックパルスまで「データ出力」に存在します。ステージ C データは、最初のクロックと2番目のクロックパルスの間の「データ出力」に存在します。ステージ B データは2番目のクロックと3番目のクロックの間に存在します。ステージ A データは3番目と4番目のクロックの間に存在します。

4番目のクロックパルスの後、およびその後、「データ入力」の連続するビットは、4クロックパルスの遅延後にシフトレジスタの「データ出力」に現れるはずです。

4つのスイッチがD A に接続されている場合 D D を介して 、ステータスは、1つのデータピンとクロックピンのみを使用してマイクロプロセッサに読み込むことができます。

スイッチを追加するのにピンを追加する必要がないため、このアプローチは多くの入力にとって魅力的に見えます。

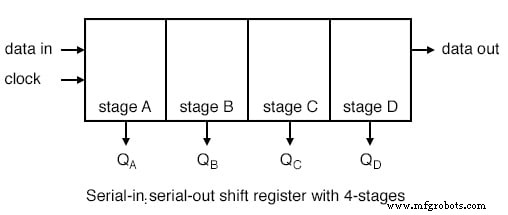

上記では、4つのデータビットが「データ入力」から4クロックパルスだけシフトインされ、Q A で使用可能になります。 Q D を介して LED、ランプ、リレードライバ、ホーンなどの外部回路を駆動するため。最初のクロックの後、「datain」のデータがQ A に表示されます。 。

2番目の時計の後、古いQ A データはQ B に表示されます; Q A 「データ入力」から次のデータを受信します。 3番目のクロックの後、Q B データはQ C にあります 。

4番目のクロックの後、Q C データはQ D にあります 。このステージには、「datain」に最初に存在するデータが含まれます。これで、シフトレジスタに4つのデータビットが含まれるはずです。

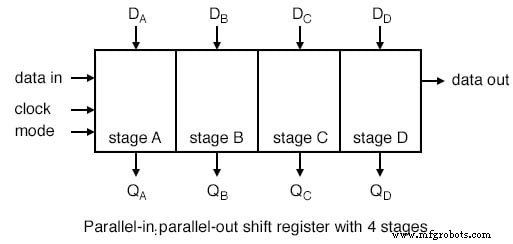

パラレルイン/パラレルアウトシフトレジスタは、パラレルイン、シリアルアウトシフトレジスタの機能とシリアルイン、パラレルアウトシフトレジスタの機能を組み合わせて、ユニバーサルシフトレジスタを生成します。

「何でもできる」シフターには代償が伴います。I/ O(入力/出力)ピンの数が増えると、パッケージ化できるステージの数が減る可能性があります。

D A で提示されたデータ D D を介して レジスタに並列ロードされます。

Q A でのこのデータ Q D を介して クロック入力に提示されるパルス数によってシフトされる場合があります。

シフトされたデータはQ A で入手できます。 Q D を介して 。

「モード」入力は、複数の入力である場合があり、D A からのデータの並列ロードを制御します。 D D を介して 、データのシフト、およびシフトの方向。

データを左または右にシフトするシフトレジスタがあります。

シフトレジスタのシリアル出力がシリアル入力に接続されている場合、クロックパルスが存在する限り、データはリングの周りで永続的にシフトできます。

上記のようにフィードバックされる前に出力が反転されている場合は、初期データを「リングカウンター」にロードすることを心配する必要はありません。

関連するワークシート:

- シフトレジスタワークシート

産業技術