QFN 向けの優れた PCB パッド設計を保証する要素

小型化、軽量化、高性能化に向けた電子部品パッケージ技術の発展に伴い、部品の機能密度を高め、入力端子と出力端子間の間隔を狭くすることが電子部品の開発傾向であり、これは自動組立技術によって最もよく示されています。 SMT(表面実装技術)による。コンポーネントの表面実装を実装するための最初のステップは、構造化された PCB が得られるように、PCB 上に対応するパッドを製造することです。次に、ステンシル印刷技術を適用して、PCB パッドの表面にはんだペーストを覆います。最後に、加熱を行ってはんだペーストを液体に変換し、コンポーネントのピンと PCB パッドの間に液体ブリッジを形成します。 PCB 上のはんだマスクの影響下で、はんだ接合部間のブリッジングを防止するために、対応するはんだパッド領域で溶融はんだペーストが制限され、PCB 上のチップの自動アセンブリが実装されます。さまざまなパッケージ タイプに応じて、円形および長方形のはんだパッド、つまり BGA (ボール グリッド アレイ) および QFN (クワッド フラット ノーリード) パッケージが主に選択されます。 BGA についてもっと知りたい場合は、4 つのステップだけで十分です。

QFN ウィキ

パッケージの種類が異なる他のコンポーネントと比較して、QFN パッケージは、PCB または FPC 基板に直接はんだ付けするように設計されています。底部に金属パッドが露出しているため、放熱性が向上します。さらに、QFN パッケージは、拡張パッケージのコンポーネントよりもピンが短いため、優れた電気的性能を備えています。したがって、PCB の高い信頼性と性能を維持および保証できるように、PCB 上の QFN パッドを設計することは非常に重要です。

ぬれ角

QFN のピンのサイズとピン間の間隔は比較的小さいため、錫ペーストの塗布量が正確であるため、はんだブリッジや疑似はんだが発生する可能性があります。したがって、ステンシルの厚さ (h0) に基づく PCB のパッド サイズの合理的な設計 ) はんだ付けの成功率に大きく役立ちます。はんだパッド上のはんだ錫のぬれ角 (θa ) は 30° で、はんだマスク上のはんだスズのぬれ角 (θr ) は 160° です。ぬれ角は、パッド表面の粗さを無視すれば、おおよそ三相接触線の前進角または後退角とみなすことができます。 QFNコンポーネントの実際のはんだ付け技術に従って、はんだスズが完全に溶融し、パッド表面が濡れているという理想的な条件下でのリフローはんだ付けの温度曲線を適切に制御することで、はんだ付け効率を確保し、コンポーネントが自動アセンブリはんだ付けバランスに達するのを助けることができます。パッドが合理的に設計されている場合、はんだ接合の理想的な状態は、PCB の電気的性能と機械的接続の要件を満たすだけでなく、ブリッジングや疑似はんだ付けなどのはんだ接合の障害を回避します。その観点から、はんだ接合の状態は次の式を満たす必要があります:

を。 QFN 内部のはんだ接合部が PCB パッド上に完全に分布している場合、θa ≤θj (Zu )≤θr , θj (0)=30°、x3 (0)=x4 (0)=Dx4

b. QFN の外側のスズがサイド パッドで成長している場合、

(1) θj (Zu )=θs3 +90°、θ4 (0)=30°、θ3 (0)=30°,

(2)×3 (0)=x4 (0)=Dx4 (0), x3 (Zu )=0.

パッドのデザイン

この式では、θs3 θa に等しい どちらもサイド パッド上のはんだスズのぬれ角です。

垂直方向では、架橋液体の静的平衡方程式は次のとおりです。

Pd Ly (x3 (0)-x4 (0)+Lx )+Wz -[T(x3 (0)-x4 (0)+Lx )(sinθ2 (0)+sinθ1 (0))+TLy (sinθ3 (0)+sinθ4 (0))]-ρgV0 =0

はんだ接合部の底部の圧力強度 (Pd ) は:Pd =[T(x3 (0)-x4 (0)+Lx )(sinθ2 (0)+sinθ1 (0))+TLy (sinθ3 (0)+sinθ4 (0))+ρgV0 -Wz ]/[Ly (x3 (0)-x4 (0)+Lx )]

これらの式では、ρ ははんだスズの液体密度を表します。 T は、はんだ接合液の表面張力を指します。 x3 (0) と x4 (0) 下部はんだパッド液体での液体はんだ接合部の両端の滑りを参照してください。 θ1 (0) と θ2 (0) θ3 の間、はんだ接合部の両側と底面パッド表面の液体-気体界面によって形成される両側の接触角を指します。 (0) と θ4 (0) 両側の液体-気体界面によって形成される両端の接触角を指します。 V0 はんだ接合部の体積を指します。 Wz 垂直方向のチップとはんだ接合部の端にあるパッドに加えられる力を指します。

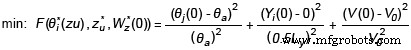

式(1)および(2)の極限の下で、はんだ接合部のフレーム曲線は、はんだ接合部の上端の境界条件を、初期値の有効な解法に基づいて初期条件と同等にすることができます。初期値の解は、z が 0 に等しいという要件を満たすことができないため、式 (3) に表示される目的関数の最小化に関して同等の問題に変換されます。

この最小化された目的関数を適用して、パッド Dx4 の理想的な設計サイズを決定できます。 .

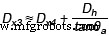

さらに、PCB パッドの錫ラップ角度の幾何学的特徴を考慮する必要があります。その観点から、パッドの拡張サイズは、以下の約式に従う必要があります。

この式では、Dh は、チップの外側に露出した側面パッドの厚さを指します。陰変数の最適化により、目的関数と内側と外側のパッドの設計サイズ (Dx4 &Dx3 ) は、下端の側の値の必要性を満たして計算できます。

この方法により、QFN に適したパッドを適切に設計して、このコンポーネントと PCB の両方の高い電気的性能を実現できます。次に、専門的で資格のあるアセンブリ機能により、PCBCart は理想的な設計を現実のものに変えることができます。

役立つリソース

• Via-in-pad (VIP) 技術の紹介

• SMT PCB の設計要件パート 1:通常のコンポーネントのボンディング パッド設計

• SMT PCB の設計要件パート 2:パッドトレース接続、スルーホール、テストポイント、はんだマスク、シルクスクリーンの設定

• PCBA の最適なパフォーマンスのための QFN コンポーネントのステンシル設計要件

• PCBCart のフル機能 PCB 製造サービス - 複数の価値 -追加オプション

• PCBCart の高度な PCB アセンブリ サービス - 1 個から開始

産業技術