コンプライアンスフリーのZrO2 / ZrO2 − x / ZrO2抵抗変化型メモリと制御可能な界面マルチステートスイッチング動作

要約

界面からフィラメント状のスイッチングモードへの制御可能な変換は、ZrO 2 に表示されます。 / ZrO 2 − x / ZrO 2 三層抵抗変化型メモリ。 2つのスイッチングモードは、提案された可能なスイッチングおよび変換メカニズムを使用して調査されます。 ZrO 2 − x の抵抗率変調 層は、酸素イオンの注入/収縮による界面スイッチングモードでのスイッチングを担当することが提案されています。 ZrO 2 で形成されたフィラメントによる固有の直列抵抗により、スイッチングはコンプライアンスフリーです。 レイヤー。 RESET を調整する 電圧、制御可能で安定したマルチステートメモリを実現できます。これは、次世代のマルチステート高性能メモリを開発する能力を明確に示しています。

背景

より高密度で、より速く、よりエネルギー消費の少ない不揮発性メモリの開発は、現代の情報技術の革新にとって非常に重要です[1、2]。多くの候補が次世代のメモリデバイスであることが明らかになっていますが、金属酸化物をベースにした抵抗変化型メモリ(RRAM)は、高速、高スケーラビリティ、低消費電力、およびCMOSプロセス[3]。抵抗変化型メモリの詳細なスイッチングメカニズムは不明なままですが、印加された電界下での酸素空孔の移動がスイッチング動作において重要な役割を果たすことは広く受け入れられています[4]。スイッチングメカニズムに応じて、抵抗スイッチングはフィラメントモードと界面(均質)モードに分類できます。フィラメントモードは、2つの電極間の酸素空孔フィラメントの形成と破壊によって実現されます。一方、界面モードでの抵抗スイッチングは、界面に沿った酸素空孔の分布によって制御されます。電流は、フィラメントモードでは導電性フィラメントに局在し、界面モードではデバイス領域全体に均一に分布します[5、6]。メモリデバイスに特徴的な抵抗スイッチングモードは、その構造に強く依存します。一般に、金属酸化物ベースのシステムでの界面モードの表示は、垂直軸に沿った酸素勾配プロファイルの存在に依存しています[7、8]。最近、1つの材料システムにおける両方のモードの共存も報告されています[9、10、11]。測定パラメータを変調することにより、これら2つのモード間の変換も実現できます[12]。ただし、界面モードでのスイッチングは通常、電極/機能層の界面での欠陥状態を介したキャリアの蓄積および枯渇プロセスによって引き起こされるショットキー障壁の高さの変化に起因します[7、9、10、11、12、13、 14,15,16,17,18]酸化物/酸化物界面での酸素空孔移動の影響ではなく。

過去数年間で、RRAMのストレージ密度を高めるために大きな進歩が見られました。メモリセルの物理的寸法を縮小する取り組みとは別に、高抵抗状態(HRS)と低抵抗状態(LRS)の間の中間抵抗状態(IRS)を利用して、1つのメモリセル内でマルチステートストレージを実現するようになりました。人気のある代替ソリューション[19、20]。このマルチステートストレージの動作は、高密度ストレージおよび酸化物ベースの電子シナプスデバイスにとって重要です[21、22、23]。フィラメントスイッチングモードでのマルチステートストレージは、異なる RESET で導電性フィラメントの幅や数を制御することで実現されます。 電圧または SET 現在のコンプライアンス。 TiO x を含むさまざまな金属酸化物 、ZnO、SiO x およびHfO 2 、RRAMデバイスでのマルチステート動作を示しています[24、25、26、27]。界面スイッチングモードでの多状態ストレージも報告されており、酸素欠陥領域の幅の調整がこの動作の原因であると提案されています[12、28]。ただし、どちらのスイッチングモードでも、 SET で電流に準拠する必要があります デバイスを故障から保護し、フィラメントスイッチングの場合は、何倍も低い抵抗状態を実現するプロセス。これらの要件により、RRAM回路設計が複雑になる可能性があります。したがって、制御可能なマルチステートスイッチング動作を備えたコンプライアンスフリーの抵抗変化型メモリは、スイッチング中の電流オーバーシュートを最小限に抑え、製造コストを大幅に削減できる可能性があるため、有利である可能性があります[29、30]。

最近、ZrO 2 の使用法 アクティブスイッチング層は、その高い熱力学的安定性、単純な組成、および半導体プロセスの互換性のために注目を集めています[31、32、33]。さらに、ZrO 2 内にエイリアンレイヤーを挿入します 酸化物ヘテロ構造を生成するフィルムは、ZrO 2 のスイッチング特性を改善するための効果的な方法であることが証明されています。 ベースのデバイス[34、35]。この作業では、ZrO 2 のデモを行います。 / ZrO 2 − x / ZrO 2 非化学量論的ZrO 2 − x であるベースの抵抗変化型メモリ 層はZrO 2 内に形成されます Zr層を挿入することにより層。界面モードとフィラメントモードの両方が観察され、界面からフィラメントへの制御可能な変換を実現できます。両方のモードのスイッチング特性と性能を調査します。酸化物/電極界面はフィラメントモードでのスイッチング挙動に影響を及ぼしますが、界面モードでのスイッチングは、3層構造の酸化物/酸化物界面に強く依存していました。最も重要なことは、インターフェースモードでの抵抗スイッチングは、コンプライアンスのない組み込みの特性と、さまざまな RESET でのマルチステートストレージの動作を享受することです。 電圧。

メソッド

ZrO 2 薄膜は、室温で中周波プラズマ支援マグネトロンスパッタリング(Leybold Optics HELIOS Pro XL)によって調製されました。このプロセスでは、均一な堆積を確実にするために、基板は180rpmの速度で回転していました。各回転中に、最初に、Ar雰囲気中で2000 Wの電力を使用してZr金属ターゲット(純度99.99%)からZrの薄層が堆積されました。この薄膜は、O 2 の下に基板を通過させることにより、酸化物層に変換されました。 RFソースのプラズマ。 O 2 流量を調整してZrO x を生成できます 異なる組成のフィルム。堆積したフィルムの組成特性は、エネルギー分散型X線(EDX)を使用して調査し、Oxford INCA x-actX線検出器を備えたZeissEVO LS25顕微鏡を使用しました。基板からの影響を最小限に抑えるために、1μmの厚い膜をSiウェーハ上に直接堆積させました。 X線回折(XRD)パターンは、かすめ入射(θ)で収集されました。 =1°)9kWのCu–K αを備えたRigakuSmartlab回折計を使用 ソース。 X線光電子分光法(XPS)データは、Al–K αを備えたThermoScientificThetaプローブシステムを使用して取得されました。 放射線(光子エネルギー=1486.6eV)。 XPS深度プロファイルは、2×2mmのラスター領域で3kVのビーム電圧でArイオンガンを使用して実行されました。透過型電子顕微鏡(TEM)試料は、従来の機械研磨とそれに続く6keVのAr +を使用した電子透過性へのイオンミリングを使用して準備されました。最後の低エネルギーミリングステップは500eVで実行されました。表面の損傷を最小限に抑えるために、サンプルの構造と形態を、LaB 6 を備えたJEOL2100TEMを使用して分析しました。 ショットキーガンを備えたJEOLARM200F TEM /走査型TEM(STEM)は、どちらも200kVで動作します。環状暗視野(ADF)STEM測定は、プローブと画像収差のCEOS補正装置を使用してARM200Fで実行されました。 ADF-STEM画像は、プローブ電流が約23 pA、収束セミアングルが約25 mrad、内角が45〜50mradのJEOL環状フィールド検出器を使用して取得されました。 Oxford Instruments X-Max N 100TLEウィンドウレスシリコンドリフト検出器(SSD)を使用して、STEM-EDX分析を実行しました。

3層ZrO 2 の抵抗スイッチング動作 / ZrO 2 − x / ZrO 2 フィルムは記憶として調査されました。厚さ200nmのTiN膜が反応的にスパッタされました(N 2 のTiターゲット 雰囲気)SiO 2 に 下部電極を形成する層。これに続いて、2番目のSiO 2 の反応性スパッタリングが行われました。 層(O 2 のSiターゲット 雰囲気)。このSiO 2 の層 フォトリソグラフィーと反応性イオンエッチングによってアクティブデバイス領域を形成するようにパターン化されました。続いて、ZrO 2 / ZrO 2 − x / ZrO 2 (20 nm / 5 nm / 20 nm)3層を堆積して、スイッチング層を形成しました。三層構造は、ZrO 2 の間に酸素プラズマを停止することによって得られました。 成長。 ZrO 2 層はO 2 の下で達成されます ZrO 2 − x での流量20sccm 層は、O 2 をオフにすることによって得られます 20秒間流れます。同一のZrO 2 / ZrO 2 − x / ZrO 2 XRDおよびXPSの特性評価のために、Si基板上に3層も堆積されました。最後に、200 nmのTiN層をスパッタリングし、3層上にパターン化して、上部電極を形成しました。すべての電気的測定は、Keithley4200半導体特性評価システムを使用して実行されました。測定中、下部電極を接地したまま、プログラミング電圧バイアスを上部電極に印加しました。デバイスの上部電極と下部電極へのプローブ/ポイントコンタクトは、ウェントワース研究所のAVT 702半自動プローバーを使用して、ウェントワースプローブ針のペアを介して実現されました。電圧DC掃引測定は、0.5 V / sの一定速度で実施されました。

結果と考察

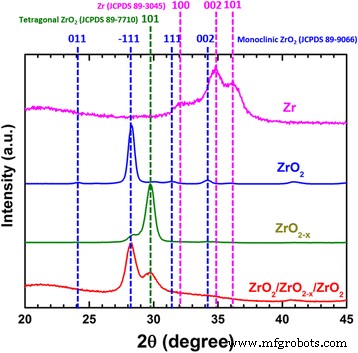

三層構造の特性は、最初にXRDによって調査されました。図1は、28.2°と29.8°に位置する2つのピークを特徴とする堆積したままの3層(赤)のXRDパターンを示しています。これらの2つのピークは、単斜晶系ZrO 2 の-111ピークに割り当てることができます。 正方晶ZrO 2 からの相と101ピーク それぞれ、2つのフェーズの存在を示すフェーズ。単一のZrO x で実行されたEDXおよびXRDの特性評価 異なる組成の層(追加ファイル1:図S1およびS2に示されている)は、化学量論的ZrO 2 単斜晶相(青)を表示し、正方晶相(緑)は酸素欠乏ZrO 2 − x から検出されました。 層。金属Zr(ピンク)のXRDピークは3層XRDパターンでは観察されませんでした。これは、両方の化学量論的ZrO 2 の共存を示唆しています。 および酸素欠乏ZrO 2 − x 三層構造の層と埋め込まれたZr層が酸化されています。

堆積したままのZrO 2 のXRDパターン / ZrO 2 − x / ZrO 2 三層構造(赤 )、酸素欠乏ZrO 2- x レイヤー(緑 )、化学量論的ZrO 2 レイヤー(青 )および純金属Zr層(ピンク )

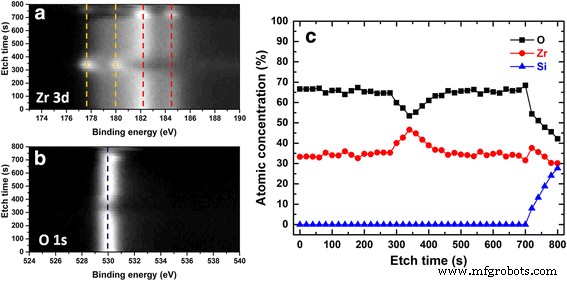

図2a、bは、800秒のエッチング時間にわたるZr3dおよびO1sピークプロファイルのXPS結果を示しています。約に位置する2つのピーク。 182.3および184.5eVは、完全に酸化されたZr 4+ に起因する可能性があります。 状態[36、37]、これは約のエッチング時間までZrスペクトルを支配します。 300秒約に位置する2つのピークの明確に強化された強度。その後、178.3および180.5 eVは、300〜400秒のエッチング時間の間に観察できます。これには、O 2- の減少も伴います。 約でのピーク強度。 530.0eV。これらの2つのZr3dピークは、金属または非酸化Zr 0 に関連していることが示唆されています。 状態[36]。これは、酸素不足のZrO 2 − x を示しています。 層はこの3層構造の真ん中にあります。 400秒のエッチング時間の後、Zr 4+ ピークはその優位性とO 2- の強度を再開します ピークは正常に戻ります。図2cの深さプロファイルに沿った原子濃度は、埋め込まれたZr層の非化学量論的ZrO 2 − x への酸化をさらに確認します。 。 ZrO 2 間の組成勾配についても言及する価値があります。 およびZrO 2 − x 界面スイッチング挙動の形成を促進することが示唆される界面も観察された[8]。 XRDとXPSの両方の結果を考慮すると、XRDで検出された単斜晶相は2つの化学量論的ZrO 2 に由来すると考えるのが妥当です。 レイヤー。挟まれた酸素欠乏ZrO 2 − x 一方、層は正方晶相に寄与しますが、アモルファス領域の痕跡を除外することはできません。

a のXPSスペクトル Zr3dおよび b ZrO 2 のO1 / ZrO 2 − x / ZrO 2 700秒のエッチング時間にわたる三層構造。 c ZrO 2 のXPS深度プロファイル / ZrO 2 − x / ZrO 2 三層構造

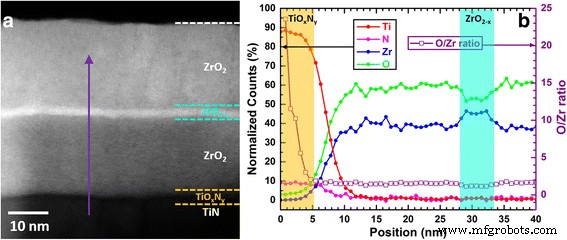

TEM測定により、酸素不足のZrO 2 − x の3層構造がさらに確認されます。 図3aに示すように明確に観察された層。さらに、ZrO 2 間の別の界面層 層と下部のTiN電極も見えます。対応するEDXプロファイルを図3bに示します。ここでは、Ti、O、N、およびZr原子の相互拡散が最初の10nmで明らかです。さらに、最初の5 nmのはるかに高いO:Zr比(白四角)は、TiO x の存在を確認します。 N y ZrO 2 間の界面層 とTiN下部電極。確かに、ZrO 2 として TiN、O 2 の直後にスパッタされます プラズマはTiN表面と反応して、TiO x を形成します。 N y ZrO 2 の場合のレイヤー 層はまだ非常に薄いです。界面TiOの同様の形成 x N y レイヤーも報告されました[38、39]。

a サンプルと b の断面のADF-STEM画像 TiN / ZrO 2 のSTEM-EDX元素線プロファイル / ZrO 2 − x / ZrO 2 構造

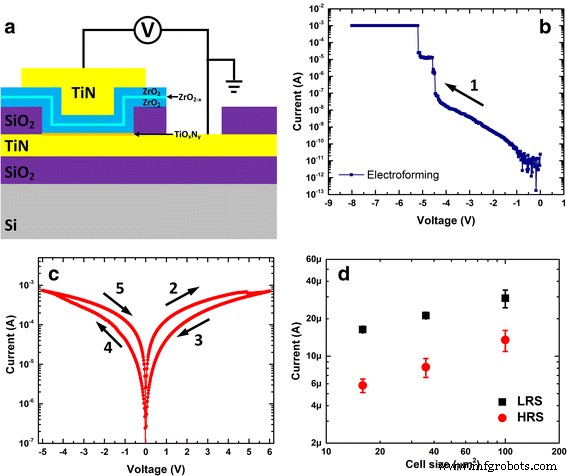

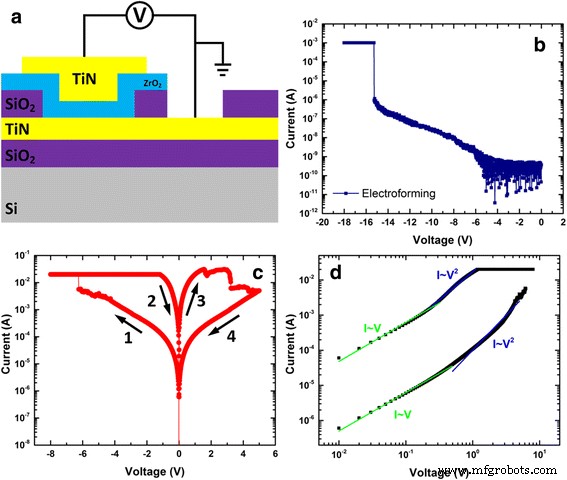

特性評価の結果に基づいて、ZrO 2 の概略図 / ZrO 2 − x / ZrO 2 3層メモリを図4aに示します。図4bに示すように、元のデバイスは高抵抗状態にあると測定されます。大きな負の形成電圧( I CC =1 mA)は、軟質絶縁破壊を誘発し、スイッチングを開始するために必要です。非常に珍しいことに、これは2段階の成形プロセスに関連しており、2つのZrO 2 で2つのフィラメントが連続して形成されることを示唆しています。 レイヤーとデバイスは SET 低抵抗状態になります。次に、正の電圧を RESET に印加しました。 図4cに示すように、デバイスをHRSに挿入します。注目すべきことに、このリセット このプロセスは、電流が徐々に連続的に減少することを特徴としています。これは、界面抵抗スイッチングの典型的な特徴です。 SET 負の電圧バイアスを適用することによるプロセスも同様の動作を示し、界面抵抗スイッチングが支配的なスイッチングモードであることを示唆しています。界面スイッチングの振る舞いは、HRSとLRSの両方における電流の面積依存性によってさらに証明されます(図4dに示されています)。電極のサイズが大きくなると、両方の電流が増加します。これは、電流伝導がフィラメント状ではないことを示しています。電流の増加は、面積に完全に比例しているわけではありませんが。これは、粒界とリーク電流の量が多いため、界面スイッチング中のセルサイズが大きくなると抵抗率の変調が効果的でないことで説明できます[12]。同様の動作は、他の2層界面抵抗スイッチングデバイスでも報告されています[8、12]。 SET プロセスは、自己コンプライアンスの動作を示します。これは、スイッチング中の電流オーバーシュートを最小限に抑え、製造コストを大幅に削減できる可能性があるため、抵抗変化型メモリでのアプリケーションに役立ちます[29、30]。

a 三層TiN / ZrO 2 の概略図 / ZrO 2 − x / ZrO 2 / TiNメモリ。 b I–V TiN / ZrO 2 の電鋳プロセスの特性 / ZrO 2 − x / ZrO 2 / TiNデバイス。 c I–V 成形後の界面スイッチングの特性。 d 界面スイッチングモードの両方のHRS / LRSのデバイスサイズの関数としての電流

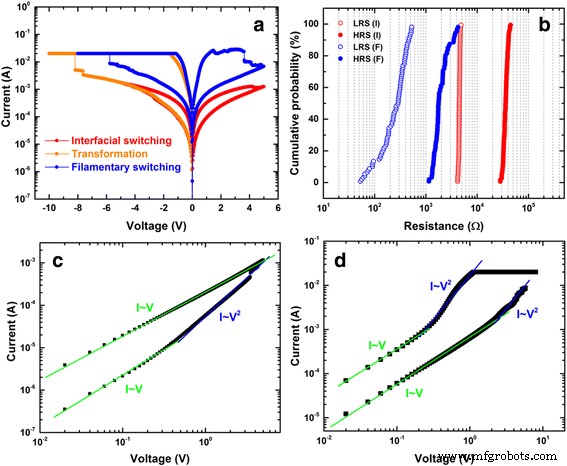

界面スイッチングモードからフィラメントスイッチングモードへの変換は、図5aに示すように、2番目の成形ステップによってトリガーできます。 20 mAの電流コンプライアンスで、HRSのデバイスにさらに負のバイアスが適用されました。これは約で電流の突然の増加につながります。 -8 Vであり、その後、デバイスははるかに低い抵抗状態のままになります。 リセットの後 正のバイアスを使用したプロセスでは、デバイスのスイッチングモードが完全にフィラメント状に変換され、シャープな SET が特徴です。 (電流制御)および RESET トランジション。図5bは、界面スイッチングモードとフィラメントスイッチングモードの両方のLRSとHRSの累積確率分布を示しています。この分布では、これら2つの抵抗状態のセット間で明確な違いが見られ、デバイスが異なるモードでスイッチングされたことを示しています。両方のスイッチングモードの伝導メカニズムに光を当てるために、対数 I–V SET の曲線プロットと線形フィッティング プロセスが提示されます。 I–V 界面モードのHRSでの曲線は、低電圧でのオームの振る舞いに従い、高電圧での2次項、つまり I が追加されます。 ∝ aV + bV 2 、これは、図5cに示すような空間電荷制限電流(SCLC)モデルの典型的な特徴です[40、41、42]。このSCLCメカニズムの同様の観察結果は、他の界面抵抗メモリデバイスでも報告されています[8、12]。一方、対数の I–V SET の曲線 変態後のフィラメントスイッチングのプロセスを図5dに示します。この曲線は、電流がトラップを備えたSCLCモデルによって支配されていることを示しています[40、41、42]。同様の伝導モデルを使用して界面スイッチングとフィラメントスイッチングを説明しますが、2つのモードは、特に低抵抗状態で、依然として明確な特徴を示します。フィラメントモードでのLRSの電流伝導は、オーム領域( I )の2つの領域で構成されます。 ∝ V )および子供の法域( I ∝ V 2 )一方、後者は界面スイッチングのLRS伝導では観察されませんでした。これは、フィラメントスイッチングがキャリアトラッピング/デトラッピングプロセスによって媒介されていることを示しています[43]。かなりの量のトラップが2番目の形成プロセス中に導電性パスで生成され、フィラメントモードのLRSで電流の2次項につながると推測されます。

a 私 – V 変換プロセスの特性(オレンジ )界面スイッチングから(赤 )フィラメントスイッチング(青 )。 b 両方の界面( V )のHRSとLRSの累積確率グラフ リセット =6V)およびフィラメントスイッチングモード。 SET プロセス I–V c の曲線 界面および d 両対数プロットのフィラメントスイッチングモード

単層ZrO 2 図6aに示す回路図と比較するために、膜厚40nmのメモリも製造されました。電鋳プロセス( I CC =1mA)のTiN / ZrO 2 / TiNデバイスは、はるかに高い電圧のシングルステップを備えています(図6b)。続いて、双極スイッチング動作が観察されました(図6c)。これは、3層デバイスのフィラメントモードに似ています。ただし、この単層デバイスでは、界面スイッチングモードは観察されませんでした。図6dは、対数の I–V を示しています。 SET の曲線 トラップを使用したSCLCモデルとの良好な一致を示す単層デバイスのプロセス。これは、サンドイッチされたZrO 2 − x という結論も裏付けています。 層は、ZrO 2 − x のいずれかで発生する界面スイッチングにとって重要です。 層またはZrO 2 − x の近く / ZrO 2 インターフェイス。

a 単層TiN / ZrO 2 の概略図 / TiNデバイス。 b I–V TiN / ZrO 2 の電鋳プロセスの特性 / TiNデバイス。 c I–V TiN / ZrO 2 の特性 成形後の/ TiNデバイス。 d I–V SET の曲線 線形フィッティングを使用した両対数プロットでのプロセス

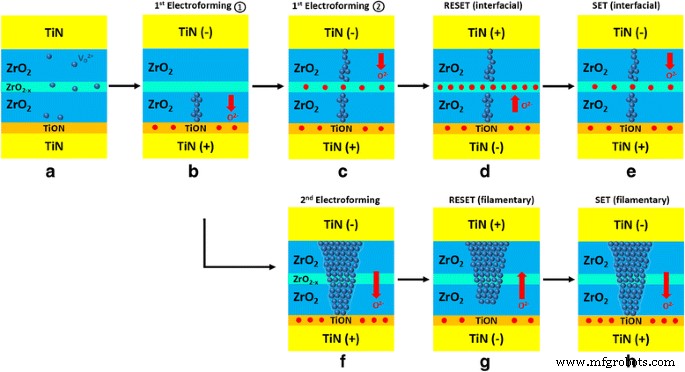

特性評価の結果に基づいて、図7に示すように、スイッチングモードと変換の両方の詳細なメカニズムを提案します。負の形成電圧を印加することにより、酸素イオンが下部電極に向かって押し下げられ、酸素空孔が上部に向かって移動します。電極と導電性フィラメントを形成します。界面TiO x N y 層は酸素貯蔵庫として機能するため、双極性の振る舞いにおいて重要な役割を果たします[38、44]。 2つの弱いフィラメントが下部と上部のZrO 2 内で連続して生成されます 2段階の成形プロセスを特徴とする層(図7b、c)。一部の酸素イオンが中央のZrO 2 − x に注入された可能性がありますが 層では、酸素空孔のレベルは、層を低抵抗状態に保つのに十分高いままです。したがって、デバイスはLRSに切り替わります(図7c)。正のバイアスが印加されると、酸素イオンがTiO x から引き付けられます。 N y ZrO 2 − x へのレイヤー 層、酸素に富む層の形成をもたらします。 ZrO 2 − x のこの化学量論的変調 レイヤーはメモリをHRSに変更します(図7d)。 SET には、もう1つの負のバイアスが必要です。 中間層からTiO x に酸素イオンを押し戻すことにより、デバイスをLRSに挿入します。 N y 貯水池(図7e)。デバイスのコンプライアンスフリー特性は、2つのフィラメントの導電率が低いことに由来する可能性があります。これは、固有の直列抵抗として効果的に機能します。変換は、非常に大きなバイアスが適用されたときに発生します。これにより、3層構造全体ではるかに強力で導電性のフィラメントが形成されます(図7f)。デバイスの抵抗は、ZrO 2 − x に依存しなくなりました。 層、およびスイッチングモードは界面からフィラメント状に変換されます。その後、デバイスのスイッチをオンにしてオフすることができます それぞれ正と負のバイアスを使用します(図7g、h)。

3層TiN / ZrO 2 のスイッチングメカニズムの概略図 / ZrO 2 − x / ZrO 2 界面スイッチングモード用の/ TiNデバイス( a – e )。界面モードからフィラメントモードへの変換( f )およびフィラメントモード( g 、 h )

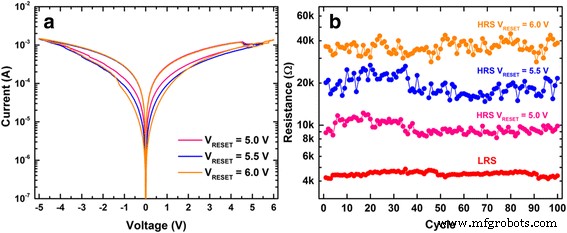

この作業の界面スイッチングモードは、マルチステートストレージの可能性を提供します。界面モードでのデバイス抵抗は、ZrO 2 − x の酸素イオンのレベルによって媒介されるため 層、多重抵抗状態は、異なる RESET を使用して中間層の酸素イオンの量を制御することによって達成できます。 電圧。図8aは、 I–V を示しています。 RESET を使用したデバイスの特性 一定の SET で5.0、5.5、6.0Vの電圧 -5 Vの電圧。酸素空孔の移動は電界によって駆動されるため、これらのパラメータは層の厚さに応じて拡張可能であることに注意してください。約50nmの厚い機能層を備えたこのプレゼンテーションでは、スケールダウンして両方の SET を大幅に削減できる可能性があります。 およびリセット 電圧。図8bは、このマルチステートメモリ動作のサイクル特性を示しています。ここでは、可逆的で再現性のある抵抗スイッチング特性が約1秒間示されています。 100サイクル、このデバイスの有望な耐久性の動作を示します。

a I–V 三層TiN / ZrO 2 の界面スイッチングの特性 / ZrO 2 − x / ZrO 2 RESET が変化する/ TiNデバイス 電圧。 b 異なる RESET を使用した界面スイッチングの100サイクルの耐久性テスト 電圧

結論

ZrO 2 で、界面モードからフィラメント状モードの界面モードへの制御可能な変換が観察されました。 / ZrO 2 − x / ZrO 2 三層メモリ。可能なスイッチングおよび変換メカニズムが提案されます。埋め込まれたZrO 2 − x レイヤーは、インターフェイススイッチングモードの重要なレイヤーであると考えられています。このモードは、おそらくZrO 2 に形成された2本の細いフィラメントによる固有の直列抵抗が原因で、コンプライアンスのない動作を示します。 レイヤー。 RESET を制御する 電圧、HRSでのマルチステート抵抗を実現できます。このマルチステートストレージの動作は、次世代のマルチステート高性能メモリを開発する機能を明確に示しています。

略語

- ADF-STEM:

-

環状暗視野走査透過電子顕微鏡法

- EDX:

-

エネルギー分散型X線分光法

- HRS:

-

高抵抗状態

- IRS:

-

中抵抗状態

- LRS:

-

低抵抗状態

- RRAM:

-

抵抗変化型メモリ

- SCLC:

-

空間電荷制限電流

- XPS:

-

X線光電子分光法

- XRD:

-

X線回折

ナノマテリアル

- 純粋なCMOSロジックプロセスによる自己抑制抵抗スイッチング負荷を備えたRRAM統合4TSRAM

- 抵抗変化型メモリのモデリングとシミュレーションに関する集合的研究

- ハイブリッド全誘電体-グラフェンメタ表面に基づく制御可能な複屈折を備えた偏光変換器

- BaTiO3 / Nb:SrTiO3エピタキシャルヘテロ接合における強誘電場効果による非対称抵抗スイッチング効果

- 確率的空孔モデルによる接触抵抗変化型メモリの変動性の研究

- 構造用カラーマイクロファイバーを使用した光スイッチングパターンの製造

- セレクタおよびメモリとしてのV / SiOx / AlOy / p ++ Siデバイスの二重機能

- 二硫化モリブデンとZrO2ヘテロ接合のエネルギーバンドの調査

- マイクロ波アニーリングによる原子層堆積Al2O3 / ZrO2 / Al2O3MIMコンデンサの誘電増強

- ZrO2誘電体を備えた高移動度GepMOSFET:ポストアニーリングの影響

- HfO2 / TiOx二層抵抗変化型メモリの低電力抵抗変化特性