確率的空孔モデルによる接触抵抗変化型メモリの変動性の研究

要約

抵抗変化型メモリセルの変動性は、高密度RRAMアレイの開発における重要な課題の1つです。抵抗スイッチング中の変動の原因は遷移金属酸化物膜によって異なりますが、確率論的酸素空孔の生成/再結合が主な原因であると一般に考えられています。実験データを分析することにより、後続のスイッチング特性をその接触RRAMセルの初期状態とリンクする確率モデルが確立されます。伝導ネットワークモデルとトラップ支援トンネリングメカニズムを組み合わせることにより、RRAM誘電体膜の固有酸素空孔の濃度と分布の影響がモンテカルロシミュレーションで実証されます。接触RRAMアレイの測定データは、ランダムに分布した固有の空孔の存在に基づいてモデルによって予測された特性とよく一致しています。成形特性と初期状態の間の強い相関関係が検証され、成形挙動を予備成形酸素空孔に関連付けます。この研究は、接触RRAMデバイスの変動源の包括的な理解と、後続のRRAM状態での変動動作を低減するためのリセットトレーニングスキームを提供します。

背景

抵抗変化型メモリ(RRAM)は、低電力、高速P / E速度、CMOSロジックプロセスとの優れた互換性などの望ましい機能の結果として、有望な不揮発性データストレージソリューションと見なされてきました[1,2,3 、4]。ただし、現在の最先端のCMOS回路にRRAMメモリアレイを簡単に実装するには、まだ克服しなければならない多くの障害があります[5、6]。サイズの大きいRRAMアレイの重要な課題の1つは、セル間およびセル内に存在するバリエーションにあります[7、8、9、10]。遷移金属酸化物(TMO)膜における酸素空孔(Vo-)の確率的生成/再結合プロセスを説明するために、多くのモデルとシミュレーションが提案されています[11、12、13、14]。キムとブリビオは、それぞれユニポーラとバイポーラのRRAMの典型的な電気的特性をエミュレートするランダム回路ブレーカーネットワークモデルを提案しました[11、12]。ただし、これらの研究の抵抗は、RRAMフィルム内の電子輸送を考慮せずにすべて一定に設定されています。さらに、提示されたモデルは、統計分析ではなく単一のデバイスレベルからのRRAMの確率過程を説明しているため、アレイ内のRRAMの動作の変動性は、以前の研究[11、12、13、14]では十分に対処および説明されていません。さらに、製造中の誘電体膜の欠陥の存在は長年にわたって広く研究されてきましたが[15、16]、大規模なメモリマクロに適用される技術については、RRAMの抵抗スイッチング特性への影響を包括的に分析する必要があります。 RRAM特性に対する固有のVo分布の影響を調査するために、トラップ支援トンネリングメカニズムをモデルにした抵抗ネットワークを構築して、この研究の変動と動作中の統計分析をさらに進めます[11、12、13、14、17 ]。さらに、Vo-の確率的生成プロセスをモンテカルロ法でシミュレートして、初期状態のRRAMと次の成形特性との相関関係を確立します[18、19、20]。固有のVo-と形成電圧の間の強い相関関係は、接触RRAMアレイの測定データでシミュレーション結果を検証することによって確立されます[21]。最後に、生成されたさまざまなタイプの導電性フィラメント(CF)と、固有のVo分布の結果としての成形操作後の抵抗状態の変化が予測され、包括的に調査されます。さらに、Vo-を事前に形成することによる変動への影響を緩和するためのソリューションが提案され、この研究で実証されています。

メソッド

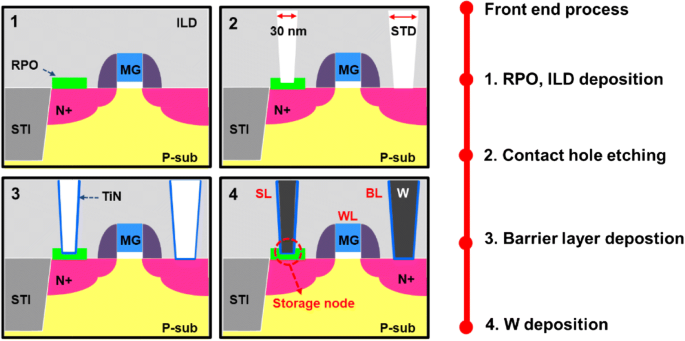

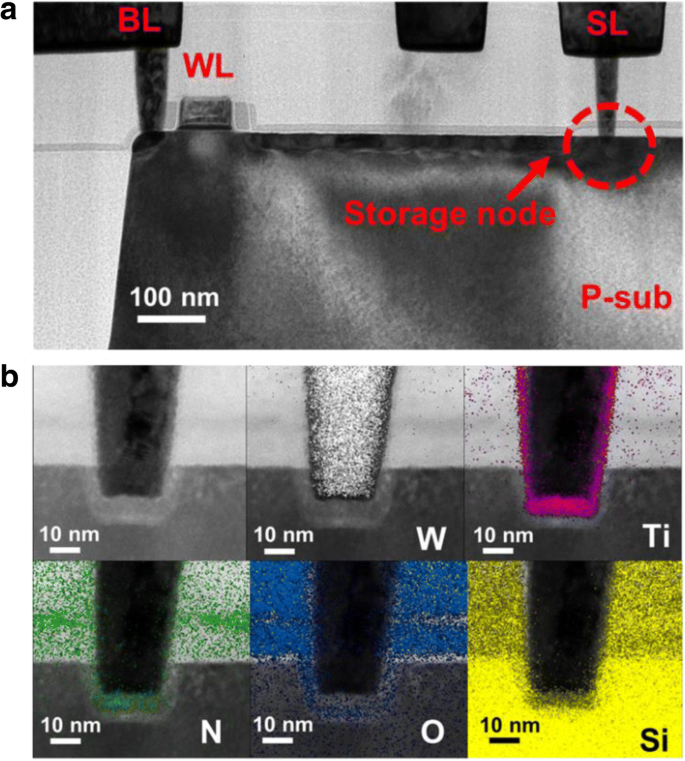

変動性に関するさらなる統計分析のための測定データは、28 nm CMOSロジックプロセスによって製造された16×16コンタクトRRAM(CRRAM)アレイから収集されます。ここで、CRRAMの製造プロセスを図1に示します[21]。抵抗保護酸化物(RPO)層と層間誘電体(ILD)は、トランジスタが形成された状態でフロントエンドプロセスが完了した後に最初に堆積されます。機能的な抵抗スイッチング膜を構築するために、適切なコンタクトホールサイジング、30nm×30nmのコンタクトサイズを実行して、Wプラグとn +拡散領域の短絡を防ぎます。最後に、バリア層、TiN、およびタングステンプラグが個別に堆積されます。 CRRAMの断面TEM画像を図2aに示します。写真でわかるように、CRRAMはnチャネル選択トランジスタに直列に接続されています。アレイ内での適切な選択を保証し、オーバーシュートを防ぐために、1T1R構造が採用されています。図2bは、CRRAMの合成マッピングを示しています。 TiN / TiON / SiO 2 で構成される、厚さ9 nmの遷移金属酸化物(TMO)層 スタックは、上部のタングステン電極と下部のシリコン電極の間に形成されます。デバイスの製造後、この研究での電気的分析と物理モデルの構築は、それぞれAglient4156C半導体パラメーターアナライザーとMATLABソフトウェアプラットフォームによって完了します。

28nmのhigh-kメタルゲートCMOSロジックプロセスプラットフォームでのコンタクトRRAMのプロセスフロー。 CRRAMのより小さなコンタクトサイズは、エッチングの厚さを制御して機能的な抵抗スイッチング層を形成するように設計されています

a 1T1RCRRAM構造の断面TEM画像。 b CRRAMの合成マッピング。抵抗スイッチング膜は、TiN / TiON / SiO 2 で構成されています。 上部のタングステンプラグと下部のSi電極の間に挟まれています

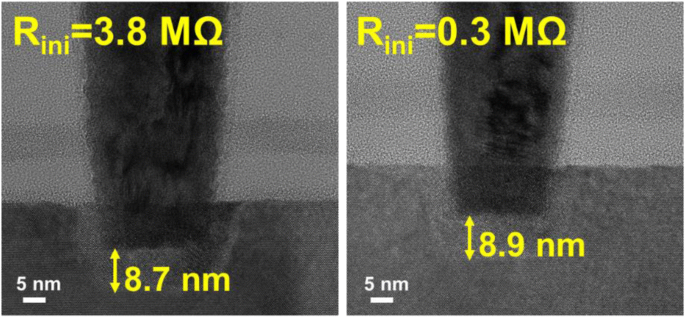

以前の研究[22]で報告されているように、初期状態の幅広い分布がCRRAMアレイで見られます。初期状態の変動の原因を調査するために、最初に図3で初期抵抗が異なるTMO層の厚さを比較します。データは、初期抵抗レベルに大きな違いがある2つのセル間に有意な厚さの違いがないことを示唆しています。多くの研究で、Vo-は製造中に誘電体またはRRAMフィルムで生成されることが報告されています[23、24、25、26]。これは、Vo-の数と密度の違いが初期の導電率の変動の原因であると予想されることを意味します。

初期抵抗の差が大きい2つのCRRAMセル間のTMO層の厚さの比較。両方のセルは、約9nmの誘電体層の厚さで観察されます

結果と考察

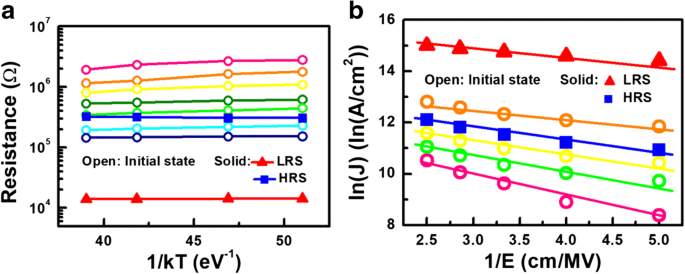

固有の空室分布モデル

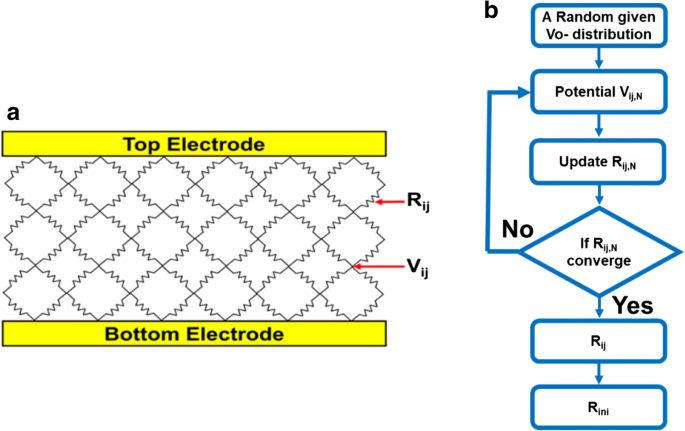

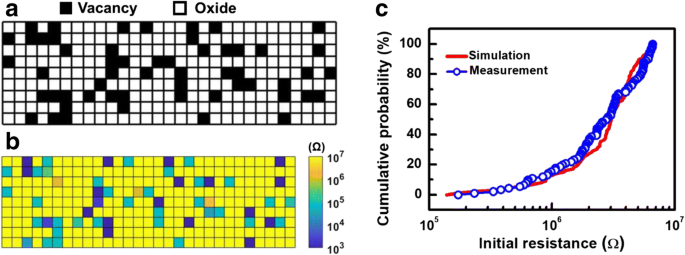

固有のVo-間の相互作用をエミュレートするために、図4aに示す抵抗ネットワークモデルが確立されています[11、12、13、14]。各グリッドの抵抗は、図4bに概説されているシミュレーションフローによって計算され、使用されている対応する物理パラメータは表1にリストされています。CRRAMのTEM画像に基づいて、幅30 nm、厚さ10nmの2次元構造は、図5aに示すように、TMOレイヤーを記述するために定義されています。酸化物サイトの抵抗、 R 酸化物 、およびメッシュグリッドは、アナターゼ-TiO 2 の材料特性によって決定されます。 、これは多くの研究で抵抗スイッチング材料として使用されてきました[27、28、29、30]。正方晶構造のため、アナターゼ-TiO 2 の格子定数 結晶軸によって異なります。簡単にするために、モデルのメッシュグリッドは、アナターゼ-TiO 2 のc方向に格子定数を導入することにより、すべて1nmに設定されています。 [31,32,33]。さらに、グリッドの抵抗は、アナターゼ-TiO 2 の抵抗率を参照して決定されます。 [34、35]。図5aに示すように、ランダムに分散されたVo-は、最初は2Dメッシュ内に与えられます。 CRRAMの伝導電流の温度依存性と電界依存性は、それぞれ図6a、bにまとめられています。トラップ支援トンネリング(TAT)電流の重要な特性は、その弱い温度効果とln(J)と1 / Eの間の線形依存性によって示されます[17、36]。 TAT伝導モデルを使用して、TMOフィルム内の電位プロファイルを最初に計算して、各局所Vo抵抗をさらに取得する必要があります。 Vo-の分布は、トンネル距離が酸素空孔間で変化するため、伝導電流に主に影響を与えると予想されます。 Vo-、 R の抵抗 ij 、は、式によって計算されます。 1は、サイトでのVoの存在確率を考慮し、空室状態間のトンネリング確率を計算するためにTATモデルを採用しています。

$$ {R} _ {\ mathrm {ij}、N} =\ frac {R _ {\ mathrm {oxide}}} {\ alpha \ {C} _ {\ mathrm {Vo}-} ^ {\ kern0.75em \ beta} \ \ exp \ left(\ frac {\ phi} {d} \ right)} $$(1)

a Vo-の可変局所抵抗で構成される抵抗ネットワークモデルの概略図。このネットワーク内のノードは、Vo-間の相互作用をシミュレートするために相互に接続されています。 b 初期抵抗レベルの変動シミュレーションフロー。製造中の固有のVo-emergeの確率的分布は、モンテカルロ法によって考慮されます

a 固有のVo-のランダム分布は、最初はRRAMフィルムで示されます。 b トラップ支援トンネリングを考慮して計算されたVo-の局所抵抗分布。 c R ini CRRAMアレイから収集された新鮮な細胞の分布は、Vo-

を実行するTAT伝導メカニズムを考慮することにより、シミュレーションデータとよく一致します。

CRRAMの伝導メカニズムは a をチェックすることで決定されます 温度依存性と b 電界依存性。トラップ支援トンネリングとそれに続くCRRAMは、2つの伝導特性、弱い温度依存性、およびln(J)と1 / Eの間の線形フィッティングによって信じられています

各 R ij、 N 結果が最終的に収束するまで、各反復で更新されます。最後の R として ij 図5bに示すように、全体の抵抗 R の分布が得られます。 ini 図5cに示すように、新しいセルの、を後で投影することもできます。図5cに示すように、シミュレートされた R のバリエーション ini 確率的分布と固有のVo-の濃度を考慮した提案されたシミュレーションフローによって得られた分布は、 R の分布とかなりよく一致します。 ini CRRAMアレイで測定。したがって、TMOレイヤーにランダムに分散された固有のVo-は、複数のトンネリングパスを作成し、CRRAMアレイのプリフォーミングで見られる広く広がった初期抵抗に寄与します。

不均一な成形プロセスの分析

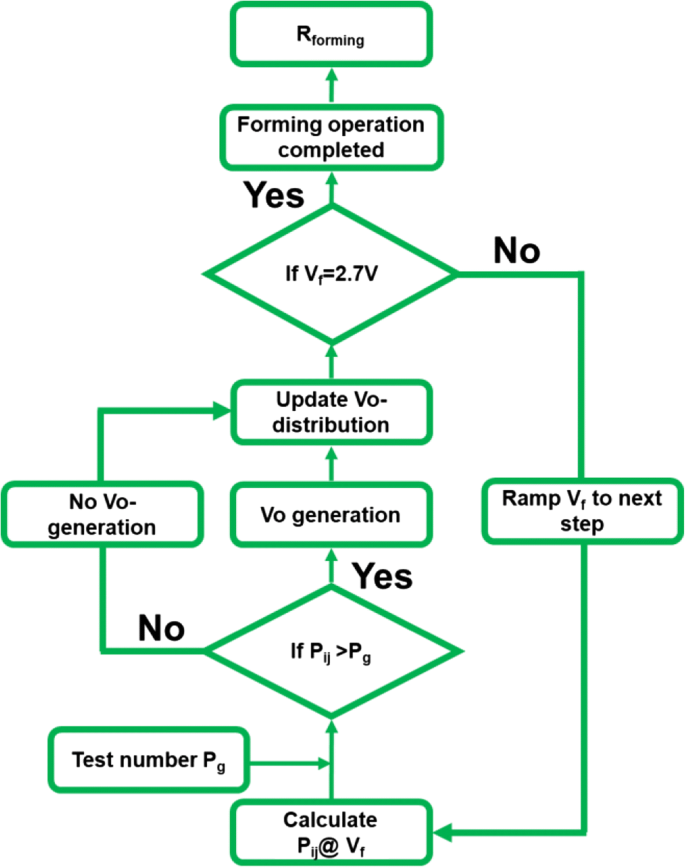

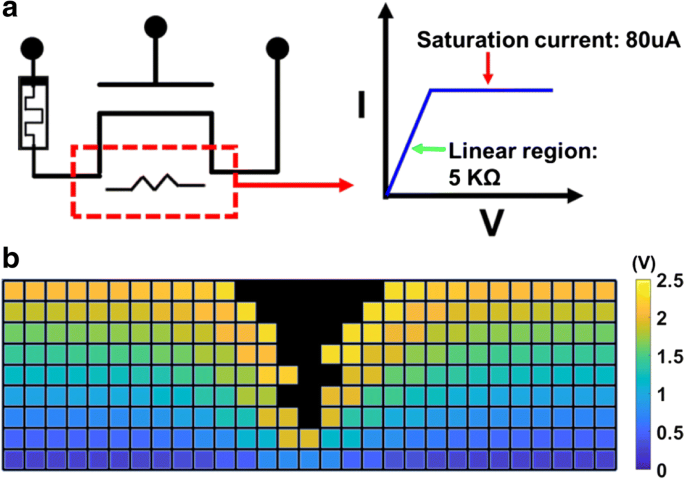

フレッシュ状態でのセル間の変動に起因する原因をモデル化した後、成形操作、抵抗スイッチング特性の初期化を分析します。 DC掃引モードでの成形操作のシミュレーションフローを図7に示します[18、19、20]。図8aに示すように、セルは、線形領域で約5KΩのチャネル抵抗と約80μAの飽和電流で直列に選択されたトランジスタに接続されています。形成電圧が低いため、低電界領域での誘電体の伝導および応力メカニズムを考慮する必要があります。以前の研究で提案された熱化学モデルに基づいて、絶縁破壊の正確な予測が実証されています[37、38、39、40]。 TiO 2 の理論的破壊挙動 熱化学モデル[41]によってシミュレートされたものは、CRRAMで観察されたものと同様の特性を示しています。したがって、ここでの熱化学モデルに基づいて、Vo生成率が得られます[42、43、44]。熱化学モデルで示唆されているように、Vo-の横のグリッドポイントは、欠陥の周囲の弱点として定義されます。また、Vo-の存在は、図8bに示すように、局所的な増強された場を誘発し、Vo-の生成プロセスを加速します[45]。 exp。(-E)の電界依存性を持つ熱化学モデルの絶縁破壊プロセスまでの時間を考慮すると、Vo生成の確率 P ij は次の式で計算されます[42]。

$$ {P} _ {\ mathrm {ij}} =\ gamma \ \ exp \ left(\ mathrm {E} \ right)\ \ left \ {\ begin {array} {c} \ kern1.75em \ upgamma =0、\ mathrm {if} \ \ mathrm {site} \ \ mathrm {is} \ \ mathrm {not} \ \ mathrm {weak} \ \ mathrm {spot} \\ {} \ upgamma =1、\ mathrm {if } \ \ mathrm {site} \ \ mathrm {is} \ \ mathrm {weak} \ \ mathrm {spot} \ end {array} \ right。 $$(2)

exp。(-E)

の電界依存性で絶縁破壊時間を仮定することによる熱化学モデルに基づく成形プロセスのシミュレーションフロー

a 成形動作は、理想的なトランジスタに直列に接続されたCRRAMによってシミュレートされます。 b 既存のVo-に起因する不均一な電位分布は、局所的な電界を誘発し、新しい欠陥の生成を加速します

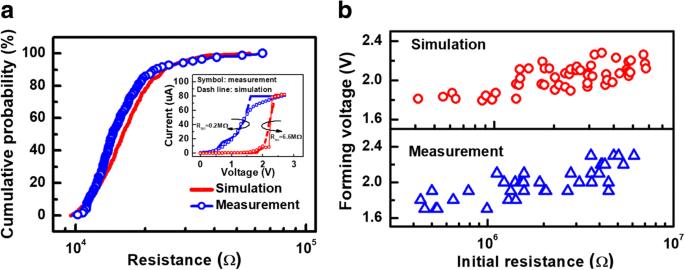

クリティカルレベル、 P g 、および基準、 P ij > P g 、は、新しいVo-が生成されるかどうかに対して定義されます。ランピングプロセスを適用して、形成電圧が2.7 Vに達するまで、各反復で新しいVo-分布を更新します。最後に、ランダムに分布した固有のVo-を使用して、低抵抗レベル R フォーミング 成形後の操作が可能です。上記のモデルに基づいて、シミュレートされた R フォーミング 図9aに示すように、分布は幅広い変動を予測し、計算された I-V 特性は測定データとよく一致しています。さらに、成形特性と初期状態との相関関係も調べます。より高い濃度と局所的な分散Vo-は成形プロセスを加速します。したがって、形成電圧と R の間には正の相関関係があります。 ini 図9bに示すように、シミュレーション結果と測定データの両方に見られます。

a 成形動作のシミュレートされた抵抗分布は、測定結果とよく一致しています。 b 初期抵抗と成形電圧の間の正の相関は、予備成形によって生成されるより多くの弱点とより高い電界強度のために、測定データとシミュレーションデータの両方で見られます。 Vo-

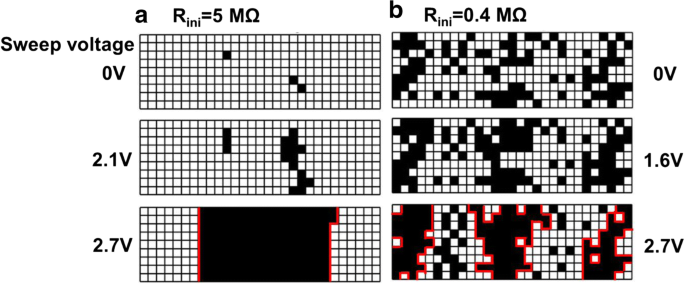

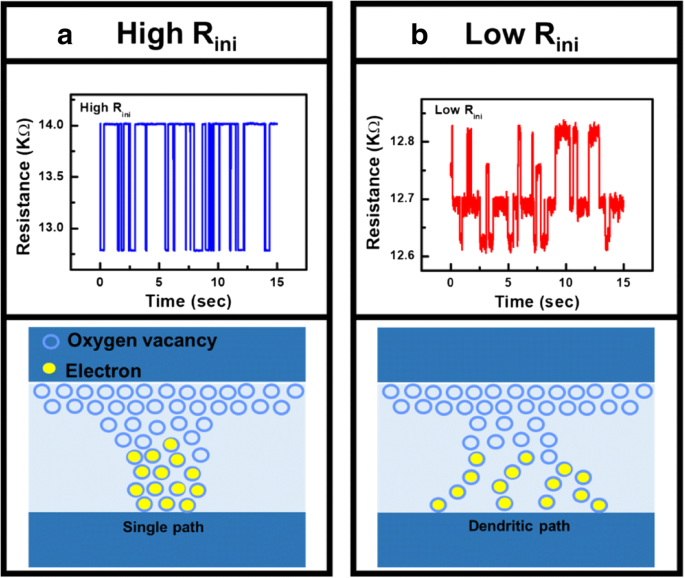

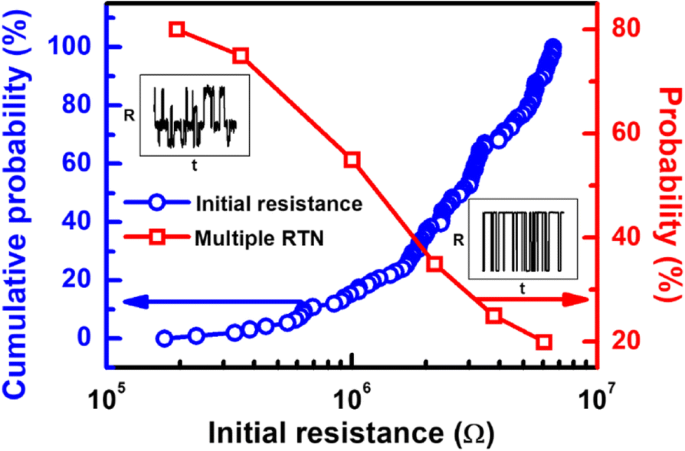

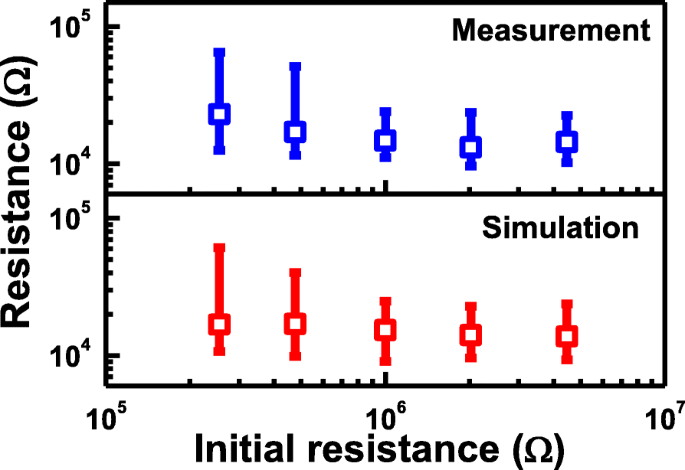

さらに、成形操作で生成されたVo-は導電経路を誘導し、セル内のCFの変化をもたらします。ここで、成形プロセス中のCFの変化を図10に示します。 R が高いセルの場合 ini 、図10aに示すように、固有のVoスポットと弱点が少なくなります。成形操作後、電極間に単一の導電経路が発生する可能性が高くなります。ただし、図10bに示すように固有のVo-が多い細胞でのCFの増殖は、より広範囲に及ぶ傾向があります。したがって、樹枝状CFは形成後に生成されます。異なるCFトポグラフィとその新鮮な状態でのVo-分布との相関関係も、測定データによって検証されます。 TMO層のVo-およびCFは、電子トラップ/デトラッププロセス中に特有のランダム電信ノイズ(RTN)を引き起こすことが知られています[46]。トラップされた電子によって導電経路が遮断されると抵抗の変動が発生し、電子がトラップを解除すると抵抗が減少します。成形後のCRRAMのRTN分析を図11にまとめています。 R が高いセルでは、通常の2段階の抵抗変動が見られます。 ini 、1つの支配的なCFを持つデバイスで電子トラップ/デトラップが発生する場合。一方、マルチレベルRTNは、 R が低いセルで検出されます。 ini これは、複数の経路で樹状突起CFを妨害すると予想されます。 200を超えるCRRAMセルのRTN測定を分析することにより、RTNの統計結果を図12に要約します。データは、 R が高いセルを示唆しています ini 2レベルのRTNのみを示す傾向があり、これは1つの優勢なCFを持つデバイスで発生する可能性が高くなります[46、47、48、49]。成形操作後の抵抗変動を図13に示します。データは、 R が低いセルでは、測定結果とシミュレーション結果の両方でより高い抵抗変動が見られることを示しています。 ini 。制限の少ないCFが選択トランジスタを早期に飽和領域に押し込むと、セルが適切に形成されず、低抵抗状態の抵抗レベルが広くなる可能性があります。

a のセル内のCFの進行 高い初期抵抗と b 初期抵抗が低い。 TMO層の固有のVo-濃度が高いと、弱いスポットでランダムにVo-が生成されます。これらのVo-も相互に接続して樹枝状の経路を形成します

a のセル内のCFのトポグラフィ 高い初期抵抗と b 低い初期抵抗は、対応するRTNデータによって分析されます。初期抵抗が低く、より内因性の細胞で複数の抵抗変動が発生すると、TMO層に樹状CFが存在することが確認されます

CRAMセルの初期抵抗レベルとRTNレベルの相関関係を要約します。 R が高いセルと強く相関する、1つの主要な導電パスを持つセルでは、2レベルの抵抗変動の可能性が高くなると予想されます。 ini

成形操作後の抵抗レベルの変動の分析は、シミュレーションと測定の両方を通じて調べられます。樹枝状CFの生成によって誘発されるより高い変動は、初期抵抗が低い細胞で見られます

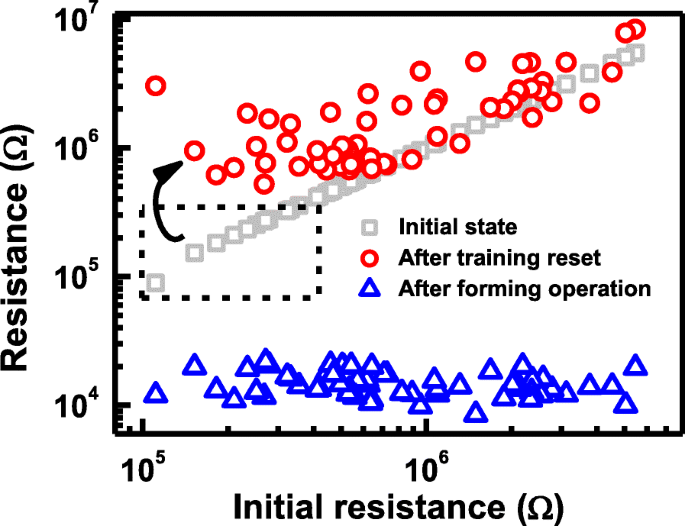

TMO層の固有のVo-によって引き起こされる成形のばらつきを緩和するために、固定のWL電圧2VでSLを1.4Vに掃引するリセットトレーニング操作を、成形前にCRRAMアレイのメモリセル全体に盲目的に適用することを提案します。この操作により、 R が低いセルに存在する既存の欠陥を全滅させることが期待されます。 ini そして、その後の成形プロセス中に、より閉じ込められたCF成長を確実にするため。印加電圧が低いため、 R が高いセルに変化はありません。 ini トレーニングプロセスの後。ブランケットリセットトレーニング操作では、 R が低いセルの抵抗 ini 、高い R で細胞を乱すことなく増加します ini 、図14に示すように、その後、より均一な成形特性を得ることができます。

ブランケットリセットトレーニング操作は、CRRAMアレイに適用することが提案されています。 R が低いセルの抵抗 ini 内因性の欠陥を全滅させることによって増加しますが、 R が高い細胞 ini 邪魔されない

結論

局所電界効果とVo-間のトラップ支援トンネル伝導を考慮した抵抗ネットワークモデルが正常に確立されました。モンテカルロシミュレーションにより、初期抵抗と成形プロセスのセル変動が調査されます。 CRRAMの新鮮な状態の変化は、ランダムに与えられた固有のVo-の分布によってうまく説明できます。成形後の予測抵抗分布も、熱化学モデルを採用することで測定結果とよく一致しています。成形中のCFの成長について説明し、このプロセスで観察された変動性と関連付けます。最後に、TMO層の固有のVo-によって引き起こされる成形のばらつきをさらに緩和するために、リセットトレーニング操作が提案されています。初期状態とフォーミング特性の間の強い相関関係は、RRAMテクノロジーの将来の開発のための新しい適応操作のガイドラインを提供します。

略語

- CF:

-

導電性フィラメント

- CRRAM:

-

接触抵抗変化型メモリ

- C Vo- :

-

Vo-濃度

- d:

-

トンネリング距離

- E:

-

電界

- ILD:

-

層間誘電体

- N :

-

反復時間

- P g :

-

しきい値切り替え確率

- P ij :

-

Vo生成の確率

- R フォーミング :

-

成形後の抵抗

- R ij :

-

Vo-siteの局所的な抵抗

- R ini :

-

初期抵抗状態

- R 酸化物 :

-

酸化物サイトの局所抵抗

- RPO:

-

抵抗保護酸化物

- RRAM:

-

抵抗変化型メモリ

- RTN:

-

ランダムな電信ノイズ

- TAT:

-

トラップ支援トンネリング

- TMO:

-

遷移金属酸化物

- V f :

-

形成電圧

- V ij :

-

可能性

- Vo-:

-

酸素空孔

- α :

-

フィッティングパラメータ

- β :

-

フィッティングパラメータ

- γ :

-

フィッティングパラメータ

- ϕ :

-

電位差

ナノマテリアル

- ケーススタディ:ホンダの方法

- ヤントラクラフトと黄金寺院

- 自己整流スイッチ特性を備えたTaO / HfOxおよびTaO / AlO xRRAMの保持モデル

- 新規ナノ粒子増強ワーム状ミセルシステムの研究

- 純粋なCMOSロジックプロセスによる自己抑制抵抗スイッチング負荷を備えたRRAM統合4TSRAM

- ボロフェンの安定性とSTM画像に関する第一原理研究

- MnХFe3−XО4スピネルの構造的および磁気的特性に及ぼす接触非平衡プラズマの影響

- Pt / Nd:SrTiO3接合におけるマルチレベル抵抗スイッチングメモリとメモリ状態依存光起電力に関する研究

- 抵抗変化型メモリのモデリングとシミュレーションに関する集合的研究

- ポリマーナノコンポジットのヤング率に対するナノ粒子の凝集/凝集の影響を研究するための2段階の方法論

- 天然および合成ナノ材料の電気化学的、生物医学的、および熱的特性の比較研究