アモルファスSiパッシベーションを備えた高移動度GepMOSFET:表面配向の影響

要約

高度なCMOSおよび薄膜トランジスタアプリケーション向けに、(001)-、(011)-、および(111)-配向表面上に作製されたGepMOSFETのアモルファスSiパッシベーションを報告します。 GeのアモルファスSiパッシベーションは、室温でマグネトロンスパッタリングによって実行されます。 Siの固定厚さ t Si 、(001)指向のGe pMOSFETは、より高いオン状態電流を実現します I オン 効果的な正孔移動度μ eff 他の向きのデバイスと比較して。反転電荷密度 Q inv 3.5×10 12 cm −2 、0.9 nm t のGe(001)トランジスタ Si ピークを示すμ eff 278 cm 2 / V×s、これはSiの普遍的な移動度の2.97倍です。 t の減少に伴い Si 、私 オン 容量性実効厚さの減少によりGeトランジスタの数は増加しますが、ミッドギャップ D の増加により、しきい値以下のスイングとリークフロア特性が低下します。 それ 。

背景

ゲルマニウム(Ge)は、Si [1,2,3,4,5,6]と比較して、正孔移動度が高く、サーマルバジェット処理が低いため、高度なCMOSおよび薄膜トランジスタアプリケーションに対して多大な研究関心を集めています。高いチャネル移動度を実現するには、ゲートスタックを形成する前に、高い界面品質につながる表面パッシベーションプロセスが必要です。 Ge金属酸化膜半導体電界効果トランジスタ(MOSFET)でキャリア移動度の利点を提供するために、いくつかの表面パッシベーション技術が開発されています[1、2、7、8、9、10]。これらの技術の中で、Ge上で不動態化されたシリコン(Si)キャップは、界面状態の効果的な抑制と優れた熱安定性と信頼性の利点により、近年ホットスポットになっています[11]。 Siパッシベーションキャップの形成は、SiH 4 の前駆体を用いた化学蒸着(CVD)を使用して広く研究されてきました。 [1]、Si 2 H 6 [4]、Si 3 H 8 [12]、および電子ビーム蒸着[13]。 CVD法は、物理蒸着(PVD)よりも均一な不動態化層を提供できますが、その不動態化率は、チャネル表面の配向とプロセス温度に強い相関関係があります。 PVD技術は、室温でも不動態化率を向上させることができます。これには、熱収支が低く、コストが低いという利点があり、薄膜トランジスタやバックエンドの3D統合アプリケーションにより適しています。この手紙では、マグネトロンスパッタリングによるアモルファスSiパッシベーションを利用して、(001)-、(011)-、および(111)配向表面上に高移動度GepMOSFETを製造しました。大幅に改善された実効正孔移動度μ eff Siユニバーサルモビリティと比較してGeトランジスタで達成されます。アモルファスSiの表面配向と厚さの影響 t Si μに対するアモルファスSiパッシベーションのブースティング効果に関する研究 eff 研究されています。

メソッド

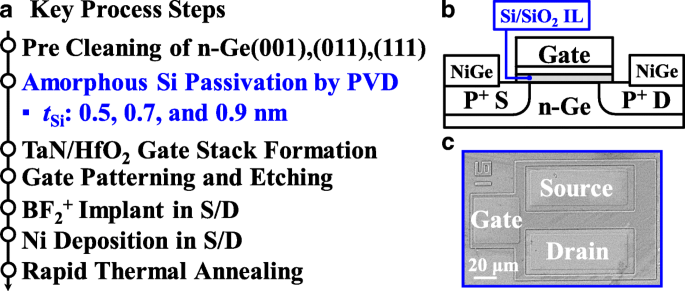

図1aは、(001)-、(011)-、および(111)方向の表面にGepMOSFETを製造するための主要なプロセスステップを示しています。希釈HF(1:50)溶液でゲート前に洗浄した後、50 Wのターゲット電力でマグネトロンスパッタリングによってn-Ge基板上に極薄のアモルファスSiパッシベーション層を堆積しました。60秒、80秒、100の3つのパッシベーション期間sは、0.5、0.7、および0.9 nm t の堆積に対応して使用されました。 si 、 それぞれ。その後、厚さ5nmのHfO 2 ゲート誘電体は、TDMAHfとH 2 を使用した原子層堆積により、250°Cで堆積されました。 それぞれHfとOの前駆体としてのO。 50 nmのTaNゲート電極は、反応性スパッタリングによって堆積されました。次に、ゲート電極をパターン化してエッチングし、続いてBF 2 + 1×10 15 の線量で30KeVでソース/ドレイン(S / D)領域に注入 cm − 2 。 15nmニッケルの非自己整合S / D金属は、リフトオフプロセスによって形成されました。最後に、ドーパントの活性化とS / Dメタライゼーションのために、400°Cでの急速熱アニーリングが実行されました。図1bは、Si / SiO 2 を使用したGepMOSFETの断面図を示しています。 界面層(IL)。図1cは、製造されたGepMOSFETの上面顕微鏡画像を示しています。

a さまざまな t を備えたGepMOSFETを製造するために採用された主要なステップを示すプロセスシーケンス Si 。 b SiO 2 を使用したGepMOSFETの断面図 IL。 c 作製したGepMOSFETの上面顕微鏡画像

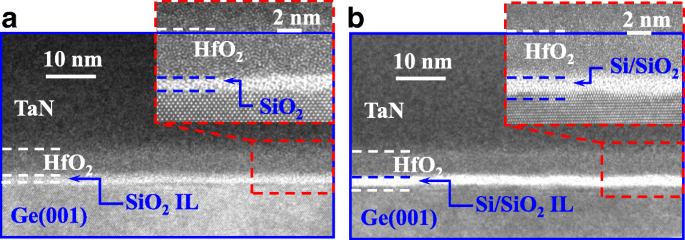

図2a、bは、SiO 2 を使用したhigh-κ/金属ゲートスタックの透過型電子顕微鏡(TEM)画像を示しています。 t のGe(001)チャネル上の/ Si界面層(IL) Si それぞれ0.5および0.9nmです。挿入図は、サンプルの高分解能TEM(HRTEM)画像を示しています。 t のデバイスの場合 Si 0.5 nmの場合、アモルファスSi層は完全に酸化されましたが、0.9 nm t のデバイスの場合 Si 、後続のアニーリングステップ後に約2つのSi単分子層が残った。

a を使用したGepMOSFETゲートスタックの断面TEM画像 0.5 nm t Si および b 0.9 nm t Si 。挿入図のHRTEM画像は、Si / SiO 2 ILはHfO 2 の間で形成されます およびGeチャネル

結果と考察

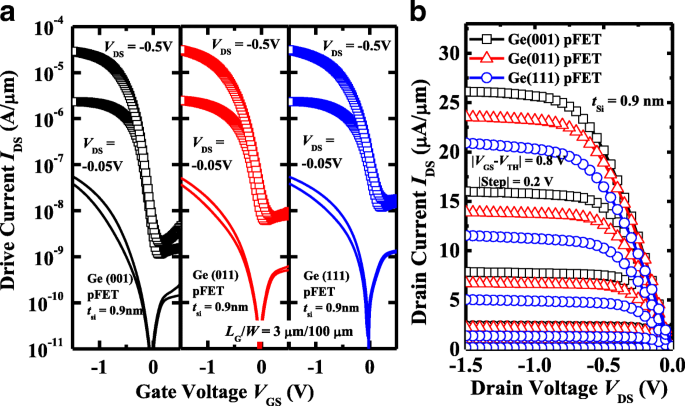

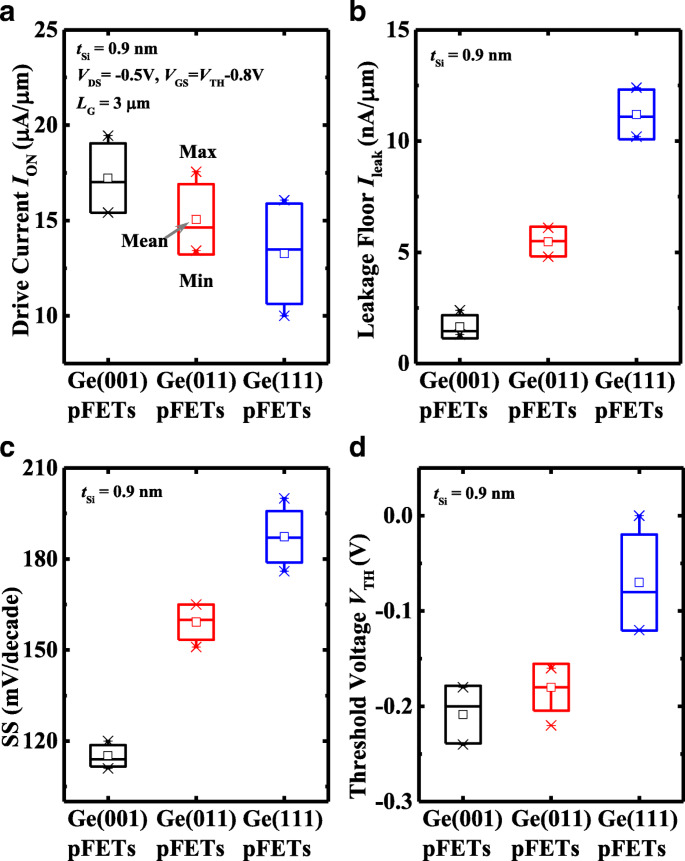

図3aは、測定された I をプロットしたものです。 DS - V GS および私 G - V GS 0.9 nm t の(001)-、(011)-、および(111)配向表面上の典型的なGepMOSFETの曲線 Si 、優れた転写特性を示します。すべてのトランジスタのゲート長は L G 3μmのゲート幅 W 100μmの。チャネル方向は、すべての方向で[110]です。 私 DS - V DS 異なるゲートオーバードライブ V で測定されたデバイスの曲線 GS - V TH 図3bに示します。ここで、しきい値電圧 V TH V として定義されます GS I で DS の10 -7 A /μm。 Ge(001)pMOSFETがより高い駆動電流 I を達成することが観察されています。 オン 固定された V の(011)および(111)表面のトランジスタと比較 GS - V TH 。後で、これがGe(001)pMOSFETの実効正孔移動度μが高いことに起因することを示します。 eff 他の2つの表面方向のデバイスと比較して。 t が固定されたデバイスの電気的性能を包括的に比較します。 Si I を含む0.9nm オン 、漏れ床 I リーク 、サブスレッショルドスイング(SS)、および V TH 特性。 私 リーク 最小の I として定義されます DS V で DS 図4aは、 I の統計プロットを示しています。 オン さまざまな方向のGepMOSFETの場合、および I オン I として定義されました DS V で DS − 0.5Vおよび V GS - V TH − 0.8Vの。このプロットのすべてのトランジスタは L を持っています G 3μmおよび W 100μmの。 (001)指向のデバイスは、改善された平均 I を示します オン (011)および(111)方向のものと比較して、これはより高いμに起因します。 eff 。図4bは、 I を比較しています。 リーク デバイスの場合、Ge(001)トランジスタの I が最も低いことを示しています。 リーク そのうち、Ge(011)pMOSFETの I は低くなっています。 リーク (111)指向のデバイスより。 I に注意する必要があります リーク p + の逆電流によって決定されます ドレイン領域の/ n接合。これは、Ge基板のバックグラウンドn型ドーピング濃度と注入されたp + の活性化の影響を受けます。 ドーパント。さまざまな方向のウェーハのn型ドーピング濃度は完全に同じではありません。表面配向は、S / D領域のドーパント活性化率と再結晶品質に影響を与えます。さらに、 I G I よりも低い DS トランジスタがオンになる前は、 I に影響します。 リーク 。同様に、(001)配向のGe pMOSFETは、他の2つの配向と比較して改善されたSS特性を示します。これは、(001)表面のトランジスタの界面状態のミッドギャップ密度が低いためです D それ 他のデバイスと比較して。図4dは、さまざまな向きのデバイスの V が異なることを示しています。 TH 。図4の結果に基づいて、固定された t であると結論付けられます。 Si 0.9 nmの(001)配向Ge pMOSFETは、最高の電気的特性を取得します。

a 測定された I DS - V GS および私 G - V GS 0.9 nm t の(001)-、(011)-、および(111)配向のGepMOSFETの曲線 Si 優れた転写特性を示します。 b 私 DS - V DS さまざまな V で測定された曲線 GS - V TH デバイス用

a の比較 私 オン 、 b 私 リーク 、 c SS、および d V TH t を備えた(001)-、(011)-、および(111)指向のGepMOSFETの場合 Si 0.9nmの

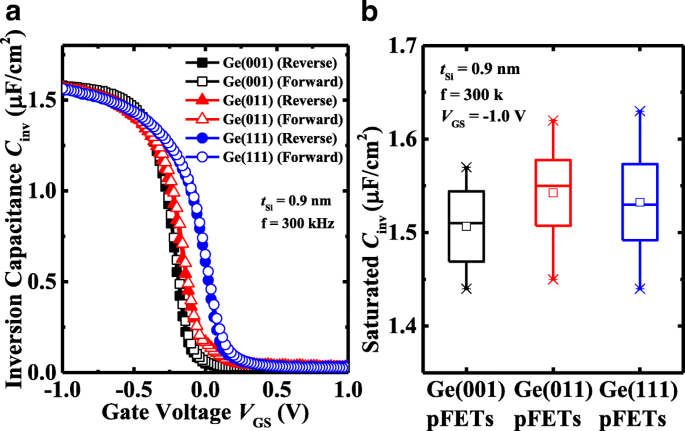

Si / SiO 2 の厚さ 0.9 nm t のトランジスタのIL Si さまざまな表面配向について、反転容量 C を使用して調べます。 inv 対 V GS 図5に示すように、測定。順方向および逆方向の掃引測定では、デバイスのヒステリシスが無視できるほど小さくなります。トランジスタは、同様の大きさの C を示します inv 、〜1.56μF / cm 2 、2.2 nmの容量性有効厚さ(CET)に対応します。図5bは、飽和した C の統計結果を示しています。 inv C のごくわずかな違いを示すデバイスの場合 inv 異なる表面配向のトランジスタで。これは、マグネトロンスパッタリングによるアモルファスSiの不動態化速度が表面配向に依存しないことを示しています。 C の左右シフトのルール inv - V GS 曲線は V の曲線とよく一致しています TH 図4dのデバイスの場合、これは、異なる配向基板でのわずかに異なるドーピング濃度によって引き起こされる可能性があります。

a 反転の比較 C inv - V GS 0.9 nm t のGepMOSFET間の曲線 Si さまざまな向きで。順方向と逆方向の両方のスイープが表示されます。 b 飽和した C の統計プロット inv C でごくわずかな違いを示しているデバイスの inv 反転レジームで

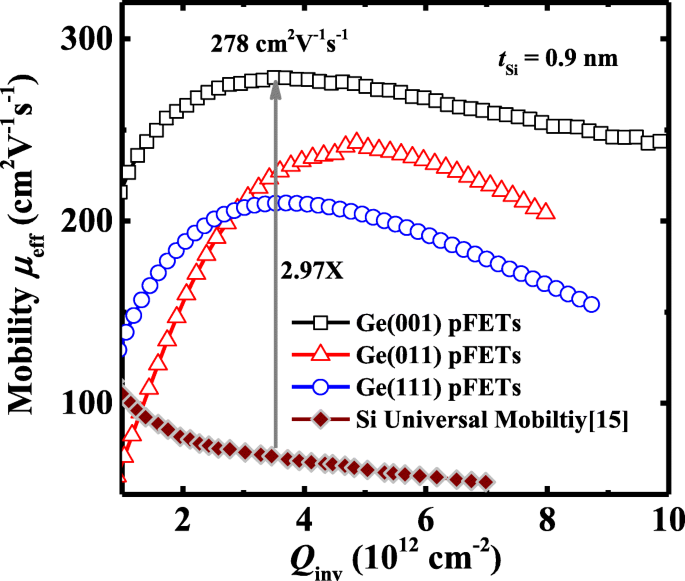

図6は、0.9 nm t のトランジスタの移動度特性を比較しています。 Si さまざまな表面の向きで。 μ eff 全抵抗勾配ベースの方法を使用して抽出されました[14]。 Ge(001)pMOSFETは、(011)および(111)方向のデバイスと比較してはるかに高いチャネル移動度を示します。 (001)基板上のトランジスタはピークμを達成します eff 278 cm 2 反転電荷密度での/ V・s Q inv 〜3.5×10 12 cm −2 、これはSiの普遍的な移動度の2.97倍です。 Si / Ge界面の表面粗さと界面状態の密度( D それ )μに影響を与える可能性があります eff 高い反転キャリア密度でのデバイスの特性。さまざまな表面配向を持つ市販のGeウェーハが表面粗さに明らかな違いを持っている可能性は低いです。したがって、(001)指向のデバイスの移動度の向上は、主に界面状態によるキャリア散乱の減少によるものと推測されます。この作業では、ミッドギャップ D を評価します それ デバイスの、そして固定された t Si 0.9 nmの場合、(001)配向のGe pMOSFETは、実際にミッドギャップが低くなります D それ 他の方向と比較して。

μのプロット eff 対 Q inv 0.9 nm t のGepMOSFETの場合 Si (001)-、(011)-、および(111)配向基板上。 Ge(001)pMOSFETは、μで2.97倍の向上を実現します eff Q で inv 3.5×10 12 cm −2 Siユニバーサルモビリティと比較して。 μ eff 全抵抗勾配ベースの方法を使用して抽出されました[17]

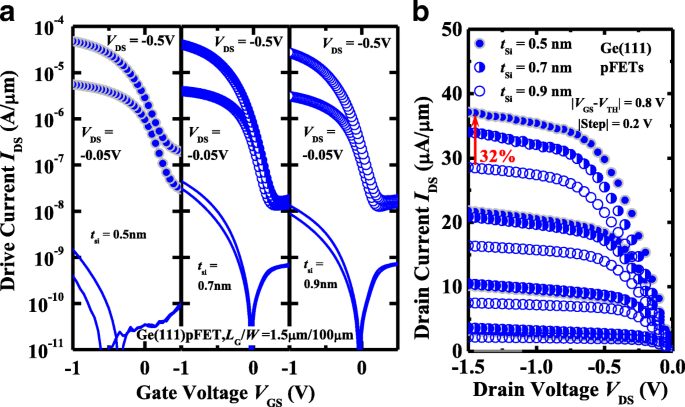

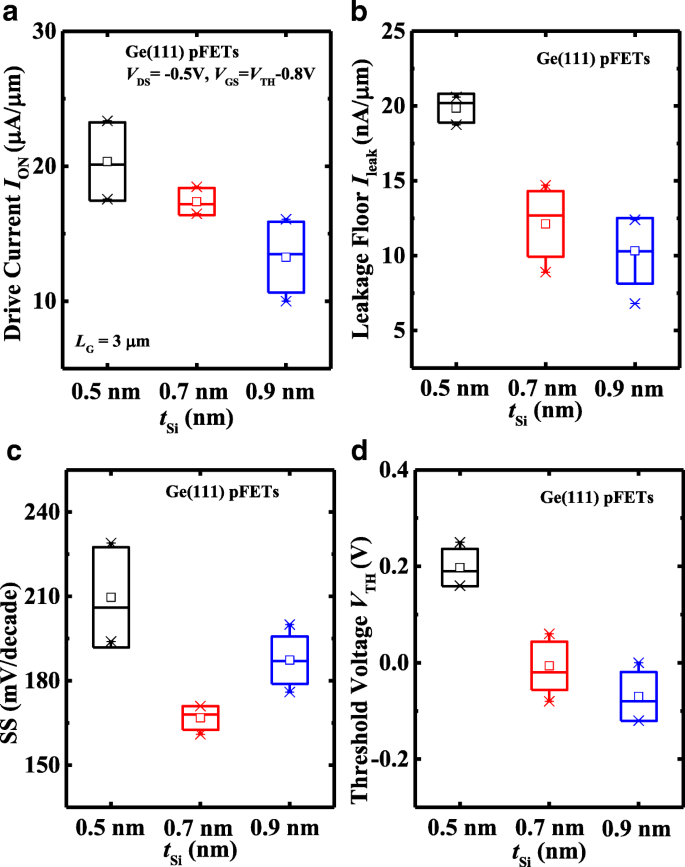

t の影響 Si GepMOSFETの電気的性能に関する研究も行われています。図7a、bは、測定された I を示しています。 DS - V GS および私 DS - V DS それぞれ、 t を備えた(111)配向のGepMOSFETの曲線 Si V で0.5、0.7、0.9nmの DS − 0.05および− 0.5Vの。トランジスタは L を持っています G 1.5μmの。 0.9 nm t のGepMOSFETが観察されます Si t が薄いデバイスと比較して改善された転送特性を示します Si 、しかし私 オン t の増加に伴い、デバイスの Si 。 V で DS − 1.5Vおよび V GS - V TH − 0.8 V、Ge(111)pMOSFET、0.5 nm t Si I が32%向上したことを示しています オン 0.9 nm t のデバイスと比較 Si 。図8は、 I の統計結果をプロットしたものです。 オン 、私 リーク 、SS、および V TH 異なる t を使用した(111)方向のGepMOSFETの Si 。図8aから、0.5 nm t のトランジスタがわかります。 Si 改善された I を達成する オン t が厚いデバイスと比較して Si 、これは0.5 nm t のトランジスタによるものです Si CETが小さく、 C が高くなります inv 。 私が リーク t の増加とともに減少します Si (図8b)、および0.5 nm t のトランジスタ Si は、0.7および0.9 nmのアモルファスSiパッシベーション層を備えたデバイスよりもSS特性が劣っています(図8c)。これは、0.5 nm t のトランジスタが原因である可能性があります。 Si ミッドギャップが高い D それ 。 SSとミッドギャップ D の関係 それ Ge pMOSFETの数は、SS =ln(10)⋅( kT / q)⋅[1 +( C それ + C d )/ C ox ]、ここで C ox 、 C d 、および C それ それぞれ、酸化物容量、空乏層容量、およびインターフェーストラップからの容量です。 C それ q で計算できます × D それ 、 D それ はインターフェーストラップ密度です。 0.5 nm t のトランジスタですが Si C が大きい ox 他の2つのデバイスと比較して、ミッドギャップが高い D それ t が厚いデバイスよりもSSが劣る可能性があります Si 。表面の不動態化も I に影響します リーク ドレインからソースへ。 V のスイープで GS 位置から負に、チャネルは累積モードから反転モードに移行します。ただし、 D それ が高く、チャネル表面の一部のポイントがインターフェーストラップによって固定され、リークパスが形成されて I が増加します。 リーク ドレインからソースへ。図8dに示すように、Ge(111)pMOSFETは V のシフトを示します。 TH 負の V GS t の増加に伴う方向 Si 、これはCETの増加に起因します。さらに、バンドギャップの下半分のトラップの密度は、 t が薄いほど増加するようです。 Si 、 V のシフトにつながる可能性があります TH [2]。

a 私 DS - V GS および私 G - V GS および b 私 DS - V DS さまざまな t を使用したGe(111)pMOSFETの曲線 Si 。 0.5 nm t のトランジスタ Si I で32%の改善を示します オン 0.9 nm t のデバイスと比較 Si V で DS − 1.5Vおよび V GS - V TH − 0.8 V

a の比較 私 オン 、 b 私 リーク 、 c SS、および d V TH 0.5、0.7、および0.9 nm t の(111)指向のGepMOSFETの場合 Si 0.5 nm t のトランジスタを示しています Si より良い私を持っている オン 、しかしより悪いSSと I リーク t が厚いデバイスと比較した特性 Si

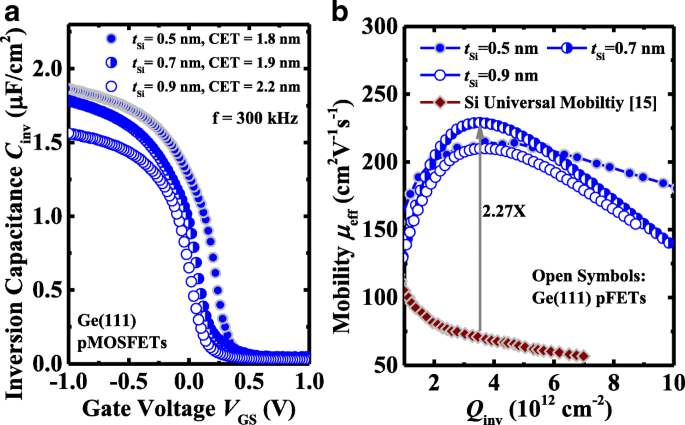

図9aは、 C を示しています。 inv V の関数として GS t の(111)配向表面上のGepMOSFETの曲線 Si 300 kHzの周波数で測定された0.5、0.7、および0.9nmの周波数。反転領域のCET値は、0.5、0.7、および0.9 nm t のデバイスで1.8、1.9、および2.2nmになるように抽出されます。 si 、 それぞれ。 μ eff Q の関数として inv デバイスの特性が抽出され、図9bに示されています。 0.7 nm t の(111)配向Ge pMOSFET si 229 cm 2 の最高ピーク移動度を達成 / V s、これはSiの普遍的な移動度と比較して2.27倍高いです。 0.5 nm t のデバイスに注意する必要があります Si 大幅に改善されたμを示す eff t が厚いトランジスタの上 Si 高い Q inv (例:10 13 cm −2 )。これはまた、より高い I につながります オン 高い V GS - V TH 0.5 nm t のデバイスで Si 0.7および0.9nm t のデバイスと比較 Si 。 μ eff 高い Q inv t として減少します Si 0.5 nmから0.7〜0.9 nmに増加します。これは、表面粗さが大きいほど、キャリアの表面粗さの散乱が強くなるためです。室温でマグネトロンスパッタリングを使用してGe表面を不動態化する間、表面原子の拡散は大幅に抑制されます。したがって、 t の増加に伴い Si 、表面粗さが大きく、図2のHRTEM画像から確認できます。

a C inv - V G 0.5、0.7、および0.9 nm t の(111)指向デバイスの300kHzで測定された特性 Si 。 b μ eff Q の関数として inv GepMOSFETの場合[17]

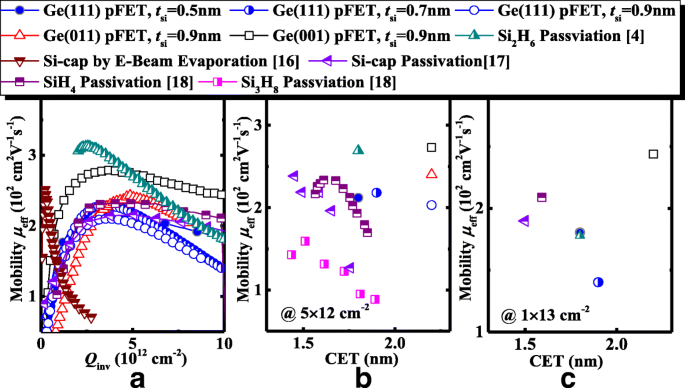

図10では、μのベンチマークを行っています。 eff この作業でのGepMOSFETの、Eビーム蒸着によるSiを含む報告された緩和Geトランジスタのそれらとの比較、SiH 4 、Si 2 H 6、 およびSi 3 H 8 不動態化。参考文献のEビーム蒸着によるアモルファスSiとの比較。 [15]、この作業のGe pMOSFETは、大幅に改善されたμを示します。 eff 。同様のCETでは、マグネトロンスパッタリングによるアモルファスSiパッシベーションを利用したGepMOSFETのμが低いことがわかります。 eff Si 2 のデバイスと比較して H 6 不動態化。アモルファスSiを使用したパッシベーションのプロセスは、キャリアの移動度を高めるためにさらに最適化する必要があります。

a μ eff この作業でのGepMOSFETの場合と、緩和されたGepMOSFETの公開された結果の場合。 b 、 c μのベンチマーク eff Q で抽出 inv =5×10 12 および1×10 13 cm −2 それぞれ、異なるCET値を持つGe pMOSFETの[18、19]

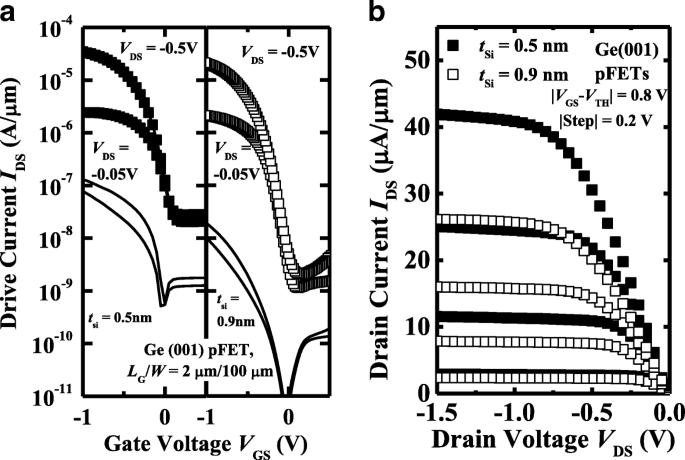

t が異なるGepMOSFET Si (001)方向の表面も特徴づけられます。図11a、bは、測定された I を示しています。 DS - V GS および私 DS - V DS それぞれ、0.5および0.9 nm t のGe(001)pMOSFETのペアの曲線 Si 。 (111)指向のデバイスと同様に、0.5 nm t のGe(001)pMOSFET Si I の改善を得る オン しかし、 I の劣化 リーク 0.9 nm t のトランジスタと比較 Si 。

a 測定された I DS - V GS および私 G - V GS 0.5および0.9nm t の(001)配向GepMOSFETの曲線 Si 。 b 私 DS - V GS デバイスの曲線

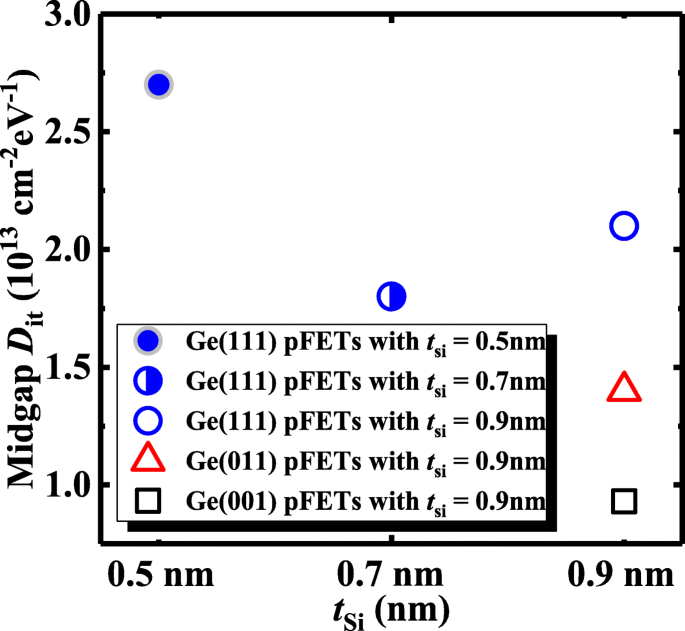

ミッドギャップ D それ Ge pMOSFETの特性は、[16]の方法、および D の値によって研究されています。 それ D によって計算されます それ =[SSlog(e)/( kT / q )− 1] C G / q 、[16]ここで、 q は電子の電荷、 k ボルツマン定数、 T は絶対温度であり、 C G は、単位面積あたりの測定されたゲート容量です。図12は、 D を示しています。 それ さまざまなGe表面配向を持つアモルファスSiの厚さの関数として。 (111)配向の表面の場合、0.7 nm t のデバイス si D が最も低い それ 価値。 0.9 nm t Si 、(001)指向のデバイスは D が低くなります それ 他の方向のトランジスタと比較して。

D それ 対さまざまなGe表面配向のアモルファスSiの厚さ

最後に、表1のさまざまな方向でのGepMOSFETの主要な電気的特性を比較します。 t を固定した場合 Si 、Ge(001)pMOSFETは、他の2つの方向と比較して電気的性能が向上しています。 t を減らすことにより、駆動電流を増やすことができます。 Si 0.9nmから0.5nmまで。これは t が薄いためです。 Si μの劣化を引き起こすことなく、CETを大幅に削減します eff 。

<図>結論

アモルファスSiによって不動態化されたGepMOSFETは、(001)-、(011)-、および(111)配向基板上に示されています。 t で Si 0.9 nmの場合、改善された I オン μが高いため、(011)および(111)方向のデバイスと比較して、(001)方向のGepMOSFETでSS特性が得られます。 eff ミッドギャップを下げる D それ 。 0.9 nm t のGe(001)pMOSFET Si 278 cm 2 のピーク移動度を達成 / V s at a Q inv 3.5×10 12 cm −2 、これはSiの普遍的な移動度の2.97倍です。 I オン t を減らすと、デバイスの割合が向上します。 Si CETの削減による。しかし、より厚い t のGepMOSFET Si そのミッドギャップ D により、優れたサブスレッショルドスイングとリークフロアを示します それ t を増やすことで減らすことができます Si 。

略語

- ALD:

-

原子層堆積

- BF 2 + :

-

フッ化ホウ素イオン

- CET:

-

容量性有効厚さ

- Ge:

-

ゲルマニウム

- GeO x :

-

酸化ゲルマニウム

- HF:

-

フッ化水素酸

- HfO 2 :

-

二酸化ハフニウム

- HRTEM:

-

高分解能透過型電子顕微鏡

- IL:

-

界面層

- MOSFET:

-

金属酸化物半導体電界効果トランジスタ

- Ni:

-

ニッケル

- Si:

-

シリコン

- SS:

-

サブスレッショルドスイング

- TaN:

-

窒化タンタル

- TDMAHf:

-

テトラキス(ジメチルアミド)ハフニウム

ナノマテリアル

- KUHMUTEはSLS3D印刷でモビリティを再設計します

- AFPMを使用した高速3D印刷

- AION500MK3による高速3Dプリント

- AgNWs電極を備えたテクスチャ表面に基づくPEDOT:PSS / n-Si太陽電池の高性能

- ハイブリッド全誘電体-グラフェンメタ表面に基づく制御可能な複屈折を備えた偏光変換器

- 表面構造が変更された高性能有機ナノ構造シリコンハイブリッド太陽電池

- 高PSRRのナノスケール低電力抵抗なし電圧リファレンス

- 太陽照射下での電荷分離と高い光触媒活性を強化するための部分的な表面改質を備えたZnO多孔質ナノシート

- オゾンとプラズマポスト酸化によって形成されたGeOxパッシベーションを備えたGepMOSFET

- ホール移動度の高い非常に薄いアモルファスSnドープIn2O3膜のキャリア輸送を制限する要因に関する新しい洞察

- ZrO2誘電体を備えた高移動度GepMOSFET:ポストアニーリングの影響