ラッチアップ免疫と堅牢なESD保護のためのキャリア再結合構造が組み込まれた新しい高保持電圧SCR

要約

静電放電(ESD)保護用の新しいCMOSプロセス互換の高保持電圧シリコン制御整流子(HHV-SCR)が提案され、シミュレーションと伝送ラインパルス(TLP)テストによって実証されています。新しく導入された正孔(または電子)再結合領域H-RR(またはE-RR)は、寄生PNP(またはNPN)トランジスタベースの少数キャリアをN +(またはP +)層で再結合するだけでなく、追加の再結合を提供してH-RR(またはE-RR)に新たに追加されたP +(またはN +)層による表面アバランシェキャリア。これにより、保持電圧( V )がさらに向上します。 h )。測定された V と比較 h 1.8 Vの低電圧トリガーシリコン制御整流子(LVTSCR)、 V h 十分に高い故障電流( I )を維持しながら、HHV-SCRの電流を8.1Vに上げることができます。 t2 > 2.6 A)。性能指数(FOM)が4倍以上向上しました。

はじめに

半導体統合技術の開発と半導体デバイスの機能サイズの一貫した小型化により、ESDによって引き起こされるデバイスの損傷はさらに深刻になっています。大きなチップ面積を犠牲にして、通常のESD堅牢性を特徴とするダイオードやゲート接地NチャネルMOSFET(ggNMOS)などの従来のデバイスが報告されました[1]。より小さなデバイス寸法で改善されたESD機能を実現するために、低電圧トリガーシリコン制御整流子(LVTSCR)は、単位面積あたりの大電流機能により魅力的なデバイスと見なされてきました[2]。低電圧アプリケーションの場合、低トリガー電圧( V が組み込まれているため) t1 )ggNMOS、優れたESD堅牢性を備えたLVTSCRは、従来のSCRで得られるよりも速いESD応答速度を提供することができます。ただし、強い固有の正のフィードバックにより、 V は非常に低くなります。 h (1〜2 V)、これはラッチアップと一時的なミストリガーの原因です[3]。このような悪影響は、 V を増やすだけで効果的に抑えることができます。 h [3,4,5,6,7,8,9,10,11]。 V の間、デバイスはラッチアップや一時的なミストリガーから解放されます。 h 電源電圧(VDD)より高いです。したがって、N + ESD領域とP + LDD領域がSCRに追加され、 V を改善するために追加のマスクとイオン注入ステップが追加されました。 h [3]。ただし、 V の増加に伴う追加の電力損失により、ESDの堅牢性が低下する可能性があります。 h 。さらに、 V のエミッター電圧クランプ技術 h 許容可能な故障電流による改善( I t2 )も提案されました[5]。それにもかかわらず、 V h 前述のアプローチでは調整不可能であり、それでも用途の広いアプリケーションでは不便で制限があります。

この手紙では、新しい高保持電圧シリコン制御整流子(HHV-SCR)が提案され、TCADシミュレーションとTLPテストによって実証されています。デバイスは同時に高い V を達成します h 、高い I t2 、および調整可能な V h 追加のマスクやステップなしで。 V であることを検証するために、TLPテストが実行されました。 h 十分に高い I を維持しながら、効果的に改善することができます t2 。テスト結果によると、HHV-SCRは4倍以上の V を備えています h I の劣化はごくわずかであるLVTSCRのそれより t2 。

メソッド

この作業では、キャリア再結合構造が埋め込まれた新しい高保持電圧SCRを調査します。数値シミュレーションでは、物理モデルIMPACT.I、BGN、CONMOB、FLDMOB、SRH、およびSRFMOBが使用されます。モデルに基づいて、H-RRとE-RRは、高い V を達成するように最適化されています。 h 高い P M 。製造されたHHV-SCRとLVTSCRは、TLPシステムによってテストされます。

構造とメカニズム

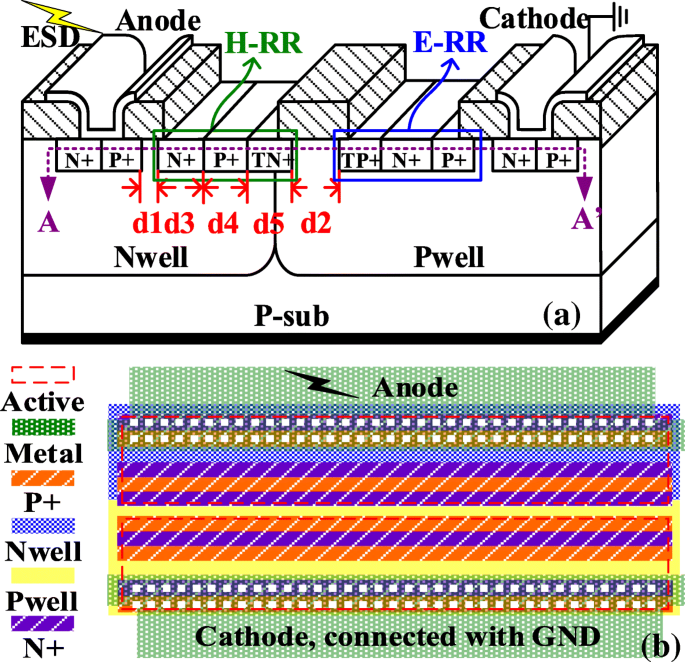

提案されたHHV-SCRの概略断面図とレイアウト図をそれぞれ図1a、bに示します。新たに導入されたH-RRとE-RRは、フローティングN +とP +によって形成され、それぞれアノード領域とカソード領域のN +とP +と同じです。 H-RRのフローティングN +(またはE-RRのフローティングP +)は、アノードのP +領域(またはカソードのN +領域)の隣に配置されます。さらに、H-RRの新しいフローティングP +(またはE-RRのフローティングN +)も、前述のH-RRのフローティングN +(またはE-RRのフローティングP +)の隣にあります。 H-RR(TN +)の低トリガーN +およびE-RR(TP +)の低トリガーP +も、アノード(またはカソード)のN +(またはP +)領域と同じプロセスで製造され、 V t1 許容範囲内。正のESD電圧として( V ESD )特定のレベルまで上昇すると、低ブレークダウン電圧のTN + / Pウェル/ TP +ジャンクションが最初にブレークダウンし、続いてアバランシェ電流によってトリガーされる寄生トランジスタのスナップバックが発生します。寄生BJTの強い正のフィードバックは、かなり低い V の原因です。 h LVTSCRの。 HHV-SCRでは、H-RRのN +(またはE-RRのP +)は、アノードP +(またはカソードN +)のエッジから注入された少数キャリアを再結合し、電流ゲイン(β )寄生PNP(またはNPN)の)であり、表面のバイポーラ効果を排除します。重要なことに、H-RRのP +(またはE-RRのN +)は、表面の電子(または正孔)を再結合することにより、表面の低抵抗経路をブロックします。 P +なしのH-RR(またはN +なしのE-RR)と比較して、H-RRの新しいP +(またはE-RRのN +)は、カソードから注入された表面電子(または正孔)を排除するための追加の再結合を提供します(またはアノード)および衝突電離によって誘発されたもの(図3aに示す)。これにより、 V がさらに増加します。 h 。これらの変更を組み合わせることにより、 FOM が大幅に改善されます。 検証されます。性能指数(FOM)は[7]から引用され、FOM =( V で与えられる単一デバイスの許容電力密度として定義されます。 h ・私 t2 )/( N ・ W ) V を評価する h および私 t2 単一デバイスのパフォーマンス。一般的に、 V の改善を伴う h パフォーマンス、それでも I の劣化を引き起こします t2 消費電力が大きいためです。したがって、FOMが高いということは、単一のデバイスがより高い V でより高い電流能力を達成できることを意味します。 h レベル( N スタッキングデバイスの番号です。 W はデバイスの幅です。

a 提案されたHHV-SCRの概略断面図。 b 提案されたHHV-SCRのレイアウト図

結果と考察

シミュレーション結果

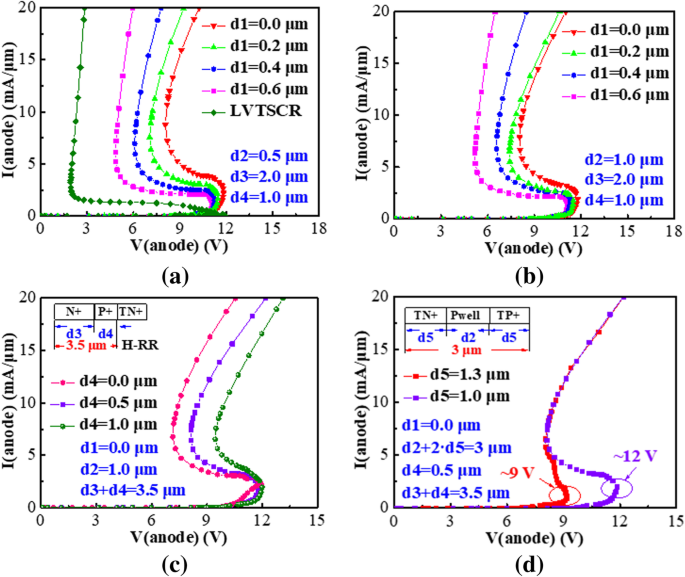

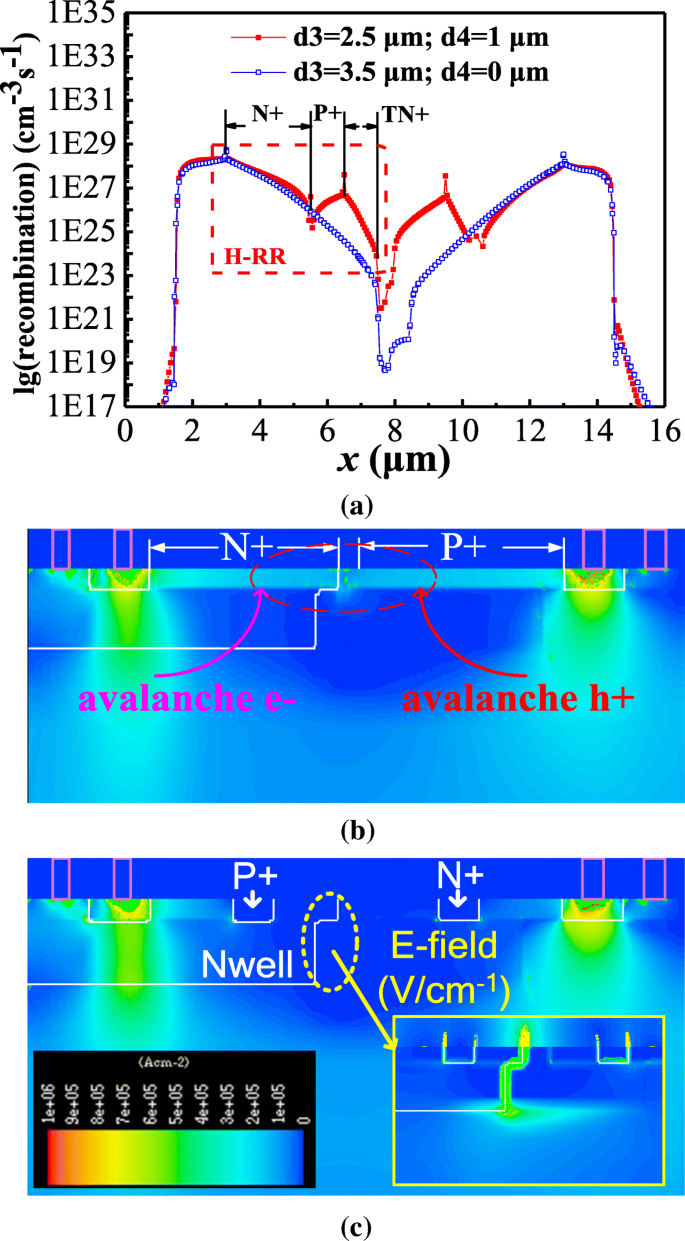

デバイスの特性は、TCAD Mediciによって研究およびシミュレーションされ、衝突電離や濃度依存移動度モデルなどの対応するモデルが使用されました。 LVTSCRおよびHHV-SCRのシミュレートされたI-V曲線を図2に示します。 V h LVTSCRの電圧は1.8Vと低く、 V h HHV-SCRの電圧は4.6Vから8.1Vに改善され、d2 =0.5μmの場合、d1は0.6μmから0μmに減少します。実際、H-RRのN +(またはE-RRのP +)の組換え能力を改善して、より低いβを得るには、より小さなd1が好まれます。 、これは、HHV-SCRが常に最高の V を達成することを説明しています h d1 =0μmの場合。図2bのシミュレーション結果は、 V h HHV-SCRの特性は、デバイスの長さが長くなるため、d2が0.5から1μmに増加することでさらに改善されます。デモンストレーションでは、H-RRのP +(またはE-RRのN +)も V を増加させる重要な要素です。 h 。シミュレーション結果を図2cに示します。 d3 + d4が固定されたH-RR(またはE-RR)が、N +(またはP +)の大量ドーピングによって完全に形成される場合(たとえば、d3 =3.5μm、d4 =0μm)、シミュレートされた V > h は7.1Vです。P+をH-RR内に挿入し、N +をE-RR内に固定d3 + d4(たとえば、d3 =2.5μm、d4 =1.0μm)で挿入することにより、シミュレートされた V h 約9.5Vまで上げることができます。H-RRの新しいP +(またはH-RRのN +)は、表面なだれ電子(または正孔)を再結合して表面電流経路を遮断するのに効果的であると推測できます。したがって、より高い V h HHV-SCRが同じ保持電流( I )を維持するために必要です h )。図3aに示されている再結合曲線のみのAA '線は、H-RRの新しいP +(またはE-RRのN +)によって誘発される再結合率の増加を示しています。 V を確保するためにTN +とTP +が採用されています t1 許容範囲内。固定されたd5 + d2 + d5でd2とd5を調整することにより、 V t1 V への影響を無視して、5V回路の設計ウィンドウを満たすためにHHV-SCRの電圧を12Vから9.0Vに大幅に下げることができます。 h 、図2dに示されています。保持点でのシミュレートされたデバイスの電流分布図も、それぞれ図3b、cに示されています。 d3 =3.5μm、d4 =0μmのHHV-SCRの電流分布と比較すると、提案されたHHV-SCRの表面電流経路は、H-RRのP +とEのN +の恩恵を受けた追加の再結合率のためにブロックされます。 -RR。

a でd1が0μmから0.6μmに増加する、従来のLVTSCRおよび提案されたHHV-SCRのシミュレートされたスナップバックI-V特性 d2 =0.5μmおよび b d2 =1μm。 c 固定d3 + d4(d3 + d4 =3.5μm)のd3とd4が異なるHHV-SCRのI-V曲線。 d さまざまな V を使用したHHV-SCRのI-V曲線 t1

a 再結合分布曲線、および( b を使用したHHV-SCRの電流分布 )d3 =3.5μm、d4 =0μm、および( c )d3 =2.5μm、d4 =1μm

実験結果

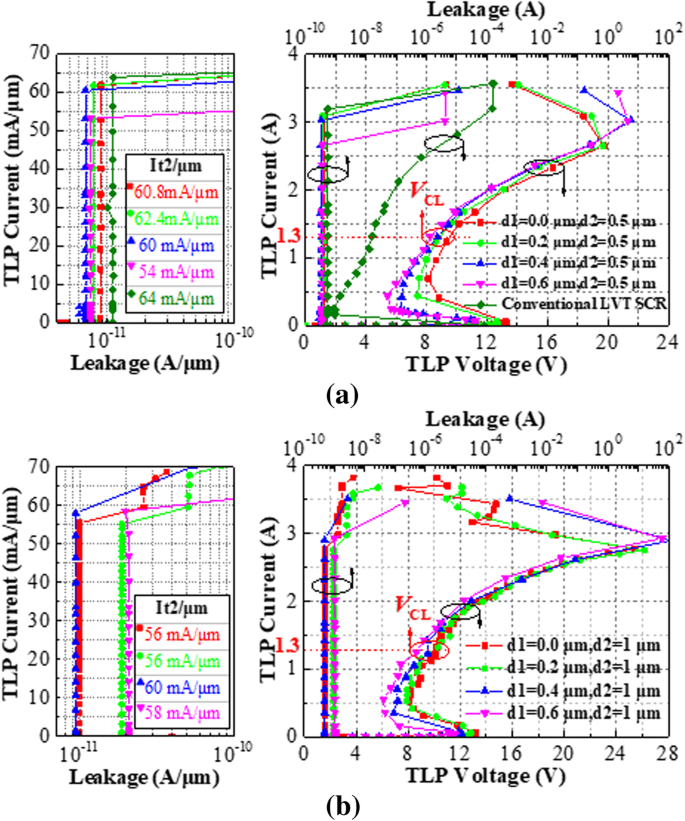

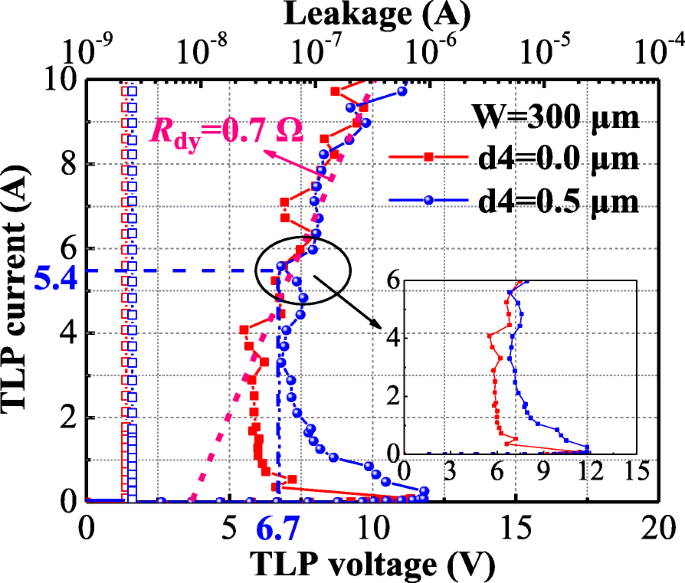

製造されたデバイスは、TLPシステムによってテストされます。テストされたすべてのSCRの全幅(W)は50μmで、パラメーターの比較のために1本の指で使用します(表1)。テストされたすべてのデバイスは、同様のレイアウト領域を占めています。デバイスパラメータを表2に示します。図4aは、d2 =0.5μmのHHV-SCR(デバイスB1と呼ばれる)とLVTSCRのTLP測定曲線を示しています。実験結果によると、 V h HHV-SCRの電圧は5.5から8.0Vに増加し、d1は0.6μmから0.0μmに減少します。これは、従来のLVTSCRで得られた1.8Vよりもはるかに高い値です。 d2が0.5から1μmに増加すると、対応するHHV-SCR(デバイスB2と呼ばれる)はより高い V を取得します。 h 図4bに示されています。設計ウィンドウを考慮して、クランプ電圧( V CL )与えられたインデックスの下でも、クランプ能力を評価するための重要なパラメータです。テスト結果から、 V CL シングルフィンガーのHHV-SCRも、HBM =2 kV( I )で許容範囲内に保たれます。 TLP =1.3 A)指の幅はわずか50μmですが。ただし、すべてのデバイスが適格な V を提供できるわけではありません CL V が高いため、より強いESDストレス下で h 大きな動的抵抗( R dy )デバイスの幅が小さすぎるために発生します。より高いオンチップESD要件を満たすために、指の幅は、d1 =0.6μm、d4 =0.5μm、およびd1 =0.6μm、d4 =0μmの許容可能な300μmに拡張されます。図5に示すTLPテストは、d4 =0.5μmのHHV-SCRが非常に低い R を特徴としていることを示しています。 dy (約0.7Ω)、優れたESD堅牢性( I t2 > 10 A)および高い V h 6.7Vの。 V CL I では6.7Vと低いです TLP =5.4 A(HBM =8KV)。さらに、より高い V h d4 =0μmのSCRのTLP曲線と比較して、H-RRのP +(またはE-RRのN +)の恩恵も証明されています。 50μmのシングルフィンガーデバイスのテスト結果を表1に示します。

<図> <図>

ユニット幅での実験的な故障電流と、従来のLVTSCRおよび a を備えた提案されたHHV-SCRの対応するTLPI-V特性 d2 =0.5μmおよび b W でd2 =1μm =50μm

d1 =0.6μmでd4 =0.0μmおよびd4 =1.0μmのHHV-SCRの実験的TLP特性、 W =300μm

結論

新しいCMOSプロセス互換のHHV-SCRは、TCADシミュレーションとTLPシステムによって研究および測定されます。従来のLVTSCRと比較して、HHV-SCRの機能は大幅に改善された V h ( V で450%以上の改善 h 達成されます)そしてチップ領域を犠牲にすることなく。さらに、 V h HHV-SCRの電圧は5.5Vから8.1Vに調整して、さまざまな V を満たすことができます。 h I の劣化が無視できる要件 t2 。 P に関して M 、従来のLVTSCRと比較して、200%を超える改善も達成されています。

データと資料の可用性

この調査中に生成または分析されたすべてのデータは、この公開された記事に含まれています。

ナノマテリアル

- マイクロコントローラと組み込みシステムのIC技術に関する簡単な説明

- マキシム:DC-DCレギュレータとサージ保護を備えたデュアルIO-Linkトランシーバ

- TRS-STAR:価値のある堅牢でファンレスの組み込みシステム

- In VivoCTイメージングおよび腎クリアランス特性のための新しい生体適合性AuNanostars @PEGナノ粒子

- スーパーキャパシターの電極材料としての階層的多孔質構造を持つ単分散カーボンナノスフェア

- スパイラル型アンテナによるマイクロブリッジ構造のTHzマイクロボロメータの周波数変調と吸収改善

- 酸化還元刺激によって誘発される放出のためのナノ粒子を標的とする新規の二重ミトコンドリアおよびCD44受容体

- GeSiSnナノアイランドと歪み層を備えた半導体膜の形態、構造、および光学特性

- 直接メタノール燃料電池用の新しい陽極触媒のサポート:特性評価と単一セル性能

- 自動化とサイバーセキュリティ:顧客の完全な保護

- PCB材料と高電圧用の設計