安定性と電源除去ブーストを備えた過渡強化電圧レギュレータ

要約

この論文では、過渡増強と過電流保護(OCP)を統合した高安定電圧レギュレータ(VR)を提案します。低電圧デバイスの性能と面積の利点を考慮して、提案されたVRのほとんどの制御部分は、安定化された出力電圧によって供給されます。これにより、電源除去(PSR)ブーストを備えたセルフパワー技術(SPT)が形成されます。さらに、安定性と過渡応答は動的負荷技術(DLT)によって強化されます。埋め込まれた過電流フィードバックループも採用され、過負荷状態での損傷から提示されたVRを保護します。提案されたVRは、標準の350 nm BCDテクノロジーで実装されており、その結果は、VRが5.5〜30 Vの入力電圧、0〜30 mAの負荷範囲、および0.1〜3.3μFの出力コンデンサで安定して動作できることを示しています。 2.98μV/ Vのラインレギュレーションと0.233mV / mAの負荷レギュレーションは、40mAの電流制限で実現されます。 PSRは、0.1μFの出力コンデンサを使用した場合、-64dBより最大10MHzの方が優れています。

はじめに

最新のナノメートルスケールのシステムオンチップ(SoC)設計では、通常、サブブロックが異なれば、特定の機能を実現するために異なる供給レールが必要になります。さらに、SoCシステム全体が広範囲の入力電圧で動作し、電源条件の変化に影響されない高性能を提供する必要がある場合があります[1]。したがって、ナノメートルスケールの技術で実装された広い入力電圧範囲の電圧レギュレータ(VR)は、この種のアプリケーションに最も適した候補の1つです。リニアVRは、スイッチングレギュレータやチャージポンプなどのスイッチング対応製品と比較して、高精度、低出力ノイズ、コンパクトサイズという利点があります。ほとんどのリニアVRは、単一の電源で電圧調整機能を実行しますが、広い電源範囲、低ノイズ、高速過渡、高負荷機能、および追加の保護機能の組み合わせを実現できるのはごくわずかです[2、3、4]。 。

広い電源範囲を実現するためには、高圧に耐えられるトランジスタの活用が必要です。ただし、この種のトランジスタは通常、より多くの領域を占有し、標準のトランジスタと比較してパフォーマンスが低下します。高電圧トランジスタの使用を減らすための既存のソリューションの2つは、プリレギュレータ方式[5、6]とスタック型低電圧トランジスタ方式[7、8]です。前者は、追加のプリレギュレータを使用して、コアレギュレータに内部供給電圧を提供します。後者は、トランジスタの端子電圧を技術限界内に維持するために、適切に設計されたスタック型低電圧トランジスタを実装しています[7]。ただし、これらの方法では電圧ヘッドルームが制限されます。この論文では、セルフパワー技術(SPT)を採用して広い電源範囲を実現しています。つまり、レギュレーションループ内のほとんどのコアモジュールは、提案されたVRのレギュレートされた出力電圧によって供給されます[9]。回路を追加しなくても、SPTによってVRのパフォーマンスを向上させ、高電圧デバイスの数を減らすことができます。

SPTを使用することにより、エラーアンプ(EA)の最初のゲインステージは、提案されたVRの安定化された出力電圧によって供給されます。 EAの第2ステージを注意深く設計することにより、入力電圧の高周波ノイズはEAの出力電圧にほとんど影響を与えません。さらに、この論文では、N型パワートランジスタアーキテクチャを採用しています。したがって、提案されたレギュレータは、高い電源除去(PSR)と優れたノイズ性能を備えています[10、11、12、13、14、15]。

高速過渡応答は、VRのパフォーマンスを測定するための重要な指標でもあります[16、17、18、19、20]。これは通常、高速化ループを追加することで実現されます[21]。この論文では、過渡的強化は動的負荷技術(DLT)によって実現されます。過渡応答手順中に、DLTは負荷条件に応じて変化する追加の電流を導入して動的負荷として機能し、それによって安定化出力電圧のオーバーシュートとアンダーシュートを抑制することができます[9]。

DLTの助けを借りて、追加の負荷電流が非支配的な極位置の変動を減らすことができるので、広い負荷範囲内のループ安定性が強化されます。ループを安定させるために、ヌル抵抗を使用したミラー補償を使用して低周波数極を生成し、追加のゼロを使用して出力極を補償します。さらに、出力コンデンサと直列の抵抗は、パワートランジスタの寄生ゲート容量によって生成された極を補償するために別のゼロを導入します[6、9、22、23]。

最後に、埋め込まれた電流制限ループは、過電流による損傷を回避し、提案されたVRの信頼性を向上させるように設計されています[9、24、25、26、27]。

この論文は次のように構成されています。提案されたVRの原理とメカニズムは、過電流保護(OCP)回路、DLTおよび過渡増強回路、安定性ブースティング方法、およびPSR分析を含む「方法」セクションに示されています。パフォーマンスの結果と他の関連する公開された文献との比較は、「結果と考察」のセクションに示されています。 「結論」セクションでは、提案されたVRの結論を導き出します。

メソッド

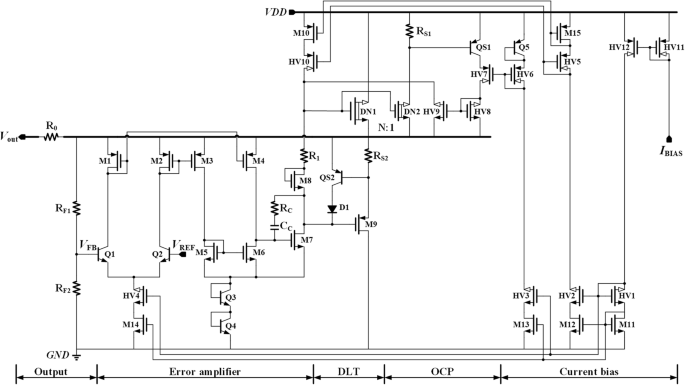

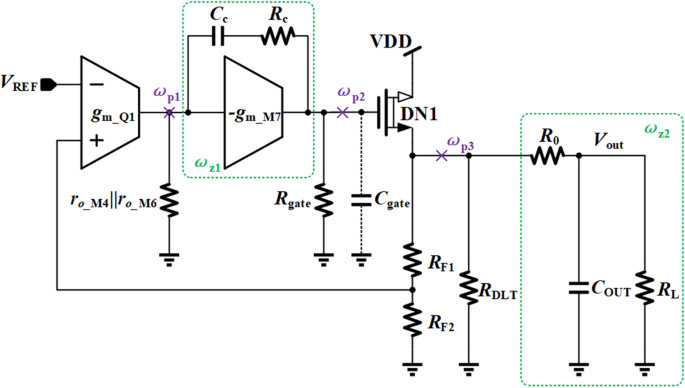

提案されたVRの詳細な回路を図1に示します。標準の低電圧MOSトランジスタ、高電圧トランジスタ、BJT、N型空乏型LDMOS(横方向拡散MOS)トランジスタ、およびダイオードの名前はM n > 、HV n 、Q n 、DN n 、およびD n 、それぞれ図では、 n 関連するデバイスのシーケンス番号です。

提案されたVRの詳細な回路

提案されたVRには、主に5つのサブモジュールが含まれています。電流バイアス、OCP、DLT、EA、および出力ステージです。電流バイアス回路は、レギュレータシステム全体にバイアス電流を供給します[12、14]。基準電圧はさまざまな方法で生成できます[1]。詳細な回路はここには示されていません。埋め込まれた電流制限ループは、負荷電流をプリセット値に制限するOCP回路として機能します。 DLTによって実装される過渡増強回路は、過渡手順中に負荷電流を適応的に変更することにより、オーバーシュートとアンダーシュート抑制を実現します。負帰還調整ループは、EAと出力電圧を調整するための出力電力段によって形成されます。出力電圧 V を仮定します OUT したがって、フィードバック電圧 V FB が所望の値よりも低い場合、パワートランジスタDN1のゲート電圧は、出力電圧を増加させるためにレギュレーションループの助けを借りて引き上げられ、逆もまた同様である。最後に、出力電圧は

で安定します。 $$ {V} _ {\ mathrm {OUT}} \ approx {V} _1 ={V} _ {\ mathrm {REF}} \ left({R} _ {\ mathrm {f} 1} + {R} _ {\ mathrm {f} 2} \ right)/ {R} _ {\ mathrm {f} 2} $$(1)図1では、提案されたVRの出力電圧が、SPTと呼ばれるEAの最初のゲインステージにも電力を供給していることがわかります。この電力多重化技術を使用すると、レギュレーションループ内のほとんどのデバイスを低電圧デバイスで実装できます。高電圧デバイスと比較して、低電圧デバイスは、パフォーマンスが高く、コストが低く、面積が小さいため、提案されたレギュレーションループは優れたレギュレーション能力をはるかに容易に実現します。 EAの第2ステージでは、Q3とQ4を追加して、M7、V DS_M7 のドレイン-ソース間電圧を制限するために採用されている接地供給レールを持ち上げます。 。言い換えれば、Q3とQ4は、M7の大きな電圧圧力を防ぐことができます。

簡単にするために、簡略化された回路は、後続の分析でイノベーションのアイデアを説明するために使用されます。

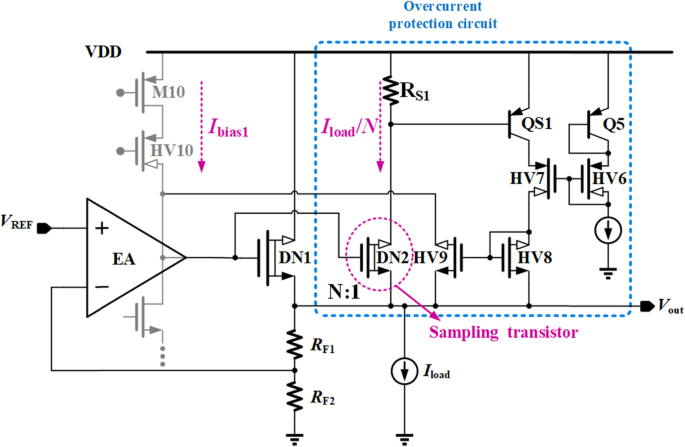

提案されたOCP回路

図2に、提案されたOCP回路を示します。提案された電流制限ループは、さまざまな負荷条件に応じて動作モードを自動的に変更できます。提案されたVRの最大電流は、過負荷が発生したときにパワートランジスタのゲート電圧を下げることで制限できます。

提案されたOCPの原則

提案されたOCPのメカニズムは次のとおりです。サンプリングトランジスタDN2は、負荷電流 I にほぼ等しいDN1を流れる電流を比例的に検出します。 ロード 、これにより、 R の両端の電圧降下が発生します S1 、 V RS1 、負荷電流レベルを反映します。一度 V RS1 QS1、HV8、およびHV9のターンオン電圧に達すると、EAの第2ステージからの電流をバイパスするためのカレントミラーが形成されます。次に、DN1のゲート電圧をプルダウンして、負荷電流をプリセット値に制限します。これは、次のように表すことができます。

$$ {I} _ {\ mathrm {Load}} \ le N \ times \ left({V} _ {EB \ left(\ mathrm {QS} 1 \ right)} / {R} _ {S1} \ right )$$(2)ここで N DN1とDN2のサイズ係数比です。 Q5とHV6の目的は、HV7に適切なバイアス電圧を供給し、QS1を過電圧状態から保護することです。

提案されたOCPには負のフィードバックループが埋め込まれています。ループゲイン T と支配的な極 p ドミナント この電流制限ループのは、

によって与えられます。 $$ T ={g} _ {m \ _ \ mathrm {DN} 2} {R} _ {S1} {g} _ {m \ _ \ mathrm {QS} 1} {R} _ {\ mathrm {gate } \ _ \ mathrm {OC}} $$(3)$$ {p} _ {\ mathrm {dominant}} =1 / \ left({R} _ {\ mathrm {gate} \ _ \ mathrm {OC} } {C} _ {\ mathrm {gate}} \ right)$$(4)ここで g m_DN2 および g m_QS1 DN2とQS1の相互コンダクタンスです。 R gate_OC ≈( g m_HV10 r o_HV10 r o_M10 )|| r o_M7 || r o_HV9 および C ゲート ≈ C gs_DN1 は、過電流が発生したときのパワートランジスタDN1のゲートノードでの等価出力抵抗と容量です。提案されたVRが通常過電流なしで動作する場合、HV9はカットオフ領域にあるため、 R という名前のDN1のゲートノードでの等価出力抵抗 ゲート [( g m_HV10 r o_HV10 r o_M10 )|| r o_M7 ]。

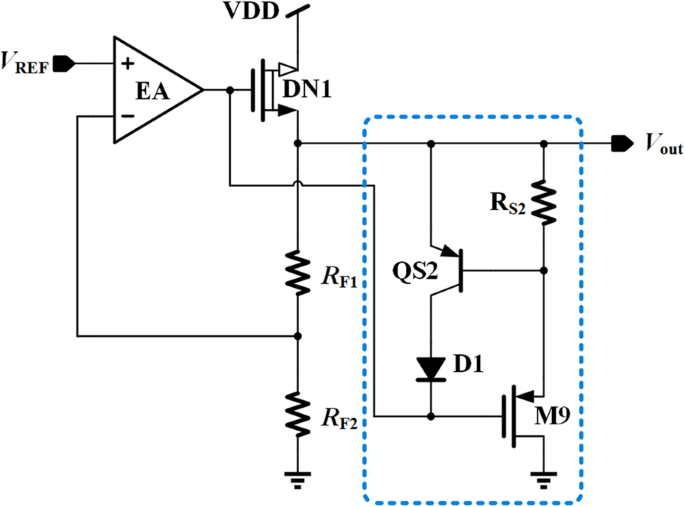

提案されたDLTおよび過渡強化回路

図3に、DLTを使用した過渡増強回路を示します。負荷電流はVgs_DN1に比例し、Vsg_M9に反比例するため、M9を流れる電流は、軽負荷状態では大きく、高負荷状態ではゼロに近くなります。したがって、負荷電流が増加すると、減少した電流が総出力負荷に導入される可能性があります。この方法により、この回路を動的負荷に均等化することができます。これは、レギュレーションループの過渡的な強化と安定性の向上の両方に役立ちます。

提案された過渡増強回路

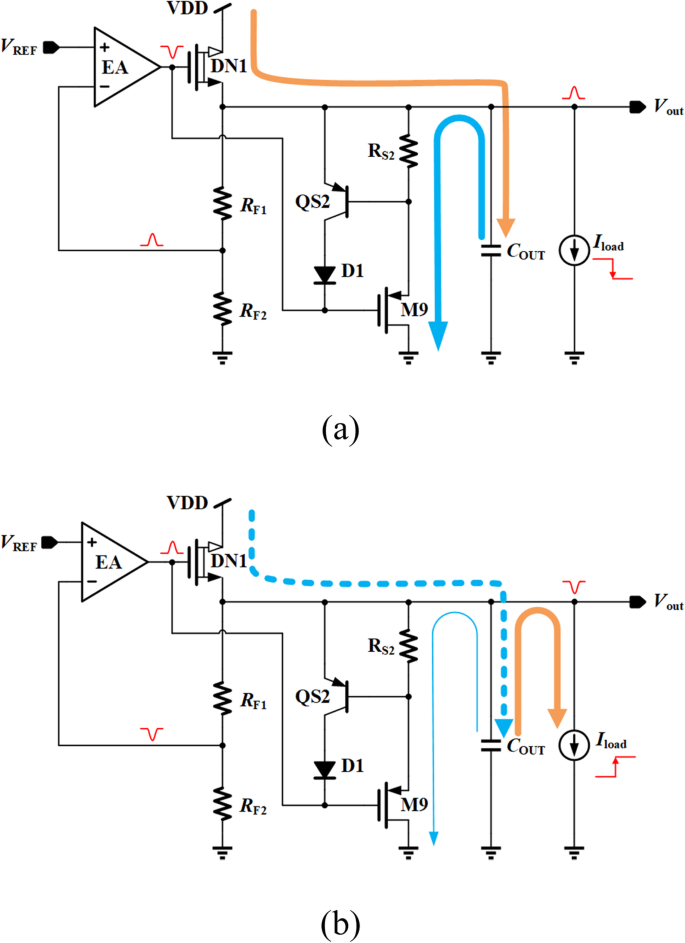

詳細な過渡エンハンスメントの動作原理は次のとおりです。負荷電流が急激に減少した場合、ループ調整能力とスルーレートが制限されているため、パワートランジスタDN1を流れる電流はすぐには変化しません。図4aに黄色のパスとして示されているこの電流は、出力電圧でオーバーシュートを引き起こし、 R の両端の電圧降下を増加させます。 S2 とM9。次に、 R を流れる追加の電流 S2 図4aに青い経路として示されているM9は、調整された出力で生成され、不要な黄色の経路電流を相殺します。したがって、出力電圧スパイクは効果的に低減されます。

提案されたVRの過渡応答。 a 重負荷から軽負荷への電流変化。 b 軽負荷から重負荷への負荷電流の変化

図4bは、負荷電流が軽度から重度に変化する場合を示しています。この場合、安定化された出力でアンダーシュートが発生し、次に R を流れる電流が発生します。 S2 そしてM9は減少します。これは、電流負荷を減らすことと同等であるため、パワートランジスタDN1を流れる正味電流が増加し、アンダーシュート電圧の抑制を実現できます。

M9を過電流から保護するために、QS2とD1が追加されています。 R の両端の電圧が S2 がQS2のターンオン電圧よりも大きい場合、余分な電流がQS2とD1に流れます。 M9の最大電流は

に設定されています $$ {I} _ {\ mathrm {M} 9 \ _ \ max} \ le \ left({V} _ {BE \ _ QS2} / {R} _ {S2} \ right)$$(5)D1の目的は、QS2が逆増幅領域に落ちて、逆電流が流れるのを防ぐことです。これは、M9電流制限機能の異常な状態です。

提案されたVRの安定性の向上

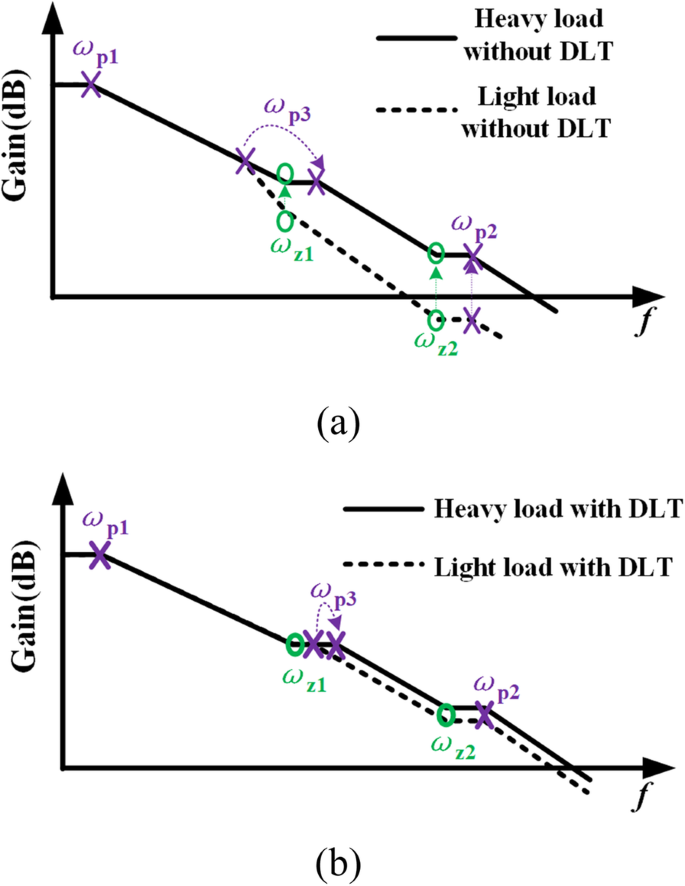

図5に示すように、3つの極がありますω p1 、ω p2 、およびω p3 、および2つのゼロω z1 およびω z2 制御ループ内で、提案されたVRのループゲインは

$$ {A} _ {\ mathrm {Vloop}} ={A} _O \ beta $$(6)

提案されたVRの極と零点の分布

ここで A O はVRの開ループゲインであり、β はフィードバック係数です

$$ {A} _O ={A} _ {\ mathrm {CD} 0} {A} _ {E0} \ frac {\ left(1 + s / {\ omega} _ {Z1} \ right)\ left( 1 + s / {\ omega} _ {Z2} \ right)} {\ left(1 + s / {\ omega} _ {P1} \ right)\ left(1 + s / {\ omega} _ {P3} \ right)\ left(1 + s / {\ omega} _ {P2} \ right)} $$(7)$$ \ beta =\ frac {R _ {\ mathrm {F} 2}} {R _ {\ mathrm {F} 1} + {R} _ {\ mathrm {F} 2}} $$(8)ここで A CD0 ≈1は、電圧フォロワおよび A として動作するパワーステージの低周波ゲインです。 E0 EAの低周波ゲインです

$$ {A} _ {E0} ={g} _ {m \ _Q1} \ left({r} _ {o \ _M4} \ Big \ Vert {r} _ {o \ _M6} \ right){g} _ {m \ _M7} {R} _ {\ mathrm {gate}} $$(9)DN1のゲートノードでのミラー効果と寄生容量を考慮すると、極と零点は[13]

と記述されます。 $$ {\ omega} _ {p1} =1 / \ left [{g} _ {m \ _M7} {R} _ {\ mathrm {gate}} {C} _c \ times \ left({r} _ { o \ _M4} \ Big \ Vert {r} _ {o \ _M6} \ right)\ right] $$(10)$$ {\ omega} _ {p2} ={g} _ {m \ _M7} / { C} _ {\ mathrm {gate}} $$(11)$$ {\ omega} _ {p3} =1 / \ left \ {\ left [{R} _L \ Big \ Vert \ left({g} _ {m \ _ \ mathrm {DN} 1} ^ {-1} \ Big \ Vert {R} _ {\ mathrm {DLT}} + {R} _0 \ right)\ right] {C} _ {\ mathrm { OUT}} \ right \} $$(12)$$ {\ omega} _ {z1} =1 / \ left [{C} _c \ left({R} _c-1 / {g} _ {m \ _M7 } \ right)\ right] $$(13)$$ {\ omega} _ {z2} =1 / \ left [\ left({R} _0 \ Big \ Vert {R} _L \ right){C} _ {\ mathrm {OUT}} \ right] $$(14)ここで R DLT 過渡増強回路の等価抵抗です。 C OUT 提案されたVRの出力コンデンサです。

補償コンデンサ C C ( g m_M7 R ゲート )ノードp1でのミラー効果により、極ω p1 支配的な極です。 2番目の極はωである必要があります p3 、 C OUT 通常、数マイクロファラッドの範囲です。寄生コンデンサ C ゲート は比較的大きく、ノードp1の等価容量と出力コンデンサの両方よりも小さいです。また、ノードp2の抵抗は1 / g です。 m_M7 。したがって、極ω p2 高周波に位置しています。ゼロω z1 中周波極をキャンセルすることですω p3 。抵抗器 R 0 ゼロωを生成します z2 内部寄生極を補償するためにω p2 。提案されたVRの安定性は、抵抗器 R として改善できます。 0 増加しています。ただし、抵抗器 R 0 負荷電流による電圧降下による出力電圧の誤差が大きくなります。したがって、抵抗器 R 0 出力電圧の精度とループの安定性の間で適切なトレードオフを行うために、適切な値に設定する必要があります。

DLTのない従来の電圧レギュレータでは、負荷電流が誘導電力トランジスタの相互コンダクタンスの変動を変化させるため、出力ノードの極は異なる周波数になります。負荷電流が増加すると、パワートランジスタの相互コンダクタンス g m _DN1 図6aに示すように、が増加するため、出力極は高周波に向かって移動し、他の零点と極は同じ位置に維持されます。これにより、システムの周波数補償がより困難になり、軽負荷状態での過渡応答が遅くなる可能性があります。さらに深刻なことに、システムが不安定になる可能性があります。

電圧レギュレータの周波数応答。 a 動的負荷技術のない電圧レギュレータ。 b 動的負荷技術を備えた提案された電圧レギュレータ

提案されたDLTの助けを借りて、提示されたVRは、さまざまな負荷でより優れた安定性を備えています。以前に分析したように、動的負荷回路を流れる電流は、負荷電流が定常状態で増加するにつれて減少し、逆もまた同様です。この電流はDN1によって供給されるため、より広い負荷電流範囲内でDN1の相互コンダクタンス変動を抑制できます。これは、提案されたDLTを使用することにより、より広い負荷範囲でのシステムの安定性と帯域幅の一定性に役立ちます。提案されたVRの周波数応答は図6bにあり、高速過渡応答で安定性を保証できます。

出力コンデンサはゼロの位置を設定しますω z2 。零点を適度に配置することにより、システムはさまざまな C でより優れた安定性を発揮します。 OUT 。

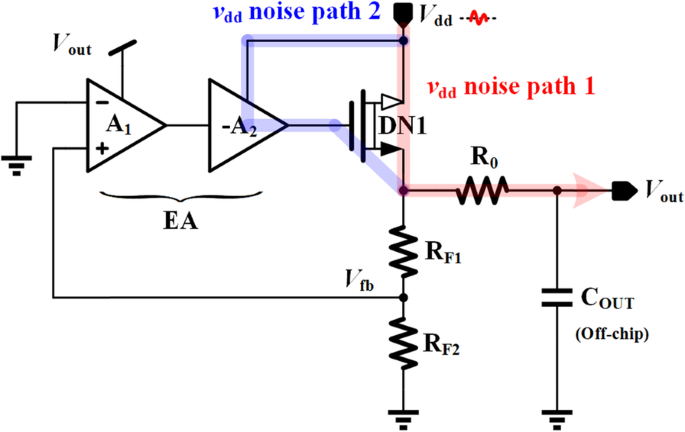

提案されたVRのPSR分析

PSRは、電圧レギュレータの性能を測定するための重要なパラメータの1つであり、電源電圧から発生する高周波リップルとノイズに対する除去能力を指します。このセクションでは、Gupta 12によって提案されたPSR分析方法を採用します。このセクションの主なアイデアは、レギュレータシステム全体を分圧器モデルに単純化することです。図7に示すように、 V からの2つのノイズパスがあります。 dd V へ out :パス1は、パワートランジスタDN1のドレインから V にノイズを直接転送します。 out ;パス2は、EAの第2ステージからパワートランジスタDN1のゲートまでです。パス2の効果は次のように表すことができます

$$ {A} _ {\ mathrm {path} 2} \ approx \ frac {r_ {o \ _M7}} {g_ {m \ _ \ mathrm {HV} 10} {r} _ {o \ _ \ mathrm { HV} 10} {r} _ {o \ _M10}} $$(15)

提案されたVRのPSR分析

(15)に示すように、 A path2 提案されたSPTとカスコードカレントミラー構造の助けを借りて非常に小さいです。これにより、PSR分析ではパス1の影響が支配的になります。

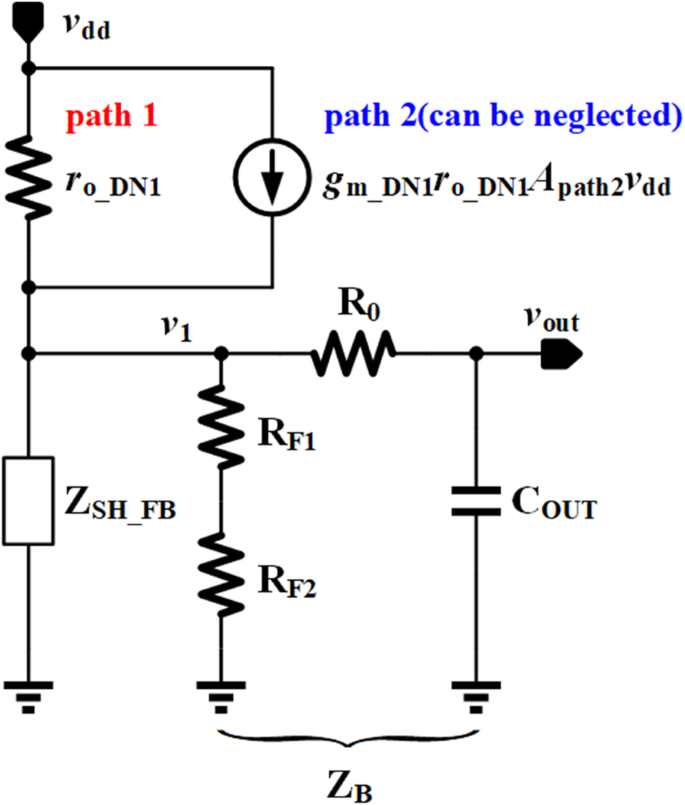

提案されたVRの簡略化されたPSRモデルを図8に示します。ここで、 r o_DN1 は、ノイズパス1を説明するパワートランジスタDN1の出力抵抗であり、制御される電流源はノイズパス2、 Z から発生します。 B R で構成されます F1 、 R F2 、 R 0 、および C OUT 高周波でフィルターとして機能し、 Z SH_FB は、負帰還ループの機能を含む等価インピーダンスです。 Z SH_FB によって与えることができます

$$ {Z} _ {SH \ _ FB} =\ frac {1} {g_ {m \ _ DN1} \ left(1+ \ beta {A} _E \ right)} $$(16)<図> <画像>

PSRの簡略化モデル

ここで g m_DN1 はパワートランジスタDN1の相互コンダクタンスです。したがって、PSR伝達関数は次のように表すことができます

$$ \ mathrm {PSR} =\ frac {V _ {\ mathrm {out}}} {V _ {\ mathrm {dd}}} =\ frac {\ left(1+ {g} _ {m \ _ \ mathrm { DN} 1} {r} _ {o \ _ \ mathrm {DN} 1} {A} _ {\ mathrm {path} 2} \ right)\ left({Z} _B \ Big \ Vert {Z} _ { \ mathrm {SH} \ _ \ mathrm {FB}} \ right)} {r_ {o \ _ \ mathrm {DN} 1} + {Z} _B \ Big \ Vert {Z} _ {\ mathrm {SH} \ _ \ mathrm {FB}}} $$(17)HV10の固有ゲインをパワートランジスタDN1よりもはるかに大きく設定することにより、 g m_DN1 r o_DN1 A path2 <<1を達成できるため、制御された電流源を無視できます。 PSRの表現は、次のようにさらに簡略化できます。

$$ \ mathrm {PSR} \ approx \ frac {Z_B \ Big \ Vert {Z} _ {\ mathrm {SH} \ _ \ mathrm {FB}}} {r_ {o \ _ \ mathrm {DN} 1} + {Z} _B \ Big \ Vert {Z} _ {\ mathrm {SH} \ _ \ mathrm {FB}}} $$(18)Z 以降 B および Z SH_FB 周波数変動により変化しますので、PSRの周波数特性を解析する必要があります。

低頻度

低周波数では、EAのゲインは非常に高く、 C OUT 開回路として扱うことができます。したがって、 Z B >> Z SH_FB PSRは次のように書くことができます

$$ {\ mathrm {PSR}} _ {\ mathrm {LF}} \ approx \ frac {1} {g_ {m \ _ \ mathrm {DN} 1} {r} _ {o \ _ \ mathrm {DN} 1} \ left(1+ \ beta {A} _ {E0} \ right)} $$(19)中頻度

Z のインピーダンス SH_FB 中周波数でループゲインが減少するため、増加します。この段階で、 Z SH_FB はまだ小さく、PSRは主にループゲインの影響を受けます。 (7)に関して、PSRは次のように表すことができます

$$ {\ mathrm {PSR}} _ {\ mathrm {MF}} \ approx \ frac {1} {g_ {m \ _ \ mathrm {DN} 1} {r} _ {o \ _ \ mathrm {DN} 1} \ left(1 + \ beta {A} _ {E0} \ right)} \ frac {1 + s / {\ omega} _p} {1 + s / \ left [{\ omega} _p \ left(1 + \ beta {A} _ {E0} \ right)\ right]} $$(20)(20)に示すように、PSRは悪化しており、ユニティゲイン周波数内で周波数が増加する一方で、出力電圧のノイズはより深刻になります。

高周波

頻度の増加により、 Z SH_FB 大きくなり、最終的に1 / g に近づきます m_DN1 。 C のインピーダンス OUT 小さくなりますが、それでも R よりはるかに大きくなります 0 。つまり、 R 0 以前のように省略できます。高周波PSRは、 r 間の分圧に依存します o_DN1 および1 / g m_DN1 C と並列 OUT 、これは

で表すことができます $$ {\ mathrm {PSR}} _ {\ mathrm {HF}} \ approx \ frac {1} {g_ {m \ _ \ mathrm {DN} 1} {r} _ {o \ _ \ mathrm {DN} 1}} \ frac {1} {1 + s {C} _ {\ mathrm {OUT}} / {g} _ {m \ _ \ mathrm {DN} 1}} $$(21)高周波では、 C の効果により、出力電圧でのノイズを大幅に抑えることができます。 OUT 。

以前に分析したように、提案されたVRの全周波数範囲での優れたアンチノイズ能力は、3つの側面によって保証されています。まず、高いループゲインが採用されています。第二に、SPTは電源ノイズがパワートランジスタのゲートにほとんど影響を与えないようにします。第三に、出力コンデンサ C OUT フィルタリング特性により、高周波でのPSRを向上させることができます。

結果と考察

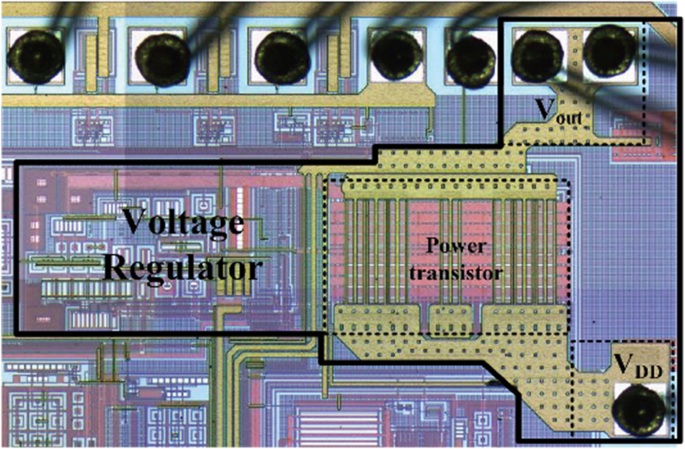

提案されたVRは、標準の0.35μmBCDテクノロジーで実装されています。作製したレギュレータのチップ写真を図9に示します。VRのアクティブコア面積は290μm×900μmです。

提案されたVRのチップ写真

提案されたVRの安定化出力電圧は5Vで、電源電圧は5.5〜30Vの範囲です。出力コンデンサは低コストのセラミックコンデンサです。出力コンデンサの静電容量は100nF〜3.3μFの範囲で設定できます。

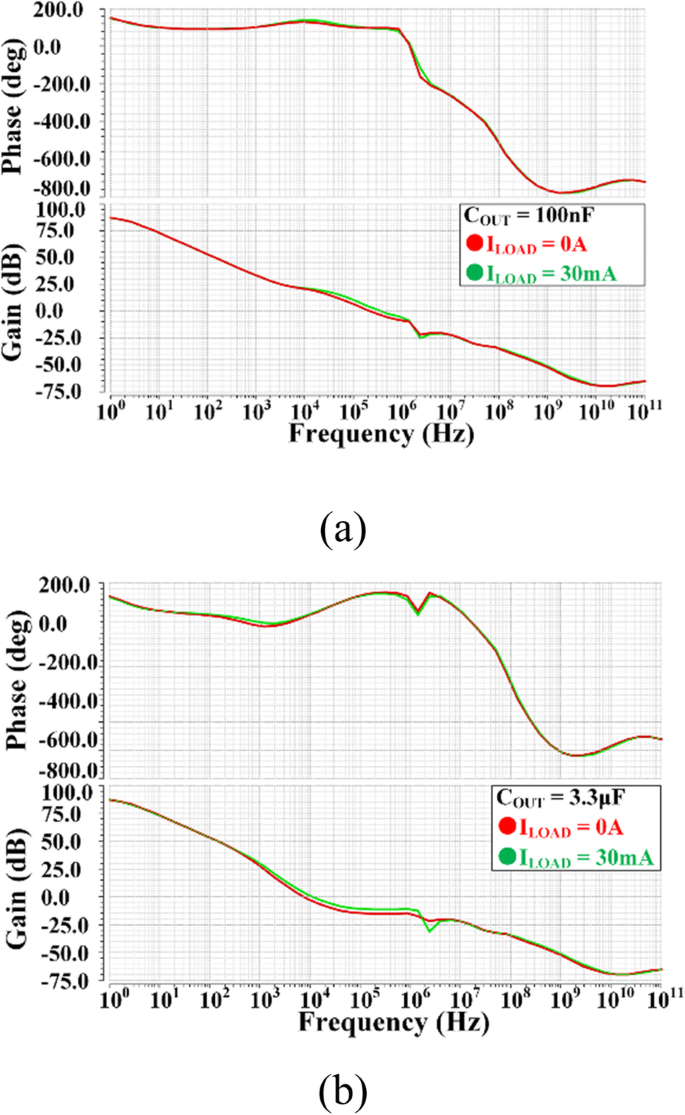

図10は、100nFおよび3.3μFの出力コンデンサを使用したさまざまな負荷条件での提案されたVRの周波数応答を示しています。提案されたLDOは、広範囲の出力コンデンサ値で安定性を維持でき、ループ周波数応答の波形は、0〜30 mAの負荷電流の差が非常に小さく、以前に分析された提案されたDLTの恩恵を受けています。

I の異なる値の下で提案されたVRのループ周波数応答 ロード および C OUT 条件。 a C OUT =100 nF、 b C OUT =3.3훍F。赤と緑の線は I を表します ロード それぞれ0Aと30mAの

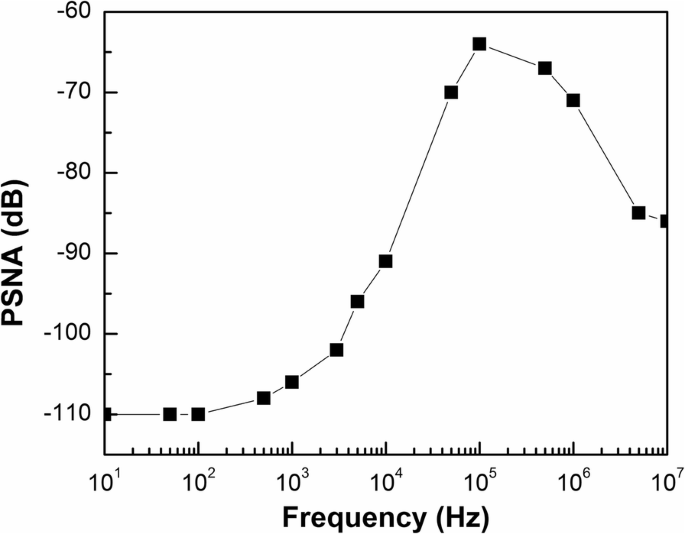

0.1μFの出力コンデンサを使用したPSR検証結果を図11に示します。ここでは、低周波数で-110 dB、最大10MHzで-64dBよりも優れています。低周波数では、提案されたVRは、ループゲインが高いため、PSRが良好です。極が支配的であるため、PSRはユニティゲイン周波数内で貧弱になりますω p 。出力コンデンサ C OUT 高周波でのPSR特性を向上させます。これらの結果は、それが以前の分析と一致しており、提案されたVRが全周波数範囲でより良いPSRを取得することを示しています。

提案されたVRのPSR

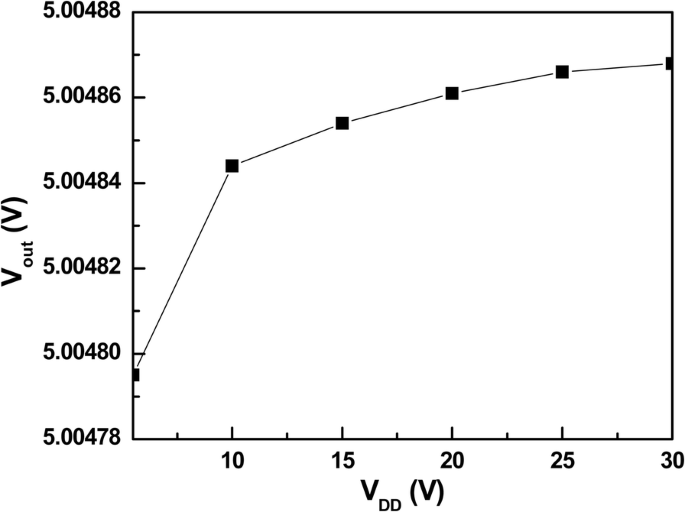

提案されたVRのラインレギュレーション結果を図12に示します。5.5〜30 Vの入力電圧範囲では、出力電圧は73.53μVしか変化せず、2.98μV/ Vのラインレギュレーションになります。これにより、提案されたSPTの有効性が確認されます。

提案されたVRのラインレギュレーション

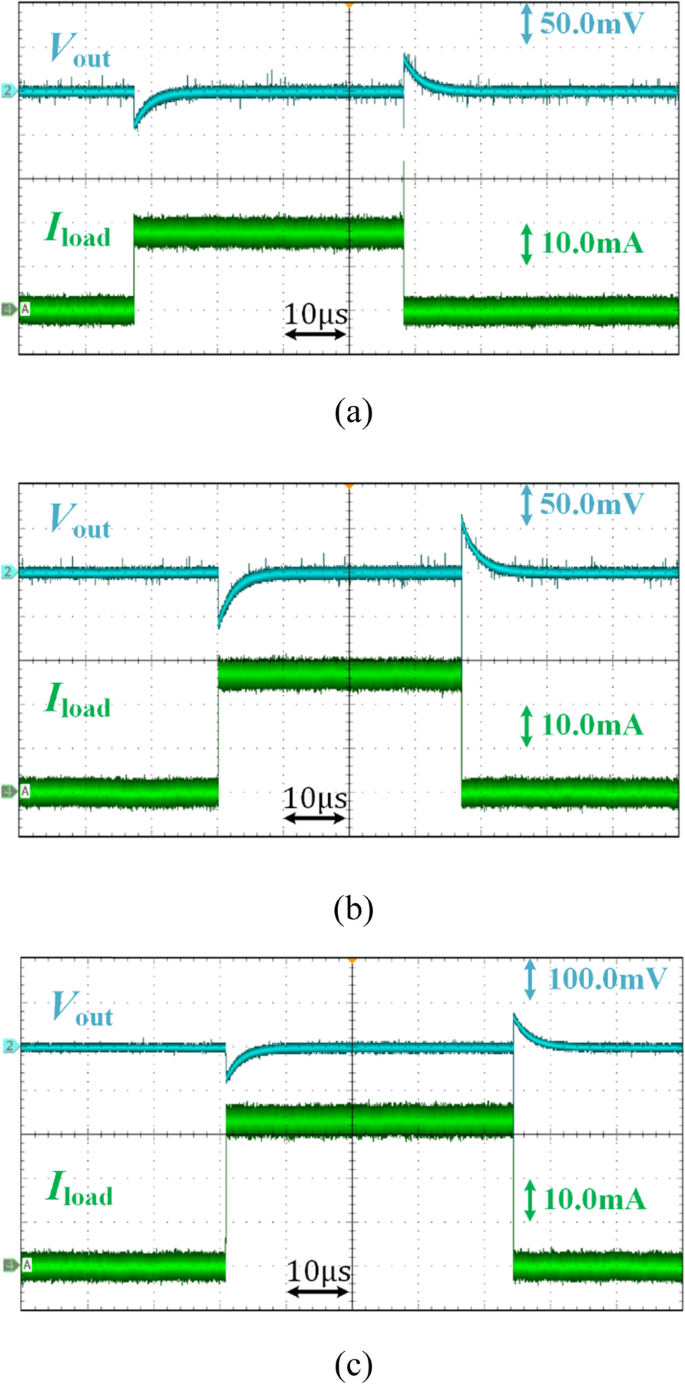

図13に、さまざまな負荷電流による出力電圧の過渡応答を示します。負荷電流が0から18mA、28 mA、32 mAに変化した場合、安定化出力電圧の電圧スパイクとディップはそれぞれ約43 mV、65 mV、83mVです。これにより、0.233 mV / mAの負荷レギュレーションが発生します。これは、主に R によって引き起こされます。 0 広範囲の出力容量での安定性のために。

異なる負荷電流ステップによる提案されたVRの過渡応答波形。 a 0〜18 mA; b 0〜28 mA; c 0〜32 mA

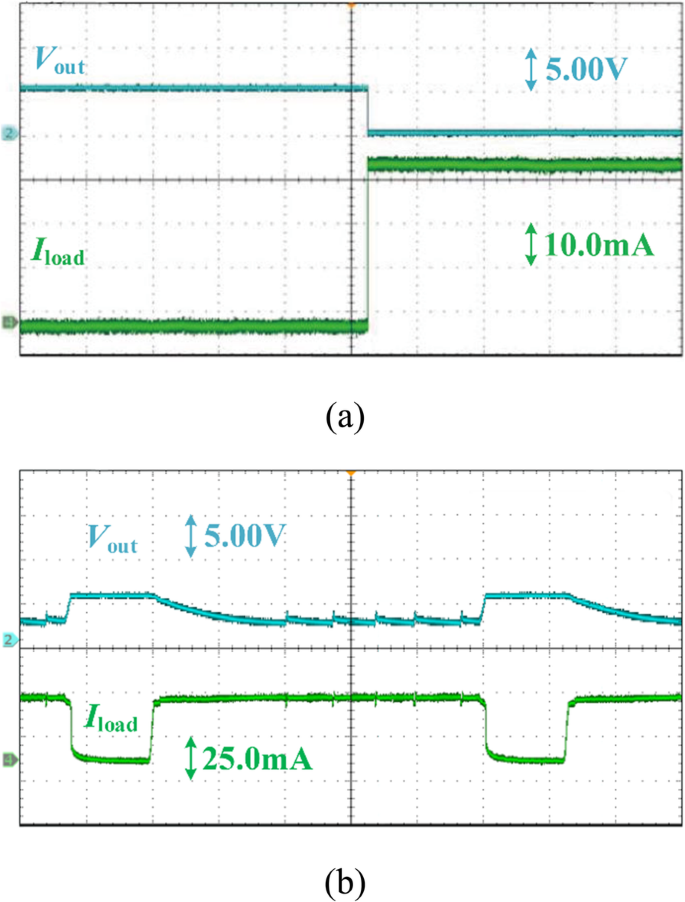

測定されたOCPを図14に示します。OCPの有効性を検証するために、図14aでは短絡が採用されています。図14aに示すように、出力電圧をグランドに引き下げて過電流が発生した場合、提案されたVRの出力電流は約40mAに維持されます。図14bは、過電流負荷と通常負荷の間の過渡応答を示しています。これは、提案されたVRが過負荷状態の終了時に自己回復する能力を備えていることを示しています。

提案されたVRのOCP測定。 a 出力短絡; b 過電流と通常の負荷の間の過渡現象

表1に、提案されたLDOと以前に公開された他のいくつかのLDOのパフォーマンス比較を示します。比較すると、このLDOは、提案されたSPTの恩恵を受ける最高のラインレギュレーションとPSRを備えています。より高度なプロセスで製造された場合、アクティブエリアはさらに減少します。

<図>表2に、電源範囲が広いLDOに焦点を当てた別のパフォーマンス比較を示します。提案されたDLTとSPTの助けを借りて、この作業は他のLDOと比較して最高のラインレギュレーションと最も広い電源範囲を持っています。追加のOCP機能により、この作業の競争力と信頼性が高まります。

<図>結論

DLTとOCPを備えた高安定SPTVRは、標準の0.35μmBCDプロセスで実装されます。 SPTの助けを借りて、ほとんどのレギュレーションループはレギュレートされた出力電圧によって供給されます。これは安定性とPSRの改善に役立ちます。提案されたDLTは、過渡応答と安定性に役立ちます。 Besides, the embedded OCP circuit can prevent the presented VR from damage by overload or short circuit. The linear regulation of the proposed VR is 2.98 μV/V with VDD from 5.5 to 30 V while the regulated output voltage is 5 V, and the load regulation is 0.233 mV/mA with load current from 0 A to 30 mA. The overshoot and undershoot voltage during load current changing is also small by using the presented transient enhancement circuit. The PSR at low frequency is − 110 dB, and is better than − 64 dB up to 10 MHz. High loop stability can be achieved in a wide range of output capacitor and load current, and thus the proposed VR is suitable for applications that require high performance and reliability under variations of output capacitor and load current.

データと資料の可用性

All data generated or analysed during this study are included in this published article.

略語

- VR:

-

Voltage regulator

- OCP:

-

Overcurrent protection

- SPT:

-

Self-power technique

- PSR:

-

Power supply rejection

- DLT:

-

Dynamic load technique

- EA:

-

Error amplifier

ナノマテリアル