モビリティの向上を実現するZrO2誘電体を備えたGeNチャネルMOSFET

要約

ZrO 2 を備えた高移動度GenMOSFET ゲート誘電体が実証され、オゾンのさまざまな界面特性を持つトランジスタと比較されます(O 3 )治療、O 3 後処理およびO 3 なし 処理。 O 3 処理、ZrO 2 を使用したGenMOSFET EOTが0.83nmの誘電体は、ピーク実効電子移動度(μ)を取得します。 eff )682 cm 2 / Vsは、中程度の反転電荷密度( Q )でのSiユニバーサル移動度よりも高くなります。 inv )。一方、O 3 Al 2 による後処理 O 3 界面層は劇的に強化された-μを提供できます eff 、約50%μを達成 eff 中程度の Q でのSiユニバーサルモビリティと比較して改善 inv 5×10 12 cm −2 。これらの結果は、ZrO 2 の潜在的な利用を示しています 高性能GenMOSFETの誘電体。

背景

ゲルマニウム(Ge)は、Siデバイスと比較して、キャリア移動度が高く、処理温度が低いという利点があります。これらにより、Geは、3次元集積回路の最上層としてのウルトラスケールCMOSロジックデバイスおよび薄膜トランジスタ(TFT)のアプリケーションの代替となります[1,2,3]。過去数年間、Ge pチャネル金属-酸化膜-半導体電界効果トランジスタ(MOSFET)の表面パッシベーション、ゲート誘電体、およびチャネルエンジニアリングに多大な努力が注がれ、電気性能の大幅な向上に貢献してきました。 pチャネルデバイス。

ただし、Ge nチャネルMOSFETの場合、実効キャリア移動度が低くなります(μ eff )ゲートスタックの不十分な界面層が原因で、デバイスのパフォーマンスが大幅に制限されます。 Siパッシベーション[1]、プラズマ後酸化[4]、InAlPパッシベーション[5]、およびHfO 2 を含むいくつかのhigh-κ誘電体を含むさまざまな表面パッシベーション技術 、ZrO 2 [6,7,8]、Y 2 O 3 [9]、およびLa 2 O 3 [10]は、電子をブーストするためにGenMOSFETで検討されていますμ eff 。 ZrO 2 Geチャネルと統合された誘電体は、GeO 2 により、堅牢なインターフェイスを提供できます。 界面層はZrO 2 と反応して混合することができます レイヤー[7]。まともな穴μ eff Ge pチャネルトランジスタ[6,7,8]で報告されていますが、電子μにはまだ改善の余地がたくさんあります。 eff 相手のために。

この作業では、ZrO 2 を備えたGenMOSFET ゲート誘電体は、改善されたμを実現するように製造されています eff 反転電荷密度の全範囲( Q inv )。 Geトランジスタは電子μを50%改善します eff 中程度の Q でのSiの普遍的な移動度と比較して inv 5.0×10 12 cm −2 。

実験的

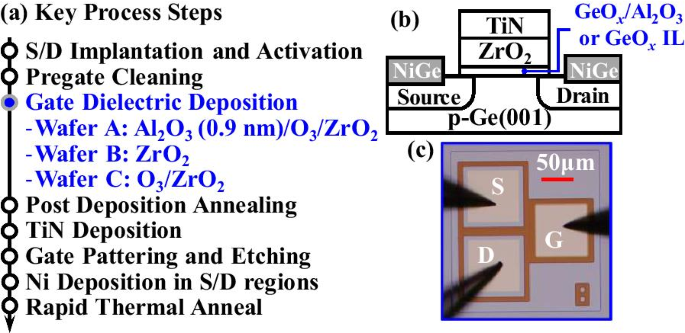

抵抗率が0.136〜0.182Ωcmの4インチp-Ge(001)ウェーハ上にGenMOSFETを製造するための主要なプロセスステップを図1aに示します。ソース/ドレイン(S / D)領域には、1×10 15 の線量でリンイオンが注入されました。 cm −2 エネルギーは30keVで、その後600°Cでドーパント活性化アニーリングを行います。ゲート前の洗浄後、Geウェーハを原子層堆積チャンバーにロードしてゲート誘電体層を形成しました:Al 2 O 3 / O 3 酸化/ ZrO 2 、ZrO 2 、またはO 3 酸化/ ZrO 2 それぞれウェーハA、B、またはCの場合。ウェーハAの場合、0.9 nm Al 2 O 3 O 3 中にチャネル表面を保護するために使用されました 酸化。 O 3 酸化は、ウェーハAとCの両方で300°Cで15分間実行されました。すべてのウェーハで、ZrO 2 の厚さ 〜3.3nmでした。続いて、TiN(100 nm)ゲート金属が物理的反応性スパッタリングによって堆積され、リソグラフィーパターニングと反応性イオンエッチングがゲート電極を形成するために使用されました。その後、25nmの厚さのNi層がS / D領域に堆積されました。最後に、350°Cで30秒間のポストメタライゼーションアニーリング(PMA)を実行して、Niゲルマニドを形成し、界面品質を改善しました。製造されたトランジスタの概略図と顕微鏡画像をそれぞれ図1b、cに示します。

a GenMOSFETを製造するための主要なプロセスステップ。 b 断面図と c 製造されたデバイスの顕微鏡画像

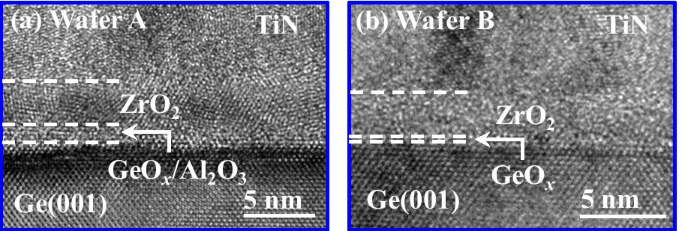

図2a、bは、それぞれウェーハAとBのゲートスタックの高分解能透過型電子顕微鏡(HRTEM)画像を示しています。 Al 2 の統一された厚さ O 3 / GeO x ウェーハAの界面層(IL)は〜1.2 nmであり、0.2〜0.3nmのGeO x を示します。 。ウェーハB上のデバイスの場合、極薄のGeO x ILは実験的に実証されました[7]。

a のHRTEM画像 TiN // ZrO 2 / Al 2 O 3 / GeO x / Ge、 b TiN / ZrO 2 / GeO x それぞれウェーハAとB上のデバイスの/ Geスタック

結果と考察

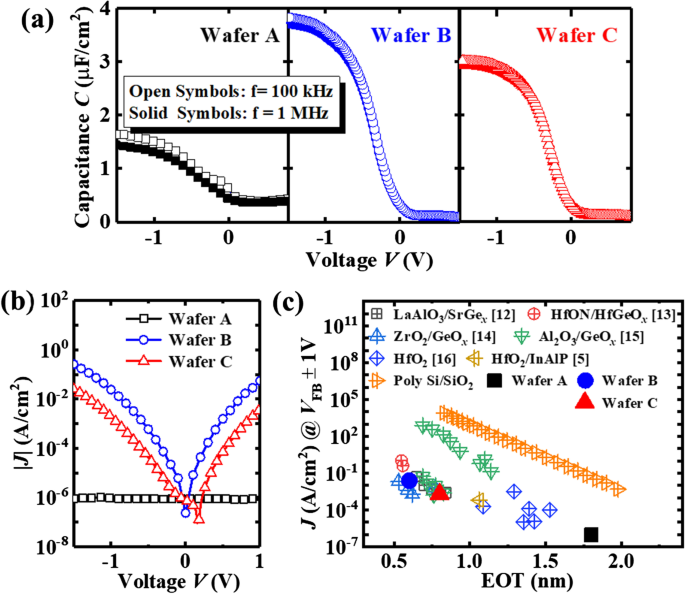

測定された静電容量( C )および漏れ電流( J )ウェーハA、B、およびC上のGe MOSコンデンサの特性が測定され、それぞれ図3a、bに示されています。ウェーハA、B、およびC上のデバイスの等価酸化物の厚さ(EOT)は、それぞれ1.79、0.59、および0.83nmと抽出されます。 GeO x を想定 ILは、ウェーハBとC、3.3 nm ZrO 2 を比較することにより、ウェーハAとCに約0.25nmの追加EOTを提供します。 EOTが〜0.6 nm、κ値が〜21.8であり、これは以前に報告されたアモルファスZrO 2 の値と一致しています。 [11]。これらの導出結果は、GeO x の厚さも確認しています。 ウェーハBのILはごくわずかです。

a 測定された C 電圧の関数として V ウェーハA、B、およびC上のGepMOSコンデンサの特性。 b J 対 V デバイスの曲線。 c J のベンチマーク ( V で抽出 FB この作品のGeMOSコンデンサの±1V)は、文献から同様のバイアス条件で得られたデータに対して機能します

GeO x / Al 2 O 3 ウェーハAおよびGeOのIL x ウェーハCのILは、それぞれ〜1.2および〜0.25nmのEOTを生成します。デバイスのEOTは、ILの厚さを薄くするか、インターフェイスの品質を向上させ、ZrO 2 の誘電率を高めることで、さらに減らすことができます。 NH 3 など、表面にパッシベーションがあります。 / H 2 プラズマ治療[6]。図3cは、 J を比較しています この作業におけるGenMOSFETのEOT特性は、他の報告されているGeデバイスの値と比較されます[5、12、13、14、15、16、17]。結果は、同じ傾向に従って超薄型EOTで報告されたGe MOSと一致していることも観察され、図3bに示すリーク電流の違いは、主にEOTの違いに起因するはずです。

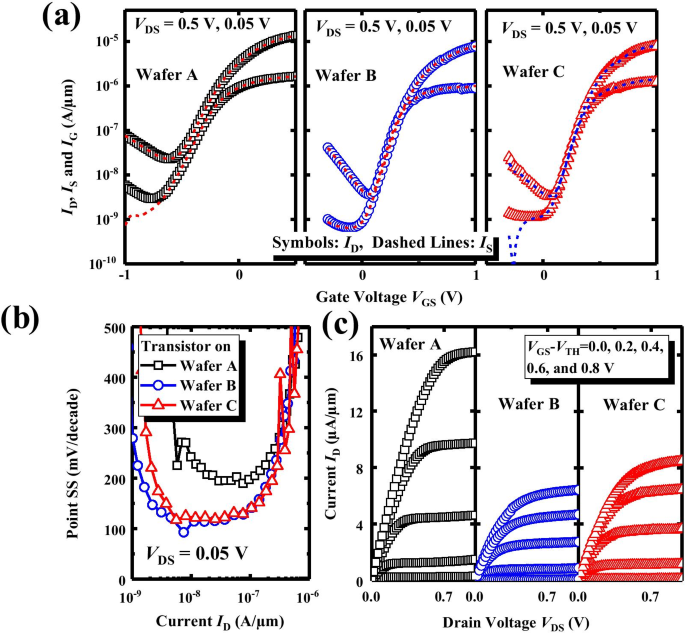

図4aは、測定されたドレイン電流( I D )およびソース電流( I S )対ゲート電圧( V G )ウェーハA、B、およびCからのGenMOSFETの曲線。すべてのトランジスタのゲート長は L です。 G 4μmのゲート幅 W 100μmの。 d V として定義されるポイントサブスレッショルドスイング(SS) G / d(log I D )、 I の関数として D 図4aのトランジスタの曲線が計算され、図4bに示されています。ウェーハA上のトランジスタが劣化した I を示すことが明らかになりました。 D ウェーハBおよびC上のデバイスと比較したリークフロアおよびSS。ウェーハA上のデバイスのEOTの増加は、SSの増加をもたらすことに加えて、これらの現象は、Al 2 O 3 挿入された層には、より高密度のインターフェーストラップがあります( D それ )ウェーハBおよびCと比較したGeチャネルのバンドギャップ内。

a 測定された I D および私 S 対 V GS ウェーハA、B、およびC上のGenMOSFETの曲線。 b I の関数としてのポイントSS D トランジスタ用。 c 私 D – V D 特性は、ウェーハA上のGenMOSFETがウェーハBおよびC上のデバイスと比較して高い駆動電流を持っていることを示しています

図4cは、測定された出力特性、つまり I を示しています。 D – V D ゲートオーバードライブのさまざまな値の曲線| V G – V TH |ウェーハA上のGeトランジスタがウェーハBおよびC上のデバイスと比較して大幅に改善された駆動電流を達成することを実証するデバイスの例。ここでは、 V TH V として定義されます GS I に対応 D の10 -7 A /μm。 S / D形成の条件が同じであることを考慮すると、ブーストされた I DS ウェーハA上のトランジスタの場合、μが高いことを示します eff [18、19、20、21]。 Al 2 O 3 層は D の劣化を引き起こしていません それ Geチャネルの伝導帯付近の性能。

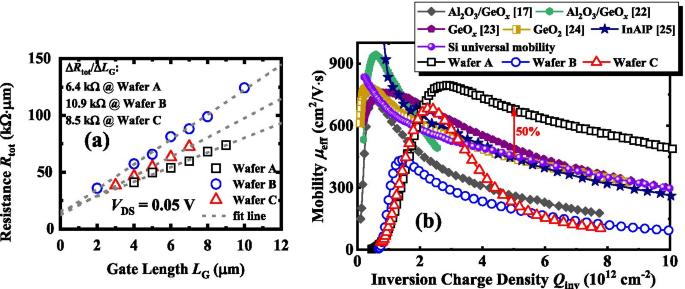

図5aは、総抵抗 R を示しています。 tot L の関数として G ZrO 2 を備えたGenMOSFETの場合 L の誘電体 G 2〜10 µmの範囲です。 R の値 tot 0.6Vおよび V のゲートオーバードライブで抽出されます D 0.05Vの。S/ D抵抗 R SD y で交差するフィッティングされた線を利用して、トランジスタの数は〜13.5kΩμmになるように抽出されます。 -軸。同様の R SD PMAとS / D形成の同じプロセスと一致しています。チャネル抵抗 R CH デバイスの値は、フィットした線の傾き、つまりΔ R によって取得されます。 tot /Δ L G 、μの計算に使用できます eff GenMOSFETの特性。インターフェイスの品質を評価するには、インターフェイストラップ密度( D それ )は、ヒルの方法[17]に従って次の方程式で抽出されました。

$$ D _ {{{\ text {it}}}} =\ frac {{2G _ {{{\ text {m}} \ max}} / \ omega}} {{qA \ left [{\ left({\ frac {{G _ {{{\ text {mmax}}}}}} {{\ omega C _ {{{\ text {ox}}}}}}} \ right)+ \ left({1 --C _ {{\ text {m}}} / C _ {{{\ text {ox}}}}} \ right)^ {2}} \ right]}} $$ここで、 q は電荷、 A はコンデンサの面積、 G m、max は測定されたコンダクタンスの最大値であり、対応する静電容量 C m 、ω は角周波数であり、 C ox ゲート酸化物の静電容量です。 D それ 値は3.7、3.2、および2.3×10 12 と計算されます eV -1 cm −2 それぞれウェーハA、B、C上のデバイス用。

計算値はミッドギャップ D に対応することが知られています それ 。 Al 2 を備えたデバイス O 3 ウェーハA上のILは、ミッドギャップが高くなります D それ ウェーハBおよびC上のデバイスと比較して。これは、図1および2の結果と一致しています。 3aと4a、およびより高いミッドギャップ D それ ウェーハAの空乏容量分散が大きくなり、 I のリーク電流が大きくなります。 DS 他の2枚のウェーハと比較して。ウェーハAの D が低いことに注意してください。 それ μが高いため、伝導バンドギャップの近く eff ウェーハBおよびC上。

a R tot 対 L G ウェーハA、B、およびC上のGe nMOSFETの曲線。y軸で交差するフィットラインと線形フィットラインの傾きを使用して、 R を抽出します。 SD および R CH 、 それぞれ。 b μ eff この作業でのGenMOSFETの場合と、以前に公開された歪みのないGeトランジスタの結果との比較。ウェーハA上のデバイスは改善されたμを示しています eff Q の全範囲でSiユニバーサルモビリティよりも inv

μはよく知られています eff は、GenMOSFETの高駆動電流と相互コンダクタンスのボトルネックです。ここで、μ eff \(\ mu _ {{{\ text {eff}}}} =1 / [WQ _ {{{\ text {inv}}}}(\ Delta R _ {{{\ text {tot}}}}で計算できます/ \ Delta L _ {{\ text {G}}})] \)、ここでΔ R tot /Δ L G R の傾きです tot 対 L G 図5aに示すように。 Q inv 測定された C を積分することで得られます inv – V G 曲線。図5bでは、μを比較しています。 eff 対 Q inv ウェーハA、B、およびC上のGe nMOSFETと、以前に[18、22、23、24、25]で報告されたものとの比較。抽出されたピークμ eff ウェーハAとCのトランジスタの値は795と682cm 2 それぞれ/ V sであり、ウェーハB上のGenMOSFETのそれは433cm 2 /Vs。 Al 2 を備えたGenMOSFET O 3 ILは大幅に改善されたμを達成します eff ウェーハBまたはCのトランジスタと比較すると、[18、22、23、24、25]のデバイスは高電界であり、 Q 全体でSiのユニバーサルモビリティがあります。 inv 範囲。 Q で inv 5×10 12 cm −2 、50%μ eff Siユニバーサルモビリティと比較して、ウェーハA上のデバイスで強化が達成されます。これは、ZrO 2 の混合を防ぐためにチャネル表面を保護することにより、 およびGeO x Al 2 を使用する O 3 、ゲート絶縁体とGeの間の高品質なインターフェースは、移動度特性を高めるために実現されます。これは、極薄EOTを備えたGeMOSFETの以前の研究でも報告されています[26]。 μ eff ウェーハC上のトランジスタのinは、 Q でのSiユニバーサルよりも高くなっています。 inv 2.5×10 12 cm −2 、 Q の増加とともに急速に減衰しますが inv 範囲。これは、使用されたO 3 ZrO 2 の前の酸化 堆積により、界面の品質がある程度向上します。ただし、高い Q でのキャリアの表面粗さ散乱を効果的に抑制するのに十分な平坦なチャネル表面にはなりません。 inv ZrO 2 の混合による およびGeO x 、 混合中に酸素空孔が発生すると、短距離秩序(SRO)の粗さが増加することが報告されているためです[27]。 O 3 の最適化 酸化プロセスまたはAl 2 の還元 O 3 ILの厚さにより、GeトランジスタのEOTを低減しながら、より高いμを維持できます。 eff 高い Q inv 。

結論

ゲート誘電体の構造と形態がGenMOSFETの電気的特性に与える影響を調査します。 Al 2 O 3 / ZrO 2 ゲート誘電体は大幅に改善されたμを提供します eff Siユニバーサルモビリティと比較して。 μ eff Al 2 を挿入することで改善できます O 3 ZrO 2 間のレイヤー Geチャネル。ただし、必然的にEOTが大きくなります。 Al 2 O 3 -O 3 を備えた無料のGenMOSFET ZrO 2 の前のGe表面の酸化 堆積はピークμを達成します eff 682 cm 2 同様の Q でSiよりも高い/ V inv 。

データと資料の可用性

この記事の結論を裏付けるデータセットは、記事に含まれています。

略語

- Ge:

-

ゲルマニウム

- ZrO 2 :

-

二酸化ジルコニウム

- Al 2 O 3 :

-

酸化アルミニウム

- O 3 :

-

オゾン

- Si:

-

シリコン

- PMA:

-

ポストメタルアニーリング

- PDA:

-

堆積後のアニーリング

- IL:

-

界面層

- TiN:

-

窒化チタン

- MOSFET:

-

金属-酸化物-半導体電界効果トランジスタ

- ALD:

-

原子層堆積

- HF:

-

フッ化水素酸

- µ eff :

-

効果的なキャリアモビリティ

- PPO:

-

プラズマ後酸化

- SS:

-

サブスレッショルドスイング

- CET:

-

静電容量相当の厚さ

- EOT:

-

等価酸化物の厚さ

- Qinv:

-

反転電荷密度

- HRTEM:

-

高分解能透過型電子顕微鏡

- Ni:

-

ニッケル

- GeO x :

-

酸化ゲルマニウム

- I DS :

-

電流を排出する

- V GS :

-

ゲート電圧

- V TH :

-

しきい値電圧

ナノマテリアル

- 染料と顔料で持続可能性を達成する

- KUHMUTEはSLS3D印刷でモビリティを再設計します

- 誘電体メタ表面を介した帯域幅の拡大による完全なテラヘルツ分極制御

- コンプライアンスフリーのZrO2 / ZrO2 − x / ZrO2抵抗変化型メモリと制御可能な界面マルチステートスイッチング動作

- 窒化処理を施したHfO2ベースのRRAMの伝導メカニズムと耐久性の向上

- マイクロ波アニーリングによる原子層堆積Al2O3 / ZrO2 / Al2O3MIMコンデンサの誘電増強

- アモルファスSiパッシベーションを備えた高移動度GepMOSFET:表面配向の影響

- 水素に富むAl2O3誘電体を使用することにより、サーマルバジェットが非常に低い高性能a-InGaZnO薄膜トランジスタ

- リリース4.6でProtocaseDesignerを改善した6つの方法

- 金属化による驚異的な仕上がりの実現

- 銅タングステン電極で耐摩耗性を向上