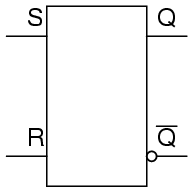

S-Rラッチ

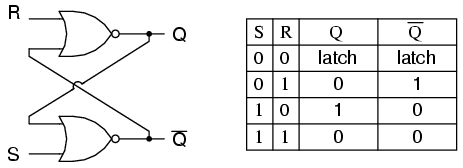

双安定マルチバイブレータには 2つあります 接頭辞 bi で示される安定状態 その名前で。通常、1つの状態は set と呼ばれます もう1つはリセット 。したがって、最も単純な双安定デバイスは、 set-reset として知られています。 、またはS-R、ラッチ。 S-Rラッチを作成するには、次のように、一方の出力がもう一方の入力にフィードバックするように、またはその逆になるように2つのNORゲートを配線できます。

Q出力とnot-Q出力は反対の状態にあると想定されています。 S入力とR入力の両方を1に等しくすると、Qと非Qの両方が0になるため、「想定」と言います。このため、SとRの両方を1に等しくすると、無効> または違法 S-Rマルチバイブレータの状態。

それ以外の場合、S =1およびR =0にすると、マルチバイブレータが「設定」され、Q =1およびQ =0ではなくなります。逆に、R =1およびS =0にすると、マルチバイブレータが反対の状態に「リセット」されます。 SとRの両方が0に等しい場合、マルチバイブレータの出力は以前の状態で「ラッチ」します。

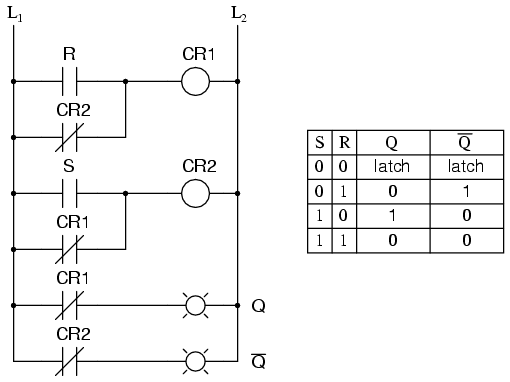

同じマルチバイブレータ関数をラダーロジックに実装して、同じ結果を得る方法に注意してください。

定義上、Q =1でQ =0ではない条件が設定されます。 。 Q =0でQ =1ではない条件はリセットです 。これらの用語は、マルチバイブレータ回路の出力状態を説明する上で普遍的です。鋭敏な観察者は、S-Rラッチのゲートまたはラダーのいずれかの初期電源投入状態が、両方のゲート(コイル)が非通電モードで開始するようなものであることに気付くでしょう。

そのため、Q出力と非Q出力の両方が同じ状態で、回路が無効な状態で起動することが予想されます。実際、これは本当です!ただし、無効な状態はS入力とR入力の両方が非アクティブで不安定であり、一方のゲート(またはリレー)がもう一方のゲートよりも少し速く反応するようにバインドされているため、回路はセット状態またはリセット状態のいずれかですぐに安定します。

両方のゲート(またはコイル)が正確に同一である場合 、電源投入時に安定点に達することなく、非安定マルチバイブレータのように高低の間で振動します。幸いなことに、このような場合、コンポーネントがこのように正確に一致する可能性はほとんどありません。

不安定な(継続的に発振する)状態は非常にまれですが、上記の回路では1〜2サイクルの発振が発生する可能性が高く、電源投入後の回路の最終状態(セットまたはリセット)に注意する必要があります。予測できないでしょう。

問題の根本は競合状態です 2つのリレー間CR 1 およびCR 2 。

競合状態は、2つの相互に排他的なイベントが、単一の原因によって異なる回路要素を介して同時に開始された場合に発生します。この場合、回路要素はリレーCR 1 です。 およびCR 2 、およびそれらの非通電状態は、通常は閉じているインターロック接点のために相互に排他的です。

一方のリレーコイルがオフになっている場合、その通常閉接点はもう一方のコイルにオンを維持し、回路を2つの状態(セットまたはリセット)のいずれかに維持します。インターロックは両方を防ぎます ラッチからリレーします。

ただし、両方の場合 リレーコイルは、電源がオフの状態で起動します(回路全体の電源がオフになってから電源が投入された後など)。両方のリレーは、他のリレーの通常閉接点。これらのリレーの1つは、必然的に他のリレーよりも先にその状態に達するため、通常は閉じているインターロック接点が開き、他のリレーコイルの電源が切れます。

どのリレーがこのレースに「勝つ」かは、回路設計ではなくリレーの物理的特性に依存するため、設計者は電源投入後に回路がどの状態になるかを確認できません。回路設計では、主に作成される予測不可能性のために、競合状態を回避する必要があります。このような状態を回避する1つの方法は、時間遅延リレーを回路に挿入して、競合するリレーの1つを短時間無効にし、もう1つに明らかな利点を与えることです。

つまり、一方のリレーの電源を切る速度を意図的に遅くすることで、もう一方のリレーが常に「勝ち」、レース結果が常に予測可能になるようにします。

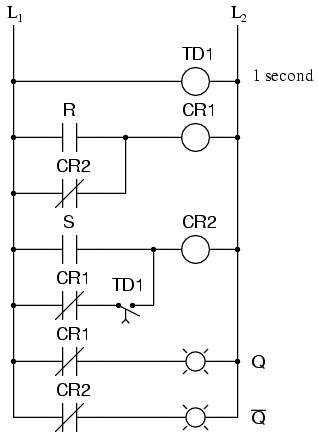

競合状態を回避するために、上記の回路に時間遅延リレーを適用する方法の例を次に示します。

回路の電源が入ると、時間遅延リレー接点TD 1 5番目のラングダウンでは、閉じるのが1秒間遅れます。その接点を1秒間開いたままにすると、リレーCR 2 が防止されます。 接点CR 1 を介した通電から 電源投入後、通常は閉じた状態です。

したがって、リレーCR 1 最初に通電することが許可され(1秒のヘッドスタートで)、通常は閉じているCR 1 が開きます。 5番目のラングで接触し、CR 2 を防ぎます S入力がアクティブになることなく通電されないようにします。

最終結果は、回路がS =0およびR =0のリセット状態でクリーンかつ予測可能にパワーアップすることです。競合状態はリレー回路に限定されないことに注意してください。ソリッドステート論理ゲート回路も、不適切に設計された場合、競合状態の悪影響を受ける可能性があります。

複雑なコンピュータプログラムは、不適切に設計された場合、人種問題を引き起こす可能性があります。レースの問題は、どのシーケンシャルシステムでも発生する可能性があり、システムの最初のテスト後しばらくしてから発見される可能性があります。それらは、検出して排除するのが非常に難しい問題になる可能性があります。

S-Rラッチ回路の実際の用途は、両方の始動に通常開の瞬間的な押しボタンスイッチ接点を使用して、モーターを始動および停止することです。 (S)と停止 (R)スイッチ、次にCR 1 のいずれかでモーター接触器に通電します またはCR 2 連絡先(またはCR 1 の代わりにコンタクタを使用) またはCR 2 。

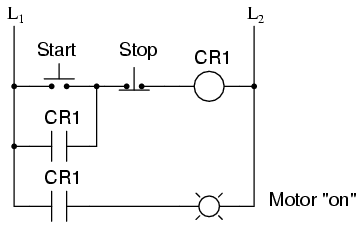

通常、次のようなはるかに単純なラダーロジック回路が使用されます。

上記のモーター始動/停止回路では、CR 1 start と並行して連絡する スイッチ接点は、制御リレーCR 1 を「シール」またはラッチするため、「シールイン」接点と呼ばれます。 開始後の通電状態 スイッチがリリースされました。

「シール」を解除する、または回路を「ラッチ解除」または「リセット」するには、停止 押しボタンが押されると、CR 1 がオフになります シールイン接点を通常開状態に戻します。ただし、この回路はS-Rラッチとほぼ同じ機能を実行することに注意してください。

また、この回路には、ダブルリレーS-Rラッチ設計のように、固有の不安定性の問題がないことに注意してください(リモートの可能性がある場合でも)。半導体形式では、S-Rラッチはあらかじめパッケージ化されたユニットで提供されるため、個々のゲートからラッチを構築する必要はありません。それらはそのように象徴されています:

レビュー:

- 双安定 マルチバイブレータは 2つの1つです 安定した出力状態。

- 双安定マルチバイブレータでは、Q =1およびnot-Q =0の条件は set として定義されます。 。逆に、Q =0でQ =1でない条件は、リセットとして定義されます。 。 Qとnot-Qがたまたま同じ状態(両方0または両方1)に強制された場合、その状態は無効と呼ばれます。 。

- S-Rラッチでは、S入力をアクティブにすると回路が設定され、R入力をアクティブにすると回路がリセットされます。 S入力とR入力の両方が同時にアクティブになると、回路は無効な状態になります。

- 競合状態 は、2つの相互に排他的なイベントが単一の原因によって同時に開始されるシーケンシャルシステムの状態です。

産業技術