J111 JFET:ピン配置、機能、アプリケーション、およびその他の重要な知識の説明

ジャンクション電界効果トランジスタ (JFET) は、入力電圧を使用して出力特性を制御 (電圧制御) する半導体デバイスです。さらに、電流を流す際に正孔または電子 (キャリア) を適用する 3 つの端子があります。 JFET のタイプの 1 つに J111 があり、これが今日の主な焦点となります。そのため、そのピン構成、機能、アプリケーションについて説明し、次に JFET の動作原理の概要を説明します。

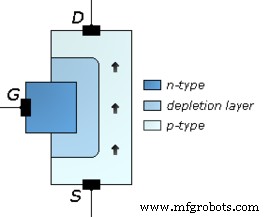

P チャネル JFET

j111 JFET ピン構成

J111 JFET のピン配列には 3 つのピンがあります。それらは、ゲート、ドレイン、およびソースピンで構成されています。

J111 n チャネル JFET の記号

- ピン 1/ ドレイン端子 - チップに電流が流れるようにします。

- ピン 2/ ソース端子 – JFET バイアスを制御します。

- Pin3/ ゲート端子 – GND に接続され、チップからの電流の出力です。

TO-92 パッケージの J111

機能

J111 JFET の機能と最大定格は次のとおりです。

注; 最大定格は、j111 が耐えることができる損傷の量を決定する個々のストレス限界値です。

- 高入力インピーダンスのインターネット N0132S 形状です。

- そして、それは RoHS に準拠しています。

- 動作および保存接合部温度範囲は -65°C ~ +150°C ですが、リード温度は 300°C です。

- また、高電力ゲイン – 1.5mS (標準)、低ノイズ – 1.2 nV/√Hz (標準) を備えています。

- 消費電力は約 625mW です。

- さらに、最大ゲート-ソース電圧と最大ドレイン ゲート電圧はいずれも 35 V です。

- 最後に、TH (スルーホール パッケージ)、ベア ダイ、および SMT パッケージ オプションで利用できます。また、パッケージ タイプの TO-92 ピン数と表面実装 SOT-23 パッケージも含まれています。

JFET の仕組み

JFET がどのように機能するかを説明するために、2 つの作業シナリオを使用します。

最初のケース

JFET の動作に関する最初の回路図

ゲート電圧なしで、ソース端子とドレイン端子の間に電圧 VDS を印加することから始めます。その結果、バーの側面にある 2 つの p-n 接合によって確立された空乏層が得られます。

すると、空乏層の間に形成されたチャネルを介して、ソース端子からドレイン端子への電子の流れが始まります。

注; 空乏層のサイズは、バーを介して伝導される電流とチャネル幅を決定します。

2 番目のケース

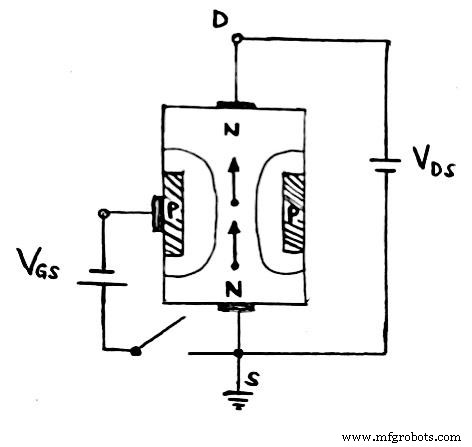

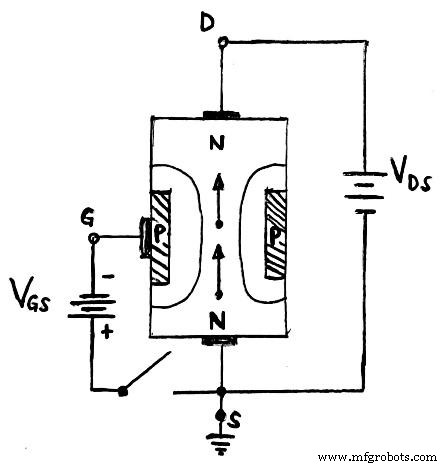

JFET の仕組みの 2 番目の図

ここでは、逆に作業します。したがって、ソース端子とゲート端子の間に VGS 電圧を印加します。供給により、空乏層の幅が広がります。

その後、導電チャネルは n バーの抵抗を増加させるよりも減少させ、したがってソースからドレインへの電流を減少させます。

逆に、ゲートの逆バイアスを小さくすると、空乏層の幅が狭くなります。その後、ソースからドレインへの電流は、導電チャネルの幅が増加するために上昇します。

n チャネルと p チャネルの JFET は同様の動作をすることに注意してください。唯一の違いは、p チャネル JFET はチャネル電流のキャリアとして電子ではなく正孔を使用することです。さらに、VGS と VDS の極性が逆になっています。

J111 と同等

J111 N チャネル JFET の同等品または代替品として、J107 を検討できます。低ノイズの JFET アンプとして動作する費用対効果の高いスイッチです。

(電子JFET)

- JFET と BJT の違い

バイポーラ接合トランジスタと JFET には、表のとおりの違いがあります。

| JFET | BJT |

| JFET は 1 つのキャリア タイプ、つまり、n 型チャネルの電子と p 型チャネルの正孔を持つため、ユニポーラ トランジスタです。 | 正孔と電子の両方が伝導を助けるため、バイポーラ トランジスタです。 |

| その入力回路には逆バイアスがかかっているため、入力インピーダンスが高くなります。 | 入力回路の順方向バイアスにより、入力インピーダンスが低くなります。 |

| ジャンクションがないため、騒音レベルが低い。 | ジャンクションが存在すると、ノイズレベルが増加します。 |

| ゲート端子電圧を使用して、ソースとドレイン間の電流を調整します。 | ベース電流を使用して、エミッタとコレクタ間の風を制御します。 |

| ここで、ゲート端子には電流が流れません。 | 一方、BJT は数 µA のベース電流を受け取ります。 |