シグナル インテグリティに関する高速 PCB 設計の課題とその解決策

電子技術の絶え間ない進歩、デジタル システムのクロックの高周波化、ますます短い立ち上がりエッジ時間により、PCB システムは高性能のシステム構造になり、コンポーネントをサポートする単なるプラットフォームをはるかに超えています。電気的性能の観点からは、高速信号間の相互接続はもはや迅速でも透過的でもなく、リード間の相互接続が高速 PCB およびボード プレーンの特性に及ぼす影響は、もはや無視できません。反射、クロストーク、遅延、通話、高速信号相互接続によって引き起こされるインピーダンス マッチングなどのシグナル インテグリティの問題にうまく対処し、信号伝送の品質が設計の成功を左右することを保証します。

PCB シグナル インテグリティの基本理論

• 高速回線とその判定原理

高速回路の定義用語には、主に 2 つのバージョンがあります。一方、ある回路において、伝送線路上のデジタル信号の遅延が立ち上がりエッジ時間の 20% 以上の場合、この回路は高速回路と見なすことができます。一方、ある回路においてデジタルアナロジー回路の周波数が45MHzから50MHz以上の場合、その回路は高速回路とみなされます。

基本的に、L(リードの長さ)がTr以上の場合 、回路は高速回路と見なされます。 L が Tr より小さい場合 、回線は低速回線と見なされます。ここで、Tr パルスの立ち上がりエッジ時間を指します。

• 信号伝送速度とパルス立ち上がり時間

空気中の信号の伝送速度は 3 x 10

8

です。 MS; PCBの材料であるFR4の誘電率はεrで表示されます。 つまり 4. PCB の信号伝送速度は、式を使用して計算できます。  .

.

Vp は 15cm/ns に等しく、約 6 インチ/ns です。パルス立ち上がり時間 Tr =1/(10 x fclk ) であり、100MHz 信号の立ち上がり時間は 1ns です。 PCB 配線上の信号の遅延が立ち上がりエッジ時間の 20% を超える場合、信号で明らかな呼び出しが行われます。立ち上がり時間が1ns(100MHz)の方形波の場合、PCBの配線長が0.2ns×6=1.2インチ以上になると信号に重大な呼び出しが発生します。したがって、臨界長は 1.2 インチ (約 3 cm) です。

• 特性インピーダンス

特性インピーダンスは、反射、コーリング、アッパー シュート、アンダー シュートに影響を与えるインピーダンス マッチングの重要なパラメータであり、高速信号伝送の完全性に直接関係します。これは、高速設計において非常に重要です。

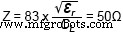

信号は伝送線路に沿って伝送され、電圧と電流の比率が過渡インピーダンスと見なされます。送電線の過渡インピーダンスは、次の式で計算されます。  .この式では、Cl 単位長さあたりの容量で、単位は pF/inch (通常は 3.3pF/inch) です。伝送線路に沿った過渡インピーダンスが一定値の場合、この値は伝送線路の特性インピーダンスと見なされます。 PCB 上のマイクロストリップ ラインとストリップ ラインの特性インピーダンスは、図 1 に示すように、伝送線路設計ツール Polar Si9000 で計算できます。

.この式では、Cl 単位長さあたりの容量で、単位は pF/inch (通常は 3.3pF/inch) です。伝送線路に沿った過渡インピーダンスが一定値の場合、この値は伝送線路の特性インピーダンスと見なされます。 PCB 上のマイクロストリップ ラインとストリップ ラインの特性インピーダンスは、図 1 に示すように、伝送線路設計ツール Polar Si9000 で計算できます。

シグナル インテグリティに影響を与える要素とソリューション

•インピーダンスマッチング

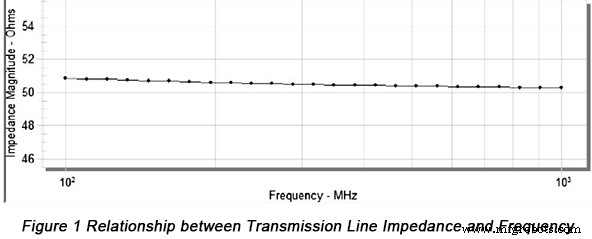

高速回路設計では、高速で正確なデータ伝送を保証するためにインピーダンス整合が必要です。データ蓄積システムは、図2に示すように、センサー、シグナルコンディショニング機器、ADデータ蓄積チップ、FPGA、SDRAMで一般的に構成されています。

AD9649 は、1.8V 電源と 14 ビット データ ラインによるパラレル サンプルを備えた AD チップとして適用されます。サンプルの頻度は 20M に設定されています。 PCIインターフェースチップとしてPCI9054を採用し、DMAデータ転送に対応。 PCI構成のチップとして93LC66Bをピックアップ。 HY57V561620FTP-H は、データ ストレージとして適用され、それぞれが 4M x 16 ビットのメモリ空間を持つ 4 つの BANK で構成され、13 列のアドレス ラインと 9 列のアドレス ラインがあります。 EP1C6F256C8 は、3.3V の終端電圧と 1.5V のコア電圧で FPGA によって選択されます。 PCI バスの幅は 32 ビットで、書き込みおよび読み取りクロックとして 33MHz のクロックがピックアップされ、配線および読み取りの最大速度は毎秒 132MByte に達し、蓄積されたデータの高速転送をサポートできます。

PCB の設計プロセスでは、次の要素を考慮する必要があります。

を。デジタルとアナログの混合部分として、AD は PCB 設計の重要なポイントの 1 つです。デジタル部分の周波数が高いため、アナログ部分は干渉に非常に敏感です。適切な処理が実装されていない場合、デジタル信号がアナログ信号に干渉する傾向があり、EMI 問題が発生します。設計者が従うべき正しい原則は次のとおりです。まず、デジタル グランドとアナログ グランドは PCB 上で信号が混在するように分割する必要があります。第二に、アナログおよびデジタル電子部品は、アナログ領域に分散されたアナログ接地とデジタル領域に分散されたデジタル接地に分類されます。 3 番目に、アナログ グラウンドとデジタル グラウンドは、領域セグメンテーションの周囲の磁気ビーズで接続されます。これらの対策により、デジタル グランドとアナログ グランドを分離することができます。

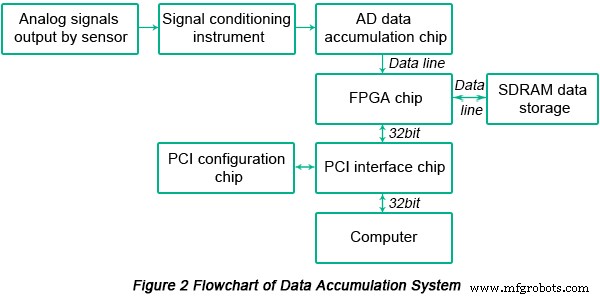

b. SDRAM はデータ蓄積システムに適用され、図 3 に示すように、FPGA に接続されるデータ ラインは、高速伝送を保証するために 50Ω のインピーダンス マッチングで構成する必要があることがマニュアルに明確に示されています。

FPGA が蓄積されたデータを SDRAM に書き込んだ後、データを維持するために常にリフレッシュを実行する必要があり、各行のリフレッシュ周期は 64 ミリ秒より速くなければなりません。

Polar Si9000 ソフトウェアによるインピーダンス マッチングの手順は、次のように表示されます。

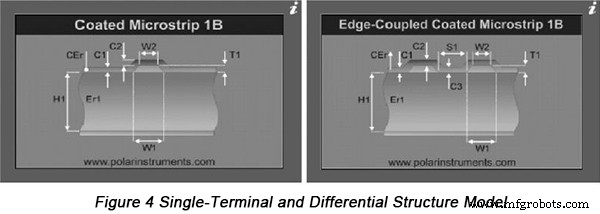

を。高速信号ラインは PCB の上面を横切り、穴はできるだけ避けてください。図 4 に示すように、マイクロストリップ ライン構造モデルがソフトウェアに取り込まれます。

50Ωのインピーダンス整合は通常、単一端子配線で行われ、90Ωのインピーダンス整合は通常、差動配線 (USB2.0 D+、D-など) で行われます。

b.必要なインピーダンス マッチング値と PCB 製造技術の特定の値は、誘電体の厚さ、PCB 材料の誘電率、銅箔の厚さ、グリーン オイルの厚さ、グリーン オイルの誘電率などのパラメータを使用してソフトウェア インターフェイスに入力されます。

| アイテム | 説明 | 参考値と計算値 |

| H1 | 誘電体の厚さ (PP またはボード素材) | 3.5 ~ 8.5mil |

| Er1 | ボード素材の誘電率 | 4-4.6 |

| W1 | 信号配線幅 | インピーダンス値に基づく |

| C1 | 基板材料の緑色のイオンの厚さ | 0.8mil |

| C2 | 銅上のグリーン オイルの厚さ | 0.5mil |

| CEr | グリーンオイルの誘電率 | 3.3 |

| ゾ | 一致させるインピーダンス値 | シングル端子:50Ω 差動:90Ω |

製造技術の特定のパラメーターは、PCB メーカーとのコミュニケーションを通じて知ることができるため、リードの幅を把握することができます。差動マイクロストリップ ラインの場合、リード間の距離 (S1) も計算する必要があります。

c.計算されたリードの幅が比較的大きく、PCB ルーティングが完了しない場合は、PCB メーカーとより多くのコミュニケーションを取り、設計要件を満たす製造技術のパラメーターを調整する必要があります。

•クロストーク

クロストークとは、信号が伝送ライン上を伝送されているときに、電磁結合の結果として、隣接する伝送ラインで予期しない電圧ノイズ干渉が発生することを指します。クロストークが多すぎると、回路が誤ってトリガーされ、システムが正常に機能しなくなる可能性があります。クロストークは電磁結合によって発生し、結合は容量結合と誘導結合に分けられます。前者は実際には干渉源での電圧変化の結果として引き起こされる誘導電流によって引き起こされる電磁干渉であり、後者は実際には干渉源での電流変化の結果として引き起こされる誘導電圧によって引き起こされる電磁干渉です。干渉源の状態が変化すると、一連の干渉パルスが干渉対象で生成されます。これは、高速システムでは非常に一般的です。

クロストークへの対策は以下のように表示されます。

a.直交性は、隣接するプレーン間の配線方向に維持する必要があります。クロストークを減らすために、信号線が異なる隣接するプレーンで同じ方向を避ける必要があります。特に信号速度率が比較的高い場合は、グランドを考慮して配線プレーンを分離し、信号線をグランド信号線で分離する必要があります。

b.ライン間のクロストークを減らすには、ライン間の間隔を十分大きくする必要があります。

c.線の中心間距離が線幅の3倍以上あれば相互干渉により電界の70%を遮断することができ、これが3W原理である。高速信号ラインが要件を満たしている状況では、結合端子にマッチングを利用して、反射を低減または除去し、クロストークを低減できます。

シグナル インテグリティ設計法の応用

PCB 設計のプロセスでは、シグナル インテグリティ理論に基づいて多くの設計ルールがまとめられています。これらの PCB デザイン ルールを参照することで、シグナル インテグリティを向上させることができます。 PCB 設計のプロセスでは、次のような設計情報を詳細に把握する必要があります。

a.

b.部品の配置位置、チップ部品の電力や熱放散が大きい部品に特別な要件があるかどうか。

c.信号の分類、速度、伝送方向、インピーダンス整合要件。

d.信号駆動能力、キー信号及び保護対策。

電源の種類、グランド、電源とグランドのノイズ制限要求、電源プレーンとグランドプレーンの設定と分割。クロック ラインのタイプと速度、クロック ラインのソース、方向、クロックの遅延要件、および最大配線要件。

参考資料:

• PCB高速信号回路設計における3つの配線テクニック

• 高速PCBレイアウトにおける信号反射の抑制方法

• 高速PCBレイアウトにおけるシグナルインテグリティ解析とPCB設計デジタル-アナログ混合回路

• ビアのインピーダンス制御と PCB 設計におけるシグナル インテグリティへの影響

• PCBCart のフル機能 PCB 製造サービス - 複数の付加価値オプション

• 高度な PCB アセンブリ サービスPCBCart から - 1 個から開始

産業技術