論理信号電圧レベル

論理ゲートの入力電圧

論理ゲート回路は、可変電圧で表される「高」(1)と「低」(0)の2種類の信号のみを入出力するように設計されています。「高」状態の場合は全電源電圧、 「低」状態。完璧な世界では、すべての論理回路信号はこれらの極端な電圧限界に存在し、それらから逸脱することはありません(つまり、「高」の場合は全電圧未満、「低」の場合はゼロより高い電圧)。

ただし、実際には、トランジスタ回路の漂遊電圧降下により、論理信号電圧レベルがこれらの完全な制限に達することはめったにありません。したがって、ゲート回路が の間にある信号電圧を解釈しようとするときに、ゲート回路の信号レベル制限を理解する必要があります。 / em> 完全な供給電圧とゼロ。

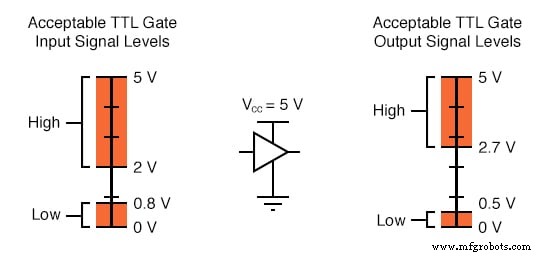

TTLゲート入力の耐電圧

TTLゲートは、5ボルト、+ /-0.25ボルトの公称電源電圧で動作します。理想的には、TTLの「高」信号は正確に5.00ボルトであり、TTLの「低」信号は正確に0.00ボルトです。

ただし、実際のTTLゲート回路は、このような完全な電圧レベルを出力することはできず、これらの理想値から大幅に逸脱する「高」および「低」信号を受け入れるように設計されています。

「許容可能な」入力信号電圧の範囲は、「低」論理状態の場合は0ボルトから0.8ボルト、「高」論理状態の場合は2ボルトから5ボルトです。

「許容可能な」出力信号電圧(指定された負荷条件の範囲でゲートメーカーによって保証された電圧レベル)は、「低」論理状態の場合は0ボルトから0.5ボルト、「高」論理状態の場合は2.7ボルトから5ボルトの範囲です。 :

0.8ボルトから2ボルトの範囲の電圧信号がTTLゲートの入力に送信された場合、ゲートからの特定の応答はありません。このような信号は不確実と見なされます 、および論理ゲートの製造元は、ゲート回路がそのような信号をどのように解釈するかを保証しません。

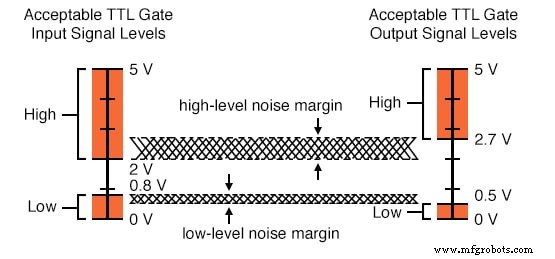

TTLノイズマージン

ご覧のとおり、出力信号レベルの許容範囲は入力信号レベルよりも狭く、デジタル信号を別のTTLゲートの入力に出力するTTLゲートが、受信ゲートに許容できる電圧を送信するようになっています。許容可能な出力範囲と入力範囲の違いは、ノイズマージンと呼ばれます。 門の。

TTLゲートの場合、低レベルのノイズマージンは0.8ボルトと0.5ボルト(0.3ボルト)の差であり、高レベルのノイズマージンは2.7ボルトと2ボルト(0.7ボルト)の差です。簡単に言えば、ノイズマージンは、受信ゲートが誤って解釈する前に、弱いゲート出力電圧信号に重畳される可能性のあるスプリアスまたは「ノイズ」電圧のピーク量です。

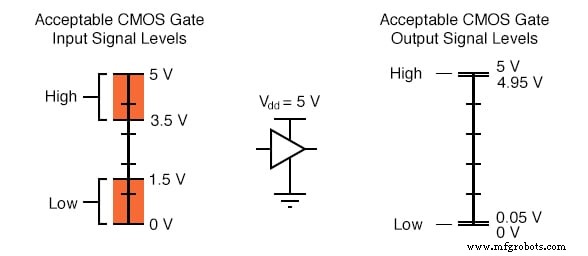

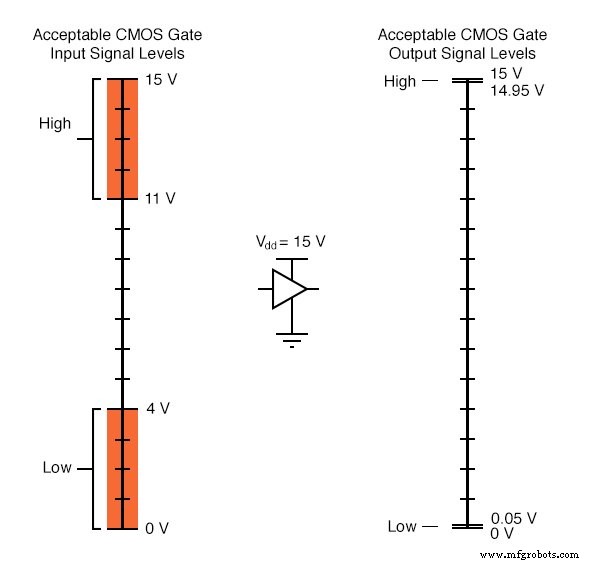

CMOSゲート入力の耐電圧

CMOSゲート回路には、TTLとはまったく異なる入力信号と出力信号の仕様があります。 5ボルトの電源電圧で動作するCMOSゲートの場合、許容可能な入力信号電圧は、「低」論理状態の場合は0ボルトから1.5ボルト、「高」論理状態の場合は3.5ボルトから5ボルトの範囲です。

「許容可能な」出力信号電圧(指定された負荷条件の範囲でゲートメーカーによって保証された電圧レベル)は、「低」論理状態の場合は0ボルトから0.05ボルト、「高」論理状態の場合は4.95ボルトから5ボルトの範囲です。 :

CMOSノイズマージン

これらの図から、CMOSゲート回路のノイズマージンはTTLよりもはるかに大きいことが明らかです。CMOSの低レベルおよび高レベルのマージンでは1.45ボルトであるのに対し、TTLでは最大0.7ボルトです。言い換えると、CMOS回路は、信号解釈エラーが発生する前に、入力ラインに重畳された「ノイズ」電圧の2倍以上の量に耐えることができます。

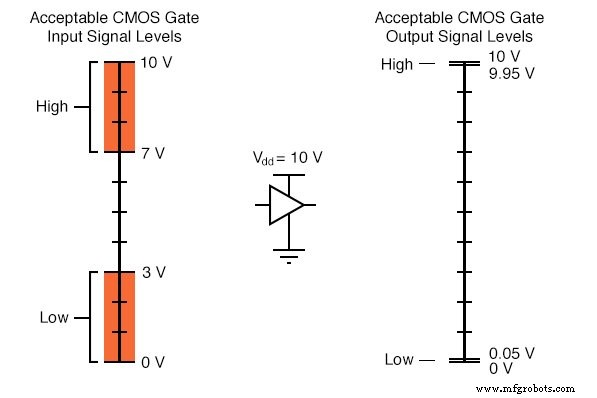

より高い動作電圧でのノイズマージン

CMOSノイズマージンは、動作電圧が高くなるとさらに広がります。 5ボルトの電源電圧に制限されているTTLとは異なり、CMOSは15ボルトの高電圧で電力を供給される場合があります(一部のCMOS回路は18ボルトの高さです)。

ここに示されているのは、入力と出力の両方で、それぞれ10ボルトと15ボルトで動作するCMOS集積回路の許容可能な「高」状態と「低」状態です。

許容可能な「高」および「低」信号のマージンは、前の図に示されているものよりも大きい場合があります。示されているのは、メーカーの仕様に基づく「最悪の場合」の入力信号性能を表しています。実際には、ゲート回路は、ここで指定されているものよりもかなり低い電圧の「高」信号とかなり高い電圧の「低」信号を許容することがわかる場合があります。

逆に、示されている非常に小さい出力マージン(「高」および「低」信号の出力状態を電源の「レール」から0.05ボルト以内に保証する)は楽観的です。このような「安定した」出力電圧レベルは、最小負荷の条件でのみ当てはまります。ゲートが負荷にかなりの電流を供給またはシンクしている場合、ゲートの最終出力MOSFETの内部チャネル抵抗のために、出力電圧はこれらの最適なレベルを維持できません。

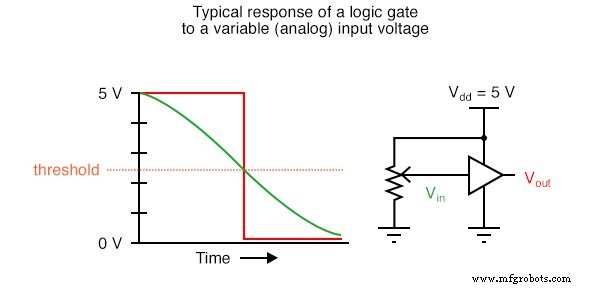

電圧しきい値

ゲート入力の「不確実な」範囲内で、ゲートの実際の「低」入力信号範囲を実際の「高」入力信号範囲から分割する境界点があります。つまり、ゲートの製造元によって保証されている最低の「高」信号電圧レベルと最高の「低」信号電圧レベルの間のどこかに、ゲートが実際に到達するしきい値電圧があります。 信号の解釈を「低」または「高」から、またはその逆に切り替えます。ほとんどのゲート回路では、この不特定の電圧は単一のポイントです:

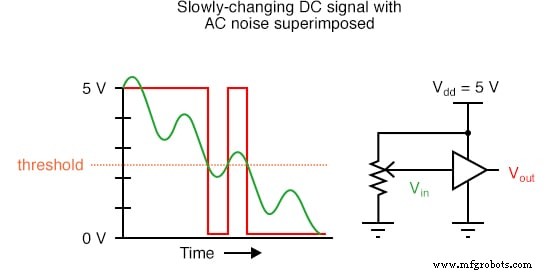

ACノイズのある入力

DC入力信号にAC「ノイズ」電圧が重畳されている場合、ゲートが論理レベルの解釈を変更する単一のしきい値ポイントにより、出力が不安定になります。

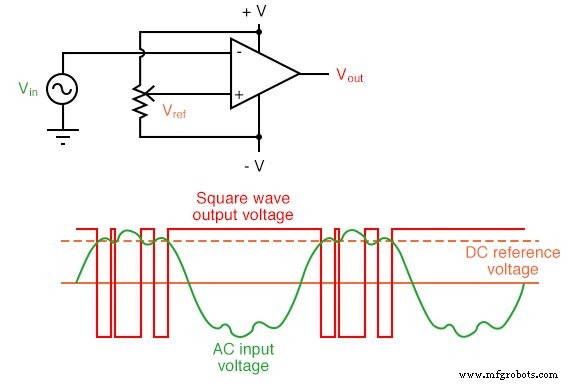

このシナリオがおなじみの場合は、(アナログ)電圧コンパレータのオペアンプ回路に関する同様の問題を覚えているためです。入力によって出力が「高」状態と「低」状態の間で切り替わる単一のしきい値ポイントでは、重大なノイズが存在すると、出力に不規則な変化が発生します。

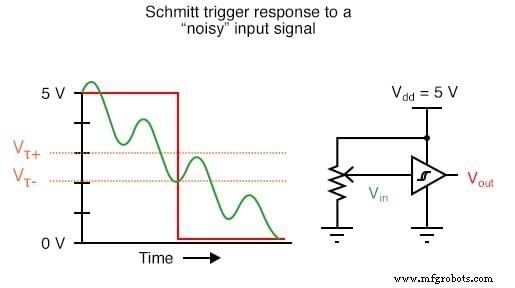

シュミットトリガー

この問題の解決策は、少しポジティブです。 増幅回路に導入されたフィードバック。オペアンプの場合、これは、出力を抵抗を介して非反転(+)入力に接続することによって行われます。

ゲート回路では、これには内部ゲート回路の再設計が必要であり、外部接続ではなくゲートパッケージ内でフィードバックを確立します。そのように設計されたゲートは、シュミットトリガーと呼ばれます。 。シュミットトリガーは、 2 に従って変化する入力電圧を解釈します しきい値電圧:正方向 しきい値(VT +)、およびネガティブゴーイング しきい値(VT-):

シュミットトリガーゲートのヒステリシス

シュミットトリガーゲートは、強磁性体のB-H曲線を連想させる、その中に描かれた小さな「ヒステリシス」記号によって概略図で区別されます。ゲート回路内の正のフィードバックによって生じるヒステリシスは、ゲートの性能に追加レベルのノイズ耐性を追加します。

シュミットトリガーゲートは、入力信号ラインでノイズが予想されるアプリケーションや、不安定な出力がシステムパフォーマンスに非常に悪影響を与えるアプリケーションで頻繁に使用されます。

同じシステムでTTLとCMOSテクノロジーを使用する

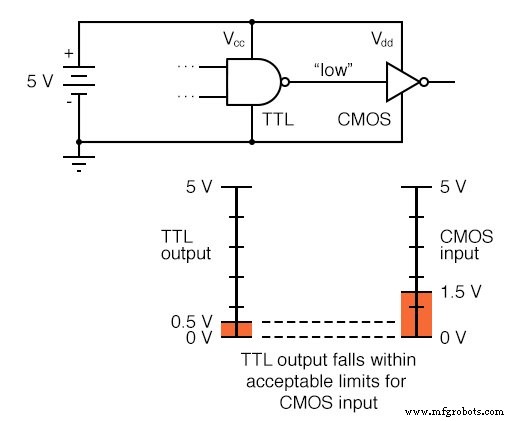

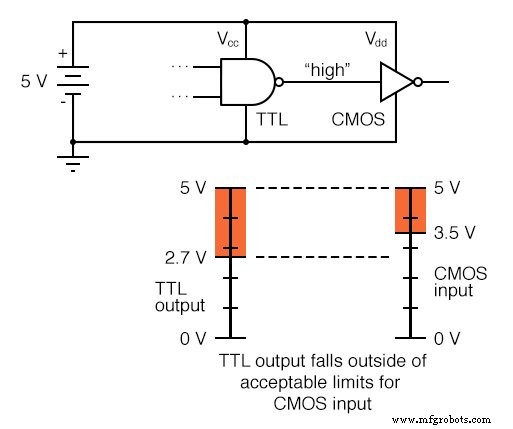

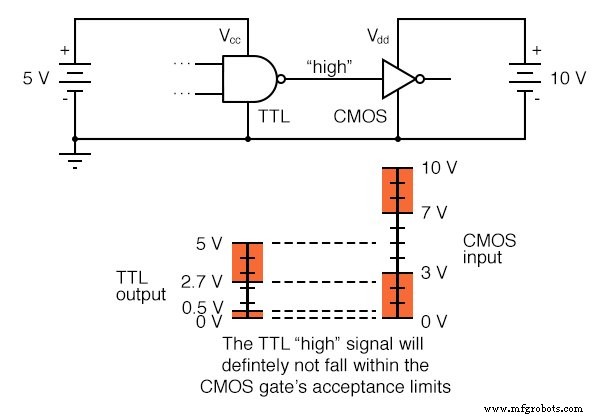

TTLおよびCMOSテクノロジの異なる電圧レベル要件は、2つのタイプのゲートが同じシステムで使用される場合に問題を引き起こします。 TTLゲートに必要な同じ5.00ボルトの電源電圧でCMOSゲートを動作させることは問題ありませんが、TTL出力電圧レベルはCMOS入力電圧要件と互換性がありません。

TTLとCMOSの組み合わせ回路のサンプル

たとえば、CMOSインバータゲートの入力に信号を出力するTTLNANDゲートを考えてみましょう。両方のゲートは、同じ5.00ボルトの電源(V cc )。 TTLゲートが「低」信号(0ボルトから0.5ボルトの間であることが保証されている)を出力する場合、それはCMOSゲートの入力によって「低」(0ボルトから1.5ボルトの間の電圧を期待)として適切に解釈されます。 / P>

ただし、TTLゲートが「ハイ」信号(5ボルトから2.7ボルトの間であることが保証されている)を出力する場合は、 可能性があります。 CMOSゲートの入力によって「高」として適切に解釈されない(5ボルトから3.5ボルトの間の電圧が予想される):

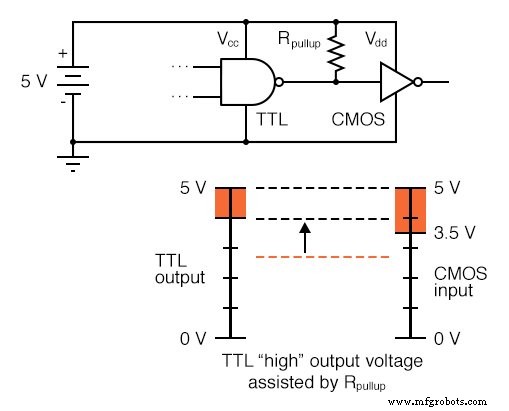

この不一致を考えると、TTLゲートがCMOS入力の「不確実な」範囲内にある有効な「ハイ」信号(有効、つまりTTLの標準による)を出力することは完全に可能です。誤って)受信ゲートによって「低」と解釈されます。この問題の簡単な「修正」は、プルアップ抵抗を使用してTTLゲートの「高」信号電圧レベルを増強することです。

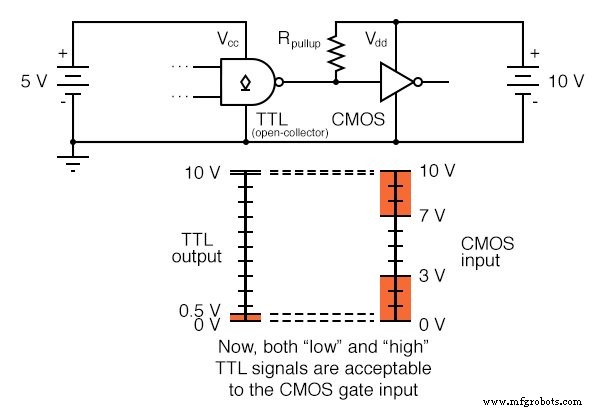

ただし、受信側のCMOSゲートに高い電源電圧が供給されている場合は、TTL出力をCMOS入力に接続するには、これ以上のものが必要です。

CMOSゲートでのオープンコレクタTTLゲートの使用

もちろん、CMOSゲートがTTLゲートの「ロー」出力を解釈することに問題はありませんが、TTLゲートからの「ハイ」信号はまったく別の問題です。 TTLゲート出力からの2.7ボルトから5ボルトの保証された出力電圧範囲は、「高」信号のCMOSゲートの7ボルトから10ボルトの許容範囲にはほど遠いです。

オープンコレクターを使用する場合 ただし、トーテムポール出力ゲートの代わりにTTLゲートを使用し、10ボルトのV dd へのプルアップ抵抗を使用します。 電源レールは、TTLゲートの「高」出力電圧をCMOSゲートに供給する全電源電圧まで上昇させます。オープンコレクタゲートは電流をシンクするだけで、ソース電流はシンクできないため、「高」状態の電圧レベルは、プルアップ抵抗が接続されている電源によって完全に決定され、不一致の問題を適切に解決します。

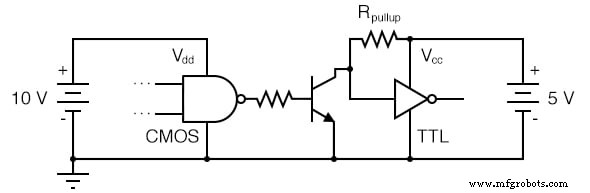

TTL入力にCMOS出力を使用する際の問題

CMOSゲートの優れた出力電圧特性により、通常、CMOS出力をTTL入力に接続するのに問題はありません。唯一の重要な問題は、TTL入力によって提示される電流負荷です。これは、CMOS出力が「ロー」状態のときに各TTL入力の電流をシンクする必要があるためです。

問題のCMOSゲートが5ボルト(V cc )を超える電圧源から電力を供給されている場合 )ただし、問題が発生します。 5ボルトを超えるCMOSゲートの「ハイ」出力状態は、「ハイ」信号に対するTTLゲートの許容入力制限を超えます。

オープンコレクタインバータ回路の使用

この問題の解決策は、ディスクリートNPNトランジスタを使用して「オープンコレクタ」インバータ回路を作成し、それを使用して2つのゲートを相互に接続することです。

「R プルアップ TTL入力はフローティングのままにすると自動的に「ハイ」状態になるため、抵抗はオプションです。これは、CMOSゲート出力が「ロー」でトランジスタがカットオフしたときに発生します。もちろん、このソリューションを実装することの非常に重要な結果の1つは、トランジスタによって作成される論理反転です。CMOSゲートが「ロー」信号を出力すると、TTLゲートは「ハイ」入力を認識します。また、CMOSゲートが「ハイ」信号を出力すると、トランジスタが飽和し、TTLゲートが「ロー」入力を認識します。この逆転がシステムの論理スキームで説明されている限り、すべてがうまくいくでしょう。

関連ワークシート:

-

デジタル論理信号ワークシート

産業技術