電界効果制御サイリスタ

従来のサイリスタデバイスの「駆動」(ゲートトリガー電流)要件を軽減するために設計された2つの比較的最近の技術は、MOSゲートサイリスタとMOS制御サイリスタ(MCT)です。

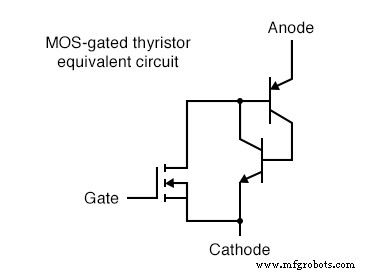

MOSゲートサイリスタ

MOSゲートサイリスタは、MOSFETを使用して、標準のサイリスタ構造の上部(PNP)トランジスタを介して導通を開始し、デバイスをトリガーします。 MOSFETは「駆動」するためにごくわずかな電流しか必要としないため(飽和させるため)、これによりサイリスタ全体が非常に簡単にトリガーされます:(下の図)

MOSゲートサイリスタの等価回路

通常のSCRはそのまま「駆動」するのが非常に簡単であるという事実を考えると、トリガーを開始するためにさらに感度の高いデバイス(MOSFET)を使用することの実際的な利点については議論の余地があります。また、サイリスタのゲート入力にMOSFETを配置すると、不可能になります。 逆トリガー信号でオフにします。低電流ドロップアウトのみが、ラッチされた後にこのデバイスの導通を停止させることができます。

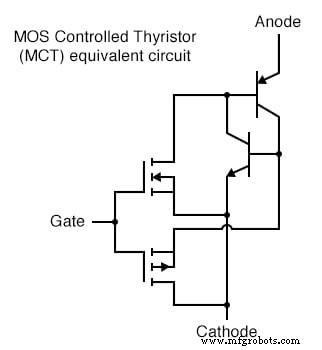

MOS制御サイリスタ

ほぼ間違いなくより大きな価値のあるデバイスは、完全に制御可能なサイリスタであり、それによって、小さなゲート信号がサイリスタをトリガーし、それを強制的にオフにすることができます。このようなデバイスは存在し、 MOS Controlled Thyristor と呼ばれます。 、または MCT 。共通のゲート端子に接続されたMOSFETのペアを使用します。1つはサイリスタをトリガーし、もう1つはサイリスタを「トリガー解除」します。

MOS制御サイリスタ(MCT)の等価回路

正のゲート電圧(カソードに対して)は、上部(Nチャネル)MOSFETをオンにし、上部(PNP)トランジスタにベース電流を流し、トランジスタペアを「オン」状態でラッチします。両方のトランジスタが完全にラッチされると、アノードとカソードの間で電圧降下がほとんどなくなり、制御された電流が最小(保持)電流値を超える限り、サイリスタはラッチされたままになります。ただし、負のゲート電圧が印加されると(ラッチ状態のカソードとほぼ同じ電圧のアノードに対して)、下部のMOSFETがオンになり、下部(NPN)トランジスタのベース間で「短絡」します。とエミッタ端子、したがってそれをカットオフに強制します。 NPNトランジスタが遮断されると、PNPトランジスタは導通状態から外れ、サイリスタ全体がオフになります。ゲート電圧は、MCTを介した伝導を完全に制御します。つまり、ゲート電圧をオンまたはオフにします。

ただし、このデバイスはまだサイリスタです。ゲートとカソードの間にゼロ電圧が印加されると、どちらのMOSFETもオンになりません。その結果、バイポーラトランジスタペアは最後の状態(ヒステリシス)のままになります。したがって、ゲートへの短い正のパルスはMCTをオンにし、短い負のパルスはMCTを強制的にオフにし、ゲート電圧が印加されていないため、すでにある状態を維持できません。本質的に、MCTはIGBTのラッチバージョンです。 (絶縁ゲートバイポーラトランジスタ)。

レビュー:

- MOSゲートサイリスタ NチャネルMOSFETを使用してサイリスタをトリガーするため、必要なゲート電流は非常に低くなります。

- MOS制御サイリスタ 、または MCT 、2つのMOSFETを使用して、サイリスタを完全に制御します。正のゲート電圧がデバイスをトリガーします。負のゲート電圧はそれを強制的にオフにします。ゼロゲート電圧により、サイリスタは以前の状態(オフまたはラッチオン)にとどまることができます。

産業技術