EMI の影響を軽減するための高速 PCB ルーティング テクニック

新世代の電子技術は、コンポーネントのエッジ速度の高速化につながります。回路の動作速度の向上により、PCB 設計に対する要件がますます厳しくなっています。 PCB 設計の品質は、コンポーネントと回路全体の動作性能を決定します。特に、コストや PCB 面積、包括的な回路の機能を考慮すると、EMI (電磁インターフェース) の発生源は複雑なメカニズムでますます広範になります。

EMI メカニズムとソリューション

EMI の主な要素には、電磁干渉源、伝送経路、および干渉対象が含まれます。 EMI の発生につながる要素を特定した上で、解決しやすい要素と、PCB 設計の過程で部分的にしか解決できない要素を特定し、レイアウト、配線のプロセスで考慮できるようにする必要があります。

• レイアウト

PCB レイアウトに関しては、さまざまな機能に従って領域を分割する必要があります。さまざまな機能がさまざまな領域に分散されていますが、機能領域の機密ユニットには特別な注意を払う必要があります。

一般に、PCB レイアウトでは次の原則に従う必要があります:

a.高速回路では、コンポーネントのピン分布のパラメータを考慮する必要があり、特に高速クロック信号ではコンポーネント ピンの分布容量が非常に重要です。一方、分布インダクタンスは、信号の発振につながり、回路機能の障害を引き起こす可能性があるため、参考にする必要があります。したがって、レイアウトのプロセスでは、将来の配線のためにリード長を短くし、EMI の影響を減らして、高密度に分布を配置する必要があります。

b.アナログ部品と電子部品の両方が回路内にある場合、レイアウトの過程でそれらを個別に分散する必要があります。デジタルコンポーネントの信号は、複数の高調波が存在する複雑な複合体を持っているため、アナログ信号に大きな影響を与えます。そのため、細心の注意を払って検討する必要があります。

c.クロックユニットは高速回路に不可欠です。クロックユニットの動作メカニズムは実はノイズ源に相当し、特定の条件が満たされるとこのユニットが発振します。伝導性干渉と放射干渉の重要な原因として、クロック ユニットを PCB の端に配置してはなりません。そうしないと、EMI が非常に深刻になります。クロック ユニットを PCB の中央に配置する必要があり、回路の EMI を大幅に削減できます。

• ルーティング

PCB ルーティングのプロセスでは、低コストの状況下で、EMI の影響を減らすために、グランド プレーンを可能な限り大きくすることができます。ただし、コストを厳密に管理する必要がある場合は、PCB のレイヤー数とスタック シーケンスを慎重に検討する必要があります。また、信号の種類を考慮し、高速信号と低速信号で独立してルーティングを行う必要があります。また、ノイズの発生源やノイズ対策の強化方法、インピーダンス整合の問題(高速信号は整合がとれていないと確実に信号が反射し、回路の信頼性が低下します)、ネットリストなども考慮する必要があります。 .

a.ルーティングの基本原則

ルーティングで従う一般原則は次のとおりです。

1).ルーティングではブレークポイントを避ける必要があります。これは、下の図 1 に示すように、直角を避ける必要があることを意味します。

直角は反射する可能性があるので、この現象を避けるために変曲点を滑らかに設計する必要があります。同時に、主要な信号が分割された領域を超えてはなりません。そうしないと、EMI が即座に強化されます。最も一般的な信号バイパスは、異なる電力分割領域を横断することです。

2). レイアウトの過程で、アナログ部品とデジタル部品を分離する必要があるため、それらの配線を分割する必要があります。同時に、信号線よりも電源線よりもグランド線の幅の方が太いことを原則として、グランド線と電源線の幅を広くする必要があります。さらに、信号線のルーティングでは 3W の原則を十分に考慮する必要があり、多層基板の場合は内部層で 20H の原則を考慮する必要があります。上記の作業が完了すると、EMI の 70% を回避できます。アナログ感応配線に関しては、接地などの対策を講じることができます。

3) USB2.0 またはその他の高速差動ラインのルーティングには、カップリング ルーティングを適用し、差動ペア間の基準面の整合性を保証する必要があります。差動ペアは一般に高速信号であるため、配線を PCB の端に配置しないでください。

b.ループ

PCB 設計ではループを避けることはできません。信号の流出から流入までループが形成され、各ループが機能上のアンテナとしての役割を果たします。 PCB の EMI を減らすには、ループの数とループのアンテナ能力の両方を減らす必要があります。これは、PCB 設計で各信号の流れ方向を認識する必要があり、高速信号用にループ領域を減らす必要があることを意味します。

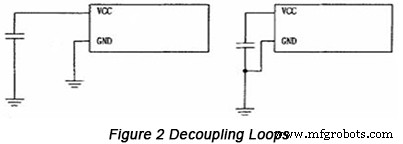

回路では、図 2 に示すように、最も一般的に使用されるループは、デカップリング コンデンサに含まれる電源ループにあります。

図 2 の左図のようにデカップリング コンデンサを配置すると、明らかな EMI 現象を伴う比較的大きな電流ループが生成されます。逆に、デカップリング コンデンサをチップの近くに配置した図 2 の右図では、EMI を低減することを主な機能として、非常に小さなデカップリング ループが生成されます。ループを減らすために従うべき原則が表示されます:

1).各信号線の 2 点間には 1 つのパスのみが確保されます。

2).グランドプレーンは、信号ループをブロックしないように適用する必要があります.

c. PCBのアース線

1). PCB 接地のシステムにおけるデジタル グランド、アナログ グランド、およびシステム シールド グランドの違いを明確にする必要があります。デジタルグランドとアナロググランドは磁気ビーズとコンデンサで分離し、デジタルグランドとフィールドグランドは直接接続する。干渉防止能力が強化され、システム間の電気レベル差が減少するように、アース線による閉回路。

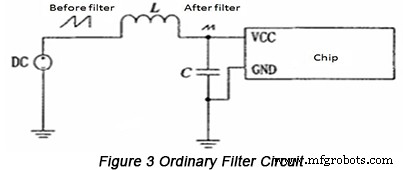

• フィルター設計

高速基板では、電源線や信号線にフィルタ処理を施すことができます。一般的な対策には、磁気フィルター コンポーネント、EMI フィルター、およびデカップリング コンデンサーの追加が含まれます。

a.デカップリングコンデンサの選択

1). 回路では、デカップリング コンデンサは電源をスムーズにし、干渉防止能力を強化するのに役立ちます。一般に、セラミックコンデンサは、安定性が高く、精度が高く、体積が小さく、ESR(等価直列抵抗)が低いため、デカップリングコンデンサとして取り上げられています。回路設計では、抵抗値は1μFから100μFの範囲で選択されますが、回路に応じて耐圧を考慮する必要があります。

2)デカップリングコンデンサは部品の近くに配置する必要があります。

/P>

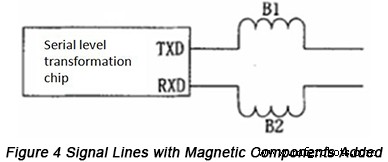

b.磁性部品の選択

磁気コンポーネントは、インダクタと磁気ビーズに分類できます。通常、インダクタは電源端子の端にピックアップされ、信号ライン間に磁気ビーズが配置されます。コンポーネントを選択するプロセスでは、飽和パラメータを考慮する必要があります。磁性部品が飽和状態に達すると、それらは焼失します。さらに、磁気コンポーネントの品質と DCR パラメーターの両方を考慮する必要があります。

信号線の間で一般的に使用される対策は、EMI 容量を強化するためにシリアル線に磁気ビーズを適用することです。

c. EMI フィルタの選択

コモンモード干渉が深刻な領域は、電源が入っていて信号線が出ている場所にあります。コモン モード干渉を回避するための通常の対策には、コモン モード インダクタ、ピエゾ抵抗、LC 回路、および特定の EMI フィルタの追加が含まれます。高速回路では、USB や HDMI などのデジタル インターフェイスでの高速伝送のために EMI 問題を考慮する必要があります。

•信号の反射

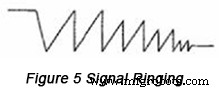

信号伝送では、ソース端子のエネルギーは常に負荷端子に伝送されることが期待されます。つまり、ZL は ZO と等しくなければなりません。それらが互いに等しくない場合、エネルギーの一部が反射されます.

回線の伝送遅延が比較的長い場合、より強い信号が送信元端子に反射されます。次に、リンギングが生成されたときの補償のために、比較的大きな量を変更する必要があります。これを以下の図 5 に示します。

信号にリンギングが発生すると、EMI は深刻度のピークに達します。 PCB 設計でこのような現象を回避するには、表 1 の原則に従ってください。

| 信号エッジ時間 (ns) | 信号線の長さ (インチ) |

| 5 | 8.6 |

| 4 | 6.9 |

| 3 | 5.1 |

| 2 | 3.4 |

| 1 | 1.7 |

EMI テスト

製品設計後、EMI を回避するためのさまざまな対策を講じても、テストを実施するまで問題は見つかりません。次に、問題を解決するためにいくつかの変更を加えることができます。

EMI テストには、テスト方法、デバイス、およびテスト位置が含まれます。試験方法は、すべての項目を参照して実施する必要があります。デバイスが標準に達しない場合は、分光計を定性テストに適用できます。デバイスの特定の EMI 値が必要な場合は、専門的なデバイスを適用する必要があります。テスト位置に関しては、暗室でテストを行うのが最善です.

役立つリソース

• 見逃せないエンジニアフレンドリーな PCB レイアウト ガイドライン

• 組み込みアプリケーション システムにおける高速 PCB 設計に関する研究

• EMI および EMC 自動化ツールの最も包括的な紹介

br />• EMI を打ち負かすための自動車回路設計の 5 つのヒント

• PCBCart のフル機能 PCB 製造サービス - 複数の付加価値オプション

• PCBCart の高度な PCB アセンブリ サービス - 1 個から開始

産業技術