T型ゲートデュアルソーストンネル電界効果トランジスタのアナログ/ RF性能

要約

本論文では、シリコンベースのT型ゲートデュアルソーストンネル電界効果トランジスタ(TGTFET)を提案し、TCADシミュレーションによって調査した。対照的な研究として、TGTFET、LTFET、およびUTFETの構造、特性、およびアナログ/ RF性能について説明します。 T字型ゲートによって導入されたゲートオーバーラップは、トンネリングジャンクションの効率を高めることができます。 TGTFETのデュアルソース領域は、オン状態電流( I )を増加させる可能性があります オン )二重のトンネリングジャンクションエリアを提供することによって。デバイスのパフォーマンスをさらに向上させるために、TGTFETにn +ポケットが導入され、バンド間のトンネリングレートがさらに向上します。シミュレーション結果は、TGTFETの I オン およびスイッチング比( I オン / 私 オフ )81μA/μmおよび6.7×10 10 に達する 1 Vゲートからソース電圧( V g )。 TGTFETの平均サブスレッショルドスイング(SS avg 、0〜0.5 V V g )51.5 mV / decに達し、TGTFETの最小サブスレッショルドスイング(SS min 、0.1 V V g )24.4 mV / decに達します。さらに、TGTFETはドレイン誘導障壁低下(DIBL)効果に対して強いロバスト性を持っていることがわかります。 TGTFETの設計ガイドラインを作成するために、デバイスの性能に対するドーピング濃度、幾何学的寸法、および印加電圧の影響を調査します。さらに、相互コンダクタンス( g m )、出力コンダクタンス( g ds )、ゲートからソースへの容量( C gs )、ゲートからドレインへの静電容量( C gd )、カットオフ周波数( f T )、TGTFETのゲイン帯域幅(GBW)は、ドレイン-ソース間電圧( V d )、 それぞれ。構造上の利点を利用して、TGTFETはUTFETおよびLTFETと比較してより優れたDC / AC特性を取得します。結論として、かなり優れたパフォーマンスにより、TGTFETは次世代の低電力およびアナログ/ RFアプリケーションにとって非常に魅力的な選択肢になります。

背景

金属酸化物半導体電界効果トランジスタ(MOSFET)のスケールダウンにより、集積回路(IC)の消費電力、スイッチング特性、回路機能、およびIC密度が大幅に向上します[1、2]。しかし、供給電圧のスケーリングとオフ状態のリーク電流の減少との間の矛盾した矛盾( I オフ )最終的には許容できない高電力消費になります[3]。同時に、短チャネル効果(SCE)によって引き起こされる信頼性の低下はますます深刻になっています[4、5]。これらの問題に対処するために、サブスレッショルドスイング(SS)とデバイスの供給電圧を下げることが有効です。バンド間トンネリングメカニズムに基づいて、トンネル電界効果トランジスタ(TFET)は60 mV / dec未満のサブスレッショルドスイング(SS)に到達し、供給電圧を効果的に下げることができます[6,7,8,9,10] 。さらに、ソースの近くにトンネル接合が存在するため、TFETは通常、ゲートからソースへの静電容量( C )が小さくなっています。 gs )[1、11]これはデバイスの周波数性能に有益です。

最近の研究によると、TFETは将来の低電力アプリケーション[12,13,14,15,16]およびアナログ/ RFアプリケーション[17,18,19]の有望な候補であるように思われます。ただし、有効なトンネル電流領域が小さいため、トンネル電流が制限されることは、従来のP-I-N TFETに固有の欠点となり、オン状態の動作電流( I )が低くなります。 オン )。 TFETの性能を向上させるために、近年、多くの新しい構造が提案されています[20、21、22、23、24、25]。凹型ゲートの恩恵を受けて、L字型トンネル電界効果トランジスタ(LTFET)[23、24]およびU字型トンネル電界効果トランジスタ(UTFET)[25]が、高い I > オン コンパクトなデバイス構造。ただし、LTFETとUTFETにはまだ改善の余地があり、これらのデバイスのアナログ/ RF性能を研究するためにより多くの努力を費やす必要があります。

本論文では、デュアルソースを備えたT型ゲートデュアルソーストンネル電界効果トランジスタ(TGTFET)を提案し、TCADシミュレーションによって研究した。設計されたTGTFETは、LTFETおよびUTFETと比較してトンネリング接合面積を2倍にすることができます。設計されたT字型ゲートによって導入されたゲートオーバーラップは、バンド間トンネリングレート(BBTレート)を向上させることができます。シミュレーション結果は、提案されたTGTFETがより高い I を獲得することを示しています オン (8.1×10 − 5 V でのA /μm d =1 V)同じ条件下でのLTFETおよびUTFETよりも。 SS min の両方 ( V g =0.1 V)およびSS avg (0〜0.5 V V g )のTGTFETは60 mV / dec未満です(それぞれ24.4 mV / decと51.5mV / dec)。 TGTFETは、より優れた入出力特性( g m =232μS/μm、 g ds =214μS/μm)UTFETおよびLTFETよりも。さらに、TGTFET、UTFET、およびLTFETの容量特性について詳しく説明します。最後に、TGTFETはより優れたアナログ/ RF性能を獲得します( f T =11.9GHzおよびGBW =2.3 GHz)、UTFETおよびLTFETと比較。その結果、かなり良好な性能のTGTFETを得ることができます。この論文の構造は次のとおりです。「方法」セクションには、TGTFET、LTFET [23、24]、およびUTFET [25]の構造とパラメータの説明が含まれています。 ]およびTCADシミュレーション方法。 「結果と考察」セクションには、シミュレーション結果の説明が含まれています。このセクションでは、TGTFETのメカニズム、特性、およびアナログ/ RF性能を調査し、LTFETおよびUTFETと比較します。 TGTFETに対するデバイスパラメータの影響も詳細に分析されます。 「結論」セクションでは、このペーパーの結論を示しています。

メソッド

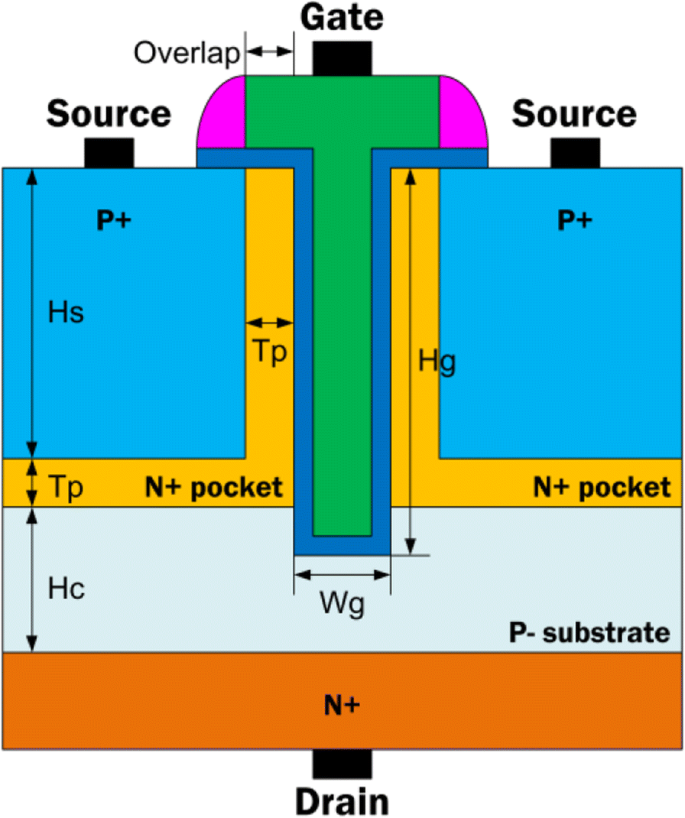

T型ゲートデュアルソーストンネル電界効果トランジスタ(TGTFET)の構造を図1に示します。ゲートの形状は、アルファベットの「T」(緑色の領域)に似ています。デュアルソース領域は、ゲートの両側にあります(サファイア領域)。チャネルトンネリングレートを上げるために、2つのn +ポケット(黄色の領域)が挿入されています[20、21、22]。 n +ドレインはチャネルの下部に配置されます。したがって、T字型のゲートは垂直方向と横方向の両方でn +ポケットと重なります。このようにして、トンネリング接合部の上部の電界を増加させることができます。電界の増強により、エネルギーバンドはより急に曲がります。最後に、コーナー電界の増強により、電子トンネリング速度が増強されます[26]。

提案されたT字型ゲートデュアルソーストンネル電界効果トランジスタ(TGTFET)の概略図

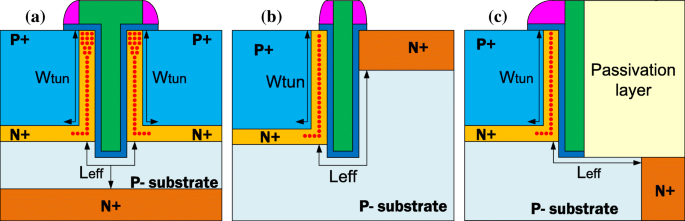

図2は、LTFET [23、24]、UTFET [25]、およびTGTFETのデバイス構造を示しています。ゲートのオーバーラップは、TGTFETのトンネリング効率を高めるのに役立ちます。 TGTFETのデュアルソース領域は、LTFETおよびUTFETと比較してトンネリングジャンクション領域を2倍にすることができます。

a の比較 提案されたTGTFET、 b UTFET、および c LTFET

シミュレーションで使用されるシリコンベースのTGTFET、UTFET、およびLTFETのパラメータは、次のとおりです。Hs=30 nm(ソース領域の高さ)、Hg =40 nm(凹型ゲートの高さ)、Wg =6 nm(ゲート領域)、Hc =15 nm(チャネル領域の高さ)、Tp =5 nm(n +ポケットの厚さ)、 ϕ =4 。 33 eV(ゲート仕事関数)、Tox =2 nm(HfO 2 の厚さ ゲート誘電体)、 N S =1×10 20 cm -3 (p +ソースドーピング濃度)、 N D =1×10 19 cm -3 (n +ドレインドーピング濃度)、 N sub =1×10 17 cm -3 (p-基板ドーピング濃度)、および N P =5×10 18 cm -3 (n +ポケットドーピング濃度)。シミュレーションの幅係数はデフォルトで1μmです。

TGTFET、UTFET、およびLTFETのシミュレーションは、Silvaco AtlasTCADツールで実行されます。非ローカルBTBTモデルがこのシミュレーションに導入され、エネルギーバンドの空間的変動が考慮されます。これは、BTBTトンネリングプロセスの精度を高めるのに役立ちます。ロンバルディ移動度モデルは、チャネル移動度をより正確にするために考慮されます(横方向の場とドーピング濃度を含む表面散乱を考慮することによって)。フェルミ統計とバンドギャップ狭小化モデルは、高濃度にドープされた領域の効果に適合するように考慮されます。この論文では、Shockley-Read-Hall再結合モデルも考慮されています。

結果と考察

さまざまなパラメータを使用したデバイスメカニズムとDC特性

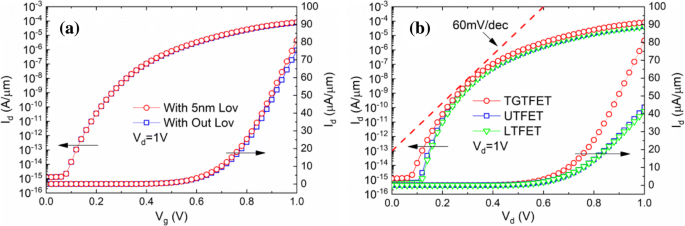

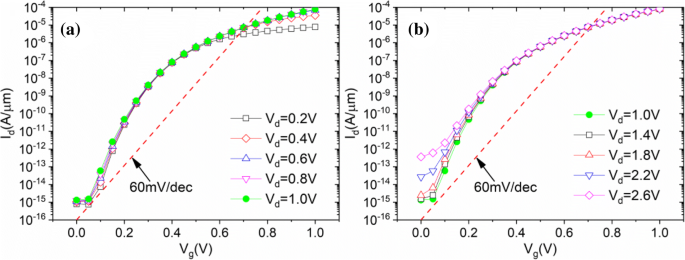

図3aは、ゲートオーバーラップがある場合とない場合のTGTFETの伝達特性を示しています。追加のゲートオーバーラップにより、 I オン 7.5×10 -5 から増加 〜8.1×10 -5 A / μ V でのm g = V d =1V。図3bは、TGTFET、UTFET、およびLTFETの伝達特性曲線を示しています。比較をより正確にするために、これら3つのデバイスのシミュレーションモデルと幾何学的寸法は同一に設定されています。その結果、TGTFETでは I が約2倍に増加します。 オン 図3bに示すように、LTFETおよびUTFETと比較。 SS min TGTFETの速度は V で24.4mV / decです。 g =0.1 V、SS avg 0 V < V の場合、は51.5 mV / decです。 g <0.5 V.スイッチング比( I オン / 私 オフ )は6.7×10 10 V で g = V d =1Vおよび6.5×10 8 V で g = V d =0.5V。

シミュレートされた a ゲートオーバーラップがある場合とない場合のTGTFETの伝達特性と b TGTFET、UTFET、LTFETの伝達特性

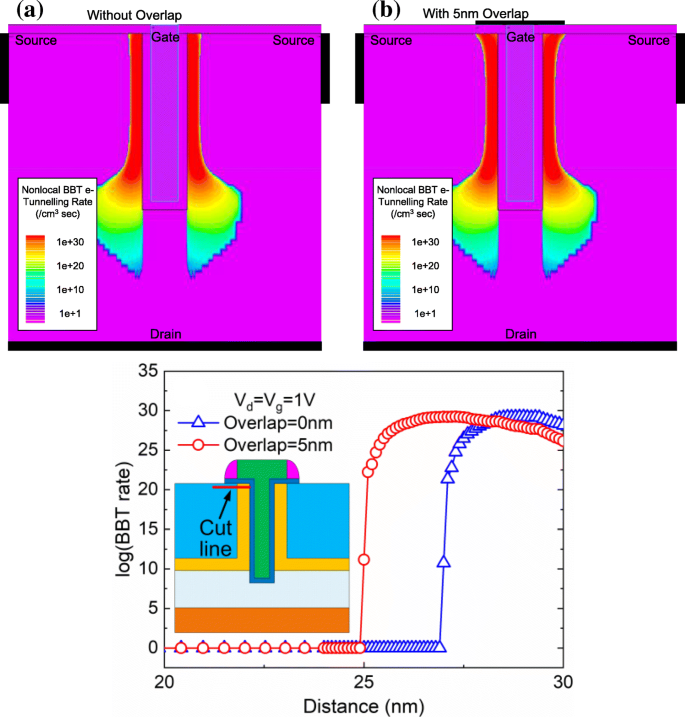

図4a、bは、5nmゲートオーバーラップがある場合とない場合のTGTFETのBBTレートを示しています。図4cから、ゲートの重なりが5 nmのデバイスは、デバイス表面の下の電子トンネル領域が広く、 I につながる可能性があることがはっきりとわかります。 オン 増加しています。

a のシミュレートされたBBT電子トンネリング速度図 ゲートオーバーラップのないデバイス、 b 5 nmのゲートオーバーラップを備えたデバイス、および c デバイス表面から1nm下の2つのデバイスのBBT電子トンネル速度。 V g = V d =1 V

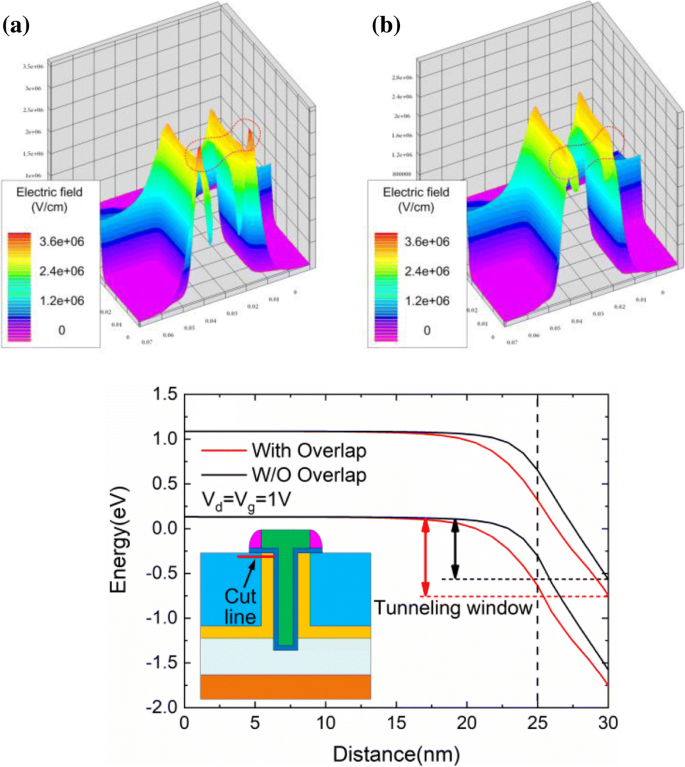

図5a、bは、ゲートオーバーラップがある場合とない場合のTGTFETの電界の3D図を示しています。図5aの破線の円に示すように、2つの電界ピークが5nmのゲートオーバーラップでTGTFETに現れます。ゲートのオーバーラップがないため、図5bには電界のピークは表示されません。図5cは、デバイスの表面下のエネルギーバンド構造を示しています。図5cの挿入図は、カットラインの位置を示しています。ゲートオーバーラップを使用すると、より大きなトンネリングウィンドウを取得できます。したがって、より高いBBT率と I オン 達成することができます。

デバイスの電界の3D概略図 a オーバーラップと b 重複なし;シミュレートされた c ソースからポケット領域(酸化物界面から1 nm下)までのエネルギーバンド図

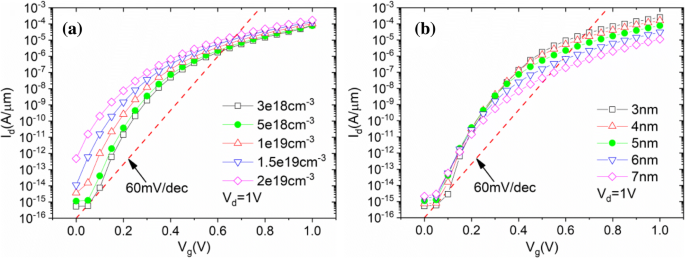

図6は、TGTFETのパフォーマンスに対するn +ポケットの影響を示しています。 私 オフ 図6aに示すように、n +ポケットドーピング濃度の増加とともに急速に増加します。 SSが低く I が大きい オン N の場合、n +ポケット(Tp)の厚さを7nmから3nmに減らすことで得られます。 P =5×10 18 cm -3 、図6bに示すように。同時に、図6bには、有意なサブスレッショルド電流は示されていません。図6aから、n +ポケットのドーピング濃度が比較的低いと、サブスレッショルド電流を抑えるのに役立つことが確認できます。

異なるn +ポケット a でシミュレートされたドレイン電流 濃度と b V での厚さ d =1 V

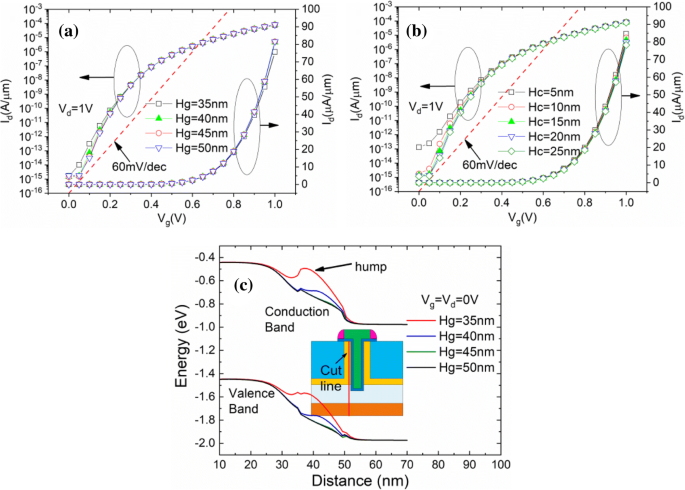

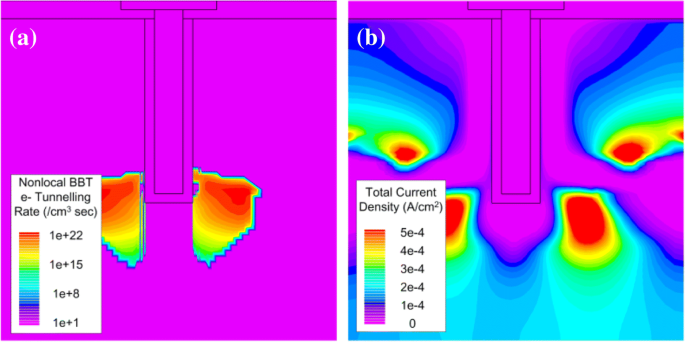

ゲートの高さ(Hg)とチャネルの厚さ(Hc)の影響を、別々に図7a、bに示します。小さな私 オン そして、Hgが増加しているときにSSの改善が現れます。 Hg =35 nmの場合、図7cに示すように、オン状態の電流経路に明らかなエネルギーバンドのこぶがあり、幸運な電子(トンネル接合を通過した電子)に対する特定の障害になります。 私 on 下降。 Hgが増加すると、エネルギーバンドのこぶが弱まり、 I が発生します。 オン とSSの改善。少し私 オン 図7bに示すように、Hcが減少すると改善が得られます。ただし、Hcが5 nmに低下すると、しきい値以下の特性が大幅に低下することがあります。これは、図8に示すように、n +ポケットのコーナーでのしきい値以下のトンネル電流の増加によって説明できます。図8aは、Hc =5 nmの場合の明らかなオフ状態のバンド間トンネル現象を示していますが、図8bは私 オフ Hc =5nmのときの電流密度。

a を使用したTGTFETのシミュレートされた転送特性 異なる水銀、 b 異なるHc、および c 電流経路上の伝導帯のこぶ

オフ状態のシミュレーション図 a BTBT電子トンネリング速度と b Hc =5nmのときの電流密度

図9に示すように、ドレインからソースへの電圧( V )の影響 d )もこのホワイトペーパーで考慮されています。 V の場合 d <0.6 V、 I オン V の増加とともに明らかに増加します d 、図9aに示すように。これは、 V の増加に応じてpチャネルの電位がゆっくりと成長しているという事実によって説明されます。 d その結果、pチャネルの抵抗が減少します。 V の場合 d > 1.8 V、図9bに示すように、 I オン V の増加に伴ってほとんど増加しません d 、しかし私 オフ かなり増加します。これは、 V の増加に伴い、n +ポケットのコーナーでのしきい値以下のトンネル電流が急速に増加するためです。 d 。最後に、0.6 V < V の場合 d <1.8 V、TGTFETは良好で安定した性能を示します。その結果、TGTFETはドレイン誘導障壁低下(DIBL)に対して堅牢であり、より広い印加電圧ダイナミックレンジで良好で安定した性能を示します。

a のシミュレートされたドレイン電流 V d ≤1Vおよび b V d ≥1V

TGTFET、UTFET、およびLTFETのアナログ/ RFパフォーマンス

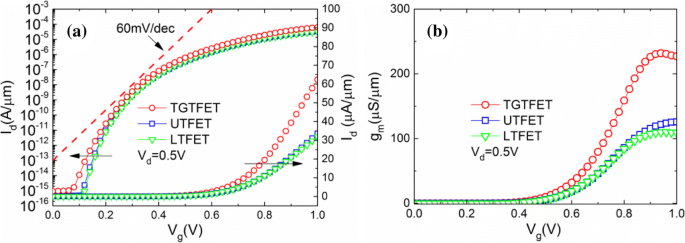

図10は、 V でのTGTFET、UTFET、およびLTFETの伝達特性と相互コンダクタンス曲線を示しています。 d =0.5 V.相互コンダクタンス( g m )は、式(1)に示すように、伝達特性曲線の一次導関数から取得できます。 (1)[27,28,29]:

$$ {g} _ {\ mathrm {m}} ={dI} _ {\ mathrm {d} s} / {dV} _ {\ mathrm {gs}} $$(1)<図> <画像>

a 伝達特性と b V でのTGTFET、UTFET、およびLTFETの相互コンダクタンス曲線 d =0.5 V

その結果、TGTFET(232μS/μm)の最大相互コンダクタンスは、図10に示すように、UTFET(120μS/μm)およびLTFET(110μS/μm)の最大相互コンダクタンスの約2倍になります。デュアルソースとゲートのオーバーラップによってもたらされる電流ゲイン。

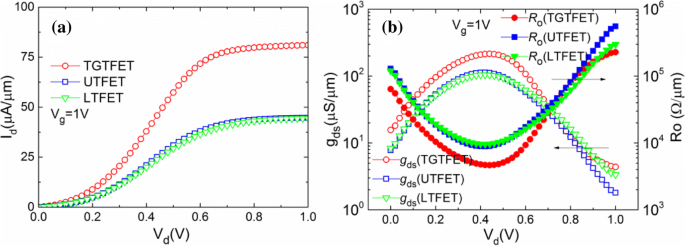

図11は、出力特性、出力コンダクタンス( g )を示しています。 ds )、および出力インピーダンス( R o )TGTFET、UTFET、およびLTFETの曲線。図11aに示すように、デバイスの出力電流は V の増加とともに増加することがはっきりとわかります。 d 、ただし V の場合 d 0.6 Vを超えると、出力電流が飽和する傾向があります。観察すると、TGTFETの出力電流がUTFETおよびLTFETの出力電流の2倍であることが簡単にわかります。図11bは、出力コンダクタンス( g )を示しています。 ds )および出力インピーダンス( R o )TGTFET、UTFET、およびLTFETの曲線。 g ds 式(1)に示すように、出力電流を導出することで求めることができます。 (2)[27、29] while R o 出力コンダクタンスの逆数として表すことができます。

$$ {g} _ {\ mathrm {ds}} ={dI} _ {\ mathrm {ds}} / {dV} _ {\ mathrm {ds}} $$(2)<図> <画像> <ソースtype ="image / webp" srcset ="// media.springernature.com / lw685 / springer-static / image / art%3A10.1186%2Fs11671-018-2723-y / MediaObjects / 11671_2018_2723_Fig11_HTML.png?as =webp">

a 出力特性、 b 出力コンダクタンス( g ds )、および c 出力インピーダンス( R o )TGTFET、UTFET、およびLTFETの曲線

出力電流の利点により、TGTFETは最高の g を獲得します ds 最小の R o これらの3つのデバイスの。 1 Vゲートバイアス条件下で、TGTFETは最大の g を取得しました。 ds 214μS/μmおよび最小 R o 0.45 V V で4.6kΩ/μm d 。同じゲートバイアス条件下で、UTFETとLTFETは最大の g を取得しました ds 113μS/μmおよび105μS/μmと最小の R o 0.4 V V で9.0kΩ/μmおよび9.6kΩ/μm d 。

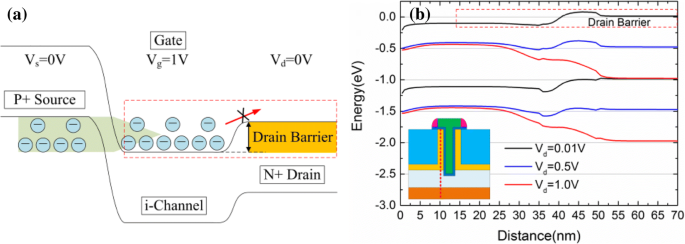

さらに、図11では、デバイスの出力特性の線形領域が特定の非線形性を示していることを確認するのは難しくありません。図11aに示すように、 R o 最初に減少し、次に V の増加とともに増加します d 。いくつかの研究グループは、この現象について対応する物理的プロセスを示しています[7、30]が、明確に説明されていないいくつかの問題がまだあります。ご存知のとおり、 R o チャネル領域とトンネリングジャンクションの抵抗によって決定されます。 V の場合 d <0.4 V、 R o V の増加とともに減少します d 。 V の場合、次の状況を考慮してください d =0Vおよび V g =1 V、幸運な電子はどれもドレイン側に掃引できず、図12a、bの赤い点線の枠に示すように、ほとんどすべての電子が比較的高いドレインバリアによってチャネル領域にトラップされます。 0 V < V の場合 d <0.4 V、 V の増加に伴い d 、ドレンバリアが弱くなります(図12bを参照)。したがって、チャネル領域にトラップされた電子は、ドレインバリアを通過して、ドレインによって収集される可能性があります。これは、チャネルからドレインへの電子の熱励起プロセスです。最後に、トンネリングジャンクションが完全にオンになっているため( V の場合) g =1 V)、トンネル電流は常に過剰な状態にあり、トンネル接合によって導入された抵抗は無視できます。このとき、 R o チャネル抵抗と R によって決定されます o ドレインバリアを通過する電子の熱励起プロセスによって決定されます。したがって、 R o V の増加とともに減少します d 。 V の場合 d > 0.6 V、これら3つのデバイスは徐々に飽和領域に入り R o 大きくなります。これは、 V の場合 d が大きい場合、トンネリング接合部を通過するほとんどすべての電子は、比較的高い電界によってドレイン側に掃引されます。トンネル電流がドレイン電流の限界になります。この状態では、 R o 主にトンネリングジャンクションによって決定されます。ただし、 V の間、トンネリング効率を大幅に向上させることはできません。 d 増加しています。 V d 図12bに示すように、トンネリングジャンクション(n +ポケット側)のエネルギーバンド構造にわずかな影響を及ぼします。その結果、トンネル電流が明らかに増加することはなく、 I はほとんどありません。 オン V が継続的に増加すると増加します d ( V の場合 d > 0.6 V)、これはインピーダンスが増加することを意味します。さらに、0.4 V < V の場合 d <0.6 V、 R o チャネル抵抗とトンネリングジャンクションの両方によって決定されます。

a V でのエネルギーバンドの概略図 d =0Vおよび V g =1V。 b V のさまざまなバイアスでのエネルギーバンド図のシミュレーション結果 d

上記の分析から、 R o TFETの特性は、トンネリングプロセスとチャネル電子熱励起プロセスの両方の影響を受けます。主な物理的メカニズムが R を支配する可能性があります o V でシフト d 変化。最後に、 R o 最初に減少し、次に増加するため、出力特性の非線形性が発生します。ちなみに、図11bを見ると、TGTFETの出力インピーダンスがUTFETやLTFETの出力インピーダンスよりもはるかに小さいことがわかります。これは、TGTFETのデュアルソースおよびラテラルゲートオーバーラップ構造によるトンネリング効率の向上によるものです。

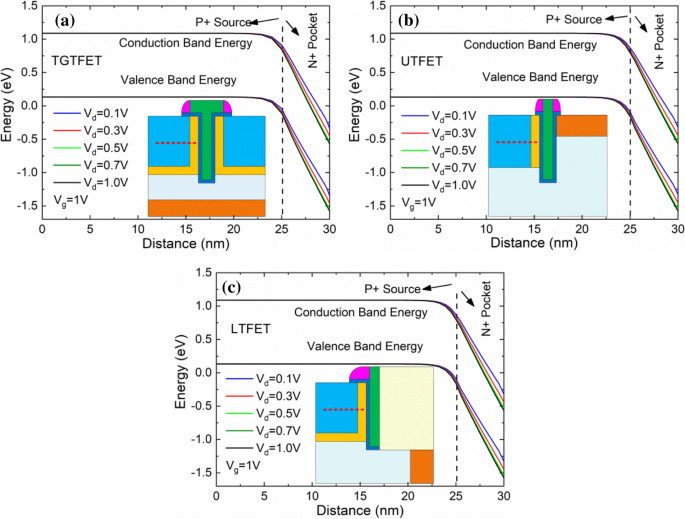

図13は、異なる印加電圧でのTGTFET、UTFET、およびLTFETのエネルギーバンド構造を示しています。挿入図の赤い点線は、エネルギーバンドを描画する位置を表しています(これは、ソース領域の1/2の高さで、表面から15 nm下にあります)。 V で d 0.1Vから0.5Vに増加すると、TGTFET、UTFET、およびLTFETのバンド構造には明らかな曲げ傾向があります。これは、ドレイン電圧がドレイン側近くのトンネル接合部の電位を引き下げる可能性があるためです。これは、TGTFET、UTFET、およびLTFETの場合、 V の増加を示しています。 d 0.1〜0.5 Vは、トンネリング効率に役立ちます。ただし、 V の場合 d > 0.5 V、 V によるエネルギーバンドの変化 d 増加は言及する価値がありません。これは、図12bの分析結果と一致しています。

a のエネルギーバンド構造 TGTFET、 b UTFET、および c V でのLTFET g =1

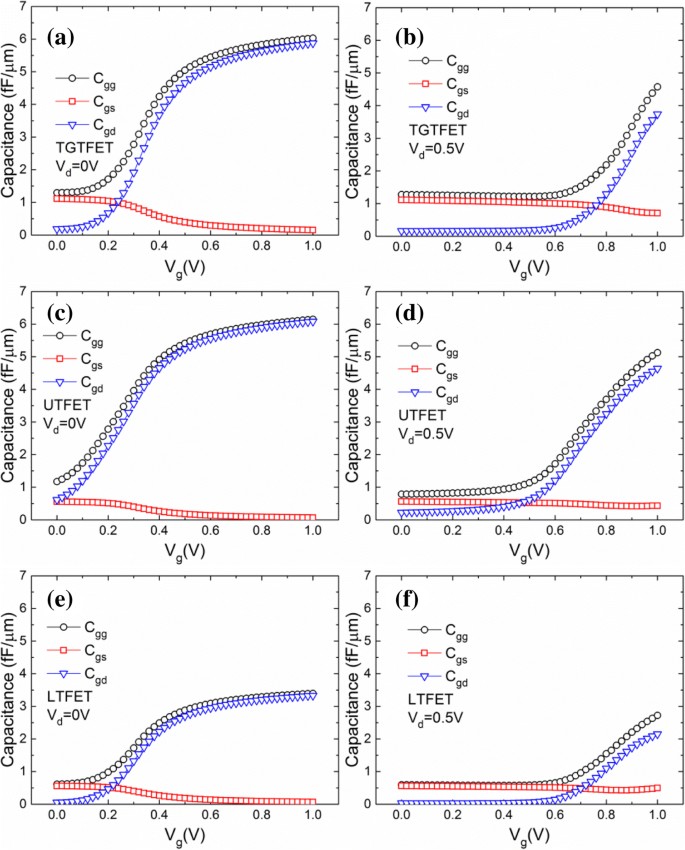

ご存知のように、ゲート容量( C gg )デバイスの周波数特性に大きな影響を与える可能性があります。 TGTFET、UTFET、およびLTFETの場合、 C gg 通常、 C で構成されます gs (ゲートからソースへの容量)および C gd (ゲートからドレインへの容量)。したがって、 C の特性 gg 、 C gs 、および C gd デバイスの周波数特性とアナログアプリケーション能力を評価するために非常に重要です。特にTFETの場合、容量特性はMOSFETとはかなり異なります。ソース領域にトンネル接合が存在するため、TFETの C は通常小さいです。 gs [1、11]。したがって、 C gg TFETのは主に C によって決定されます gd 。図14は、TGTFET、UTFET、およびLTFETの静電容量と V の関係を示しています。 g V の下 d =0.5Vおよび V d =0 V、別途。

TGTFETの静電容量と V g a の下 V d =0Vおよび b V d =0.5V.UTFETの静電容量と V g c の下 V d =0Vおよび d V d =0.5V.LTFETの静電容量と V g e の下 V d =0Vおよび f V d =0.5 V

図14a、bを観察すると、 C であることが簡単にわかります。 gs 1 Vゲート電圧でのTGTFETの電圧は、 V で0.15fF /μmです。 d =0Vおよび V で0.7fF /μm d =0.5 V、これは C よりもはるかに小さい gd ( V で5.8fF /μm d =0Vおよび V で3.7fF /μm d =0.5 V)。したがって、 C gg TGTFETのは主に C によって決定されます gd 。 V の場合 d =0 V、 C gg および C gd V の増加に伴って急速に増加します g 、図14aに示すように。これは、 V の増加に伴い g 、電子はデバイスチャネルのゲート界面に凝集し、静電容量が急速に上昇します。 V の場合 d =0.5 V、 C gd V まで明らかに増加しません g 図14bに示すように、は0.6Vを超えて増加します。これは、 V の場合 g は低く、トンネリングジャンクションを通過してチャネルに入ることができる幸運な電子はごくわずかです。これらの幸運な電子のいくつかは再結合プロセスに参加し、他のほとんどは0.5Vのドレイン電圧のためにドレインによって急速に収集されます。したがって、これらの幸運な電子がデバイスチャネルに留まるのは非常に困難です。ただし、 V では g 増加すると、幸運な電子の数が急速に増加します。現時点では、ドレイン収集も電子正孔再結合プロセスも、これらの幸運な電子を急速に枯渇させることはできません。したがって、チャネル内の電子濃度が増加し、静電容量が急速に増加します。その結果、 V の間、静電容量特性曲線は右にシフトする傾向があります。 d 図14a、bに示すように、増加します。上記の分析と現象は、図14c–fに示すように、UTFETとLTFETにも当てはまります。さらに、0Vおよび0.5VでのUTFETのゲート容量 V d それぞれ6.2fF /μmと5.1fF /μmに達し、LTFETのそれはそれぞれ3.4 fF /μmと2.7fF /μmに達しました。

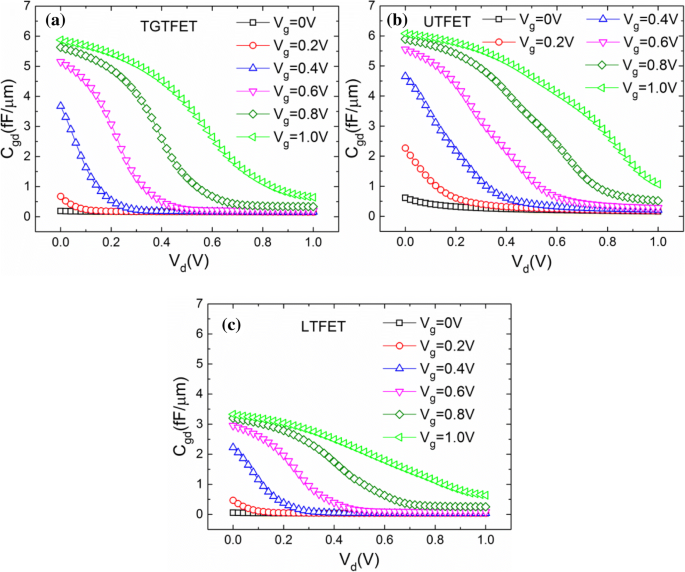

LTFETのゲートとドレインの間に直接の重なりがなく、ゲートとドレイン間の距離が比較的遠いため、LTFETの静電容量特性は最高で C は最小です。 gg 。対照的に、UTFETのゲートとドレインの間には直接重なりがあります。したがって、ドレイン側付近の電子はゲートによって制御されやすくなり、結果として C が大きくなります。 gg UTFETの。 TGTFETの場合、ゲートとドレイン間の距離は近いですが、ゲートとドレインを分離できる低濃度のチャネル領域があります。したがって、TGTFETの静電容量はUTFETの静電容量よりも優れていますが、LTFETよりもわずかに劣っています。図15は、 C を示しています gd V に対するTGTFET、UTFET、およびLTFETの特性 d 異なる V g 。図15a–vを観察すると、 C を見つけるのは難しくありません。 gd これら3つのデバイスの特性は似ています。つまり、固定の V の場合 g 、 C gd V の増加とともに減少します d 。一方、固定の V の場合 d 、 C gd V の増加とともに増加します g 。

C gd a の特徴 TGTFET、 b UTFET、および c LTFETと V d 異なる V g

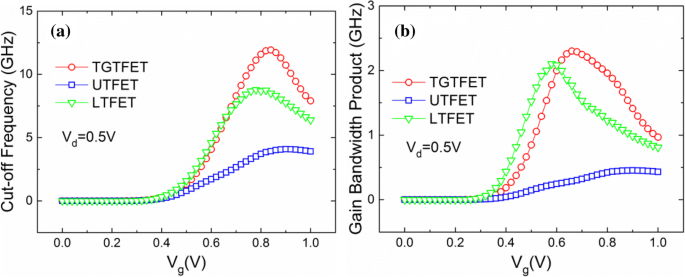

ご存知のように、両方のカットオフ周波数( f T )とゲイン帯域幅(GBW)は、デバイスの周波数特性を評価するための評価基準です。 f T g の比率に依存します m C へ gg 、式に示すように。 (3)[30、31]。 10に等しい特定のDCゲインの場合、GBWは g の比率で表すことができます。 m C へ gd 、式に示すように。 (4)[17]:

$$ {f} _T =\ frac {g _ {\ mathrm {m}}} {2 \ pi {C} _ {\ mathrm {gs}} \ sqrt {1 + 2 {C} _ {\ mathrm {gd} } / {C} _ {\ mathrm {gs}}}} \ approx \ frac {g _ {\ mathrm {m}}} {2 \ pi \ left({C} _ {\ mathrm {gs}} + {C } _ {\ mathrm {gd}} \ right)} =\ frac {g _ {\ mathrm {m}}} {2 \ pi {C} _ {\ mathrm {gg}}} $$(3)$$ \ mathrm {GWB} ={g} _ {\ mathrm {m}} / 2 \ pi 10 {C} _ {\ mathrm {gd}} $$(4)図16は、 f の特性曲線を示しています。 T およびTGTFET、UTFET、およびLTFETのGBW。 T字型ゲートによって導入されたデュアルソースおよびラテラルゲートオーバーラップなどの構造上の利点を利用して、TGTFETはUTFETおよびLTFETと比較して最も優れた周波数特性を取得します。 V の条件下で d =0.5 V、 f T TGTFETのGBWとGBWは、それぞれ最大値の11.9GHzと2.3GHzに達しました。ゲートとドレイン間の距離が長く、ゲート/ドレインのオーバーラップがないという利点により、LTFETは小さな C を取得します。 gg そして良い周波数特性。 f T LTFETのGBWは、それぞれ8.7GHzと2.1GHzに達します。 UTFETの容量特性はTGTFETやLTFETに比べて劣っています。これは、直接ゲート/ドレインがオーバーラップするためです。その結果、 f の最大値 T UTFETのGBWは、4.1GHzと0.5GHzに別々にしか到達できません。

a の特性曲線 f T および b V に対するTGTFET、UTFET、およびLTFETのGBW g V で d =0.5 V

結論

本論文では、良好な性能を備えたT型ゲートデュアルソーストンネル電界効果トランジスタ(TGTFET)を提案し、調査した。構造、メカニズム、およびTGTFETの特性に対するデバイスパラメータの影響について説明します。さらに、TGTFET、UTFET、およびLTFETの特性について説明し、このホワイトペーパーで比較します。トンネルジャンクションの面積を2倍にするために、デュアルソース領域が導入されています。ゲートオーバーラップとn +ポケットは、TGTFETのトンネル接合のトンネル効率を明らかに向上させることができます。最後に、印象的な特性を備えたTGTFET( I オン =8.1×10 −5 A /μm、 I オン / 私 オフ =6.7×10 10 およびSS min =24.4 mV / dec)が得られます。同時に、TGTFETはDIBLに対して堅牢です。つまり、TGTFETは、より広い印加電圧ダイナミックレンジで良好で安定した性能を発揮できます。さらに、TGTFETのアナログ/ RF性能が研究され、UTFETおよびLTFETと比較されます。入出力特性、静電容量特性、GBW、 f などの重要なパラメータ T 分析されます。ゲートとドレインが直接重なり合わないという利点により、TGTFETは比較的小さな C を取得します。 gd および C gg 。最後に、顕著な周波数特性( f )を備えたTGTFET T =11.9GHzおよびGBW =2.3 GHz)が得られます。結論として、TGTFETは、低電力およびアナログ/ RFアプリケーションにおける次世代デバイスの有望な代替手段の1つになることが期待されています。

略語

- C gd :

-

ゲートからドレインへの静電容量

- C gs :

-

ゲートからソースへの容量

- f T :

-

カットオフ周波数

- GBW:

-

ゲイン帯域幅

- g ds :

-

出力コンダクタンス

- g m :

-

相互コンダクタンス

- Hc:

-

チャネルレイヤーの高さ

- Hg:

-

ゲート電極の高さ

- Hs:

-

ソースレイヤーの高さ

- LTFET:

-

L字型ゲートトンネル電界効果トランジスタ

- N D :

-

n +ドレインのドーピング濃度

- N P :

-

n +ポケットのドーピング濃度

- N S :

-

p +ソースのドーピング濃度

- N sub :

-

p-基板のドーピング濃度

- R o :

-

出力インピーダンス

- TGTFET:

-

T字型ゲートデュアルソーストンネル電界効果トランジスタ

- Tox:

-

HfO 2 の厚さ ゲート誘電体

- Tp:

-

n +ポケットの厚さ

- UTFET:

-

U字型ゲートトンネル電界効果トランジスタ

- V d :

-

ソース電圧へのドレイン

- V g :

-

ゲートからソースへの電圧

- Wg:

-

ゲート電極の幅

ナノマテリアル