接合電界効果トランジスタ

電界効果トランジスタは、1926年と1933年に米国特許でJulius Lilienfeldによって提案されました(1,900,018)。さらに、Shockley、Brattain、およびBardeenは、1947年に電界効果トランジスタを調査していました。しかし、極端な困難により、代わりにバイポーラトランジスタを発明することになりました。ショックリーの電界効果トランジスタ理論は1952年に発表されました。しかし、材料処理技術は、ジョンアタラが動作するデバイスを製造した1960年まで十分に成熟していませんでした。

電界効果トランジスタ (FET)はユニポーラ デバイス、1種類の電荷キャリアのみを使用して電流を流します。半導体のN型スラブに基づく場合、キャリアは電子です。逆に、Pタイプベースのデバイスは穴のみを使用します。

FETの動作

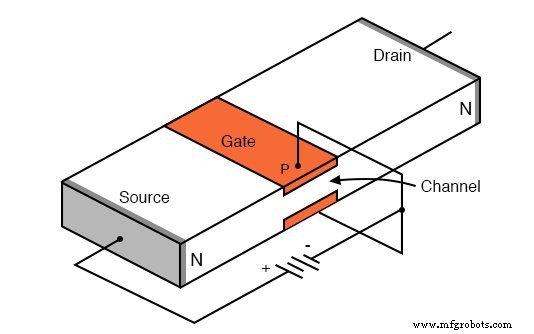

回路レベルでは、電界効果トランジスタの動作は簡単です。 ゲートに印加される電圧 、入力要素は、チャネルの抵抗を制御します 、ゲート領域間のユニポーラ領域。 (下の図)Nチャネルデバイスでは、これは、両端に端子がある、低濃度にドープされたシリコンのN型スラブです。 ソース およびドレイン 端子は、それぞれBJTのエミッタとコレクタに類似しています。 Nチャネルデバイスでは、スラブの中心の両側にある重いPタイプの領域が、制御電極であるゲートとして機能します。ゲートはBJTのベースに類似しています。

「清浄度は敬虔さの次にあります」は、電界効果トランジスタの製造に適用されます。 クリーンルームの外でバイポーラトランジスタを作ることは可能ですが 、電界効果トランジスタの必需品です。このような環境でも、汚染管理の問題があるため、製造には注意が必要です。ユニポーラ電界効果トランジスタは概念的には単純ですが、製造が困難です。今日のほとんどのトランジスタは、集積回路内に含まれる電界効果トランジスタの金属酸化物半導体の種類(後のセクション)です。ただし、ディスクリートJFETデバイスは利用可能です。

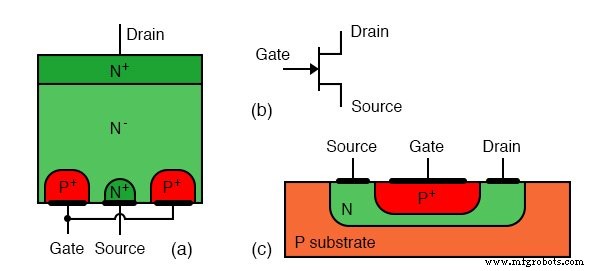

接合型電界効果トランジスタの断面積。

適切にバイアスされたNチャネル接合型電界効果トランジスタ(JFET)を上の図に示します。ゲートは、半導体スラブをドレインするためのソースへのダイオード接合を構成します。ゲートは逆バイアスされています。ソースとドレインの間に電圧(またはオーム計)が印加された場合、N型バーはドーピングのためにどちらの方向にも導通します。導通にはゲートもゲートバイアスも必要ありません。図のようにゲート接合が形成されている場合、逆バイアスの程度によって導通を制御できます。

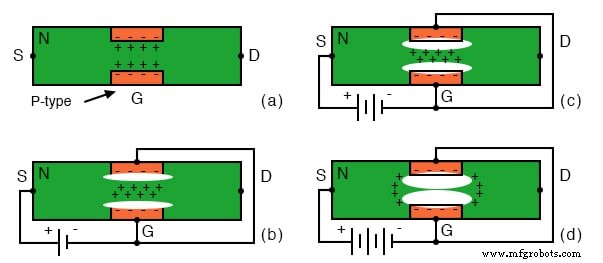

下の図(a)は、ゲート接合部の空乏領域を示しています。これは、P型ゲート領域からN型チャネルへの正孔の拡散によるものであり、接合部に非導電性の空乏領域があり、接合部の周りに電荷が分離します。重いゲートドーピングと軽いチャネルドーピングにより、空乏領域はチャネル側にさらに深く広がります。

NチャネルJFET:(a)ゲートダイオードの空乏。 (b)逆バイアスされたゲートダイオードは空乏領域を増加させます。 (c)逆バイアスを大きくすると、空乏領域が大きくなります。 (d)逆バイアスを増やすとS-Dチャネルがピンチオフします。

空乏領域の厚さは、適度な逆バイアスを適用することにより、上の図(b)で増やすことができます。これにより、チャネルが狭くなるため、ソースからドレインチャネルへの抵抗が増加します。 (c)で逆バイアスを大きくすると、空乏領域が大きくなり、チャネル幅が狭くなり、チャネル抵抗が大きくなります。 (d)で逆バイアスVGSを増やすと、ピンチオフされます。 チャネル電流。チャネル抵抗は非常に高くなります。ピンチオフが発生するこのVGSは、ピンチオフ電圧であるVPです。通常は数ボルトです。要約すると、チャネル抵抗は、ゲートの逆バイアスの程度によって制御できます。

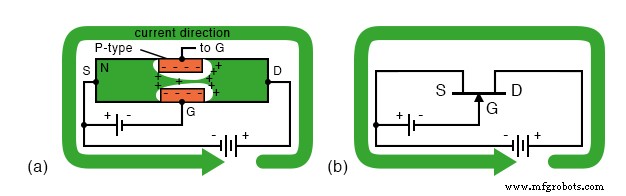

ソースとドレインは交換可能であり、ソースからドレインへの電流は、低レベルのドレインバッテリ電圧(<0.6 V)の場合、どちらの方向にも流れる可能性があります。つまり、ドレインバッテリを低電圧AC電源に置き換えることができます。ドレイン電源電圧が高く、小信号デバイスの場合は数十ボルトの場合、極性は下の図(a)に示すようにする必要があります。このドレイン電源は、前の図には示されていませんが、空乏領域を歪ませ、ゲートのドレイン側で拡大します。これは、数ボルトから数十ボルトまでの一般的なDCドレイン供給電圧のより正確な表現です。ドレイン電圧VDSが増加すると、ゲート空乏領域がドレインに向かって拡大します。これにより、狭いチャネルの長さが長くなり、抵抗が少し増加します。大きな抵抗変化はゲートバイアスの変化によるものであるため、「少し」と言います。下の図(b)は、(a)のシリコン断面と比較したNチャネル電界効果トランジスタの回路図記号を示しています。ゲートの矢印は、接合ダイオードと同じ方向を指しています。

「ポインティング」矢印と「非ポインティング」バーは、それぞれP型とN型の半導体に対応しています。

NチャネルJFET電流は、(a)断面図、(b)概略記号でドレインからソースに流れます。

上の図は、(+)バッテリ端子からFETドレインに流れ、ソースから出て、(-)バッテリ端子に戻る大電流を示しています。この電流の流れは、ゲート電圧を変えることによって制御できます。バッテリーと直列の負荷は、変化するゲート電圧の増幅されたバージョンを確認します。

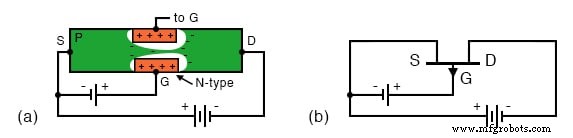

Pチャネル電界効果トランジスタも利用できます。チャネルはPタイプの材料で作られています。ゲートは高濃度にドープされたN型領域です。より一般的なNチャネルデバイスと比較して、Pチャネル回路(下の図)ではすべての電圧源が逆になっています。また、矢印は、Pチャネル電界効果トランジスタの回路図記号(b)のゲートを指していることに注意してください。

PチャネルJFET:(a)N型ゲート、P型チャネル、Nチャネルデバイスと比較した逆電圧源。 (b)回路図の逆ゲート矢印と電圧源に注意してください。

正のゲートバイアス電圧が増加すると、Pチャネルの抵抗が増加し、ドレイン回路に流れる電流が減少します。

ディスクリートデバイスは、下の図に示す断面で製造されています。概略記号に対応するように配向された断面は、半導体ウェーハに対して上下逆になっている。つまり、ゲート接続はウェーハの上部にあります。ゲートは高濃度にドープされており、P +であり、大きな空乏領域のチャネルに正孔を十分に拡散します。このNチャネルデバイスのソース接続とドレイン接続は高濃度にドープされており、接続抵抗を下げるためにN +が使用されています。ただし、ゲートを囲むチャネルは、ゲートからの正孔がチャネル内に深く拡散できるように、軽くドープされています。それがN領域です。

接合型電界効果トランジスタ:(a)ディスクリートデバイスの断面、(b)回路図記号、(c)集積回路デバイスの断面。

集積回路バージョンでは、3つのFET端子すべてがダイの上部で使用できるため、金属化層(図示せず)が複数のコンポーネントを相互接続できます。 (上の図(c))集積回路FETは、高いゲート入力抵抗のためにアナログ回路で使用されます。ゲートの下のNチャネル領域は、ゲート周辺の固有領域がチャネルを制御およびピンチオフできるように、非常に薄くする必要があります。したがって、チャネルの両側にゲート領域は必要ありません。

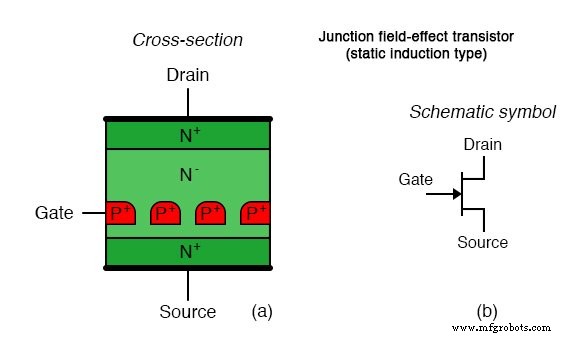

SIT

接合型電界効果トランジスタ(静電誘導型):( a)断面図、(b)回路図記号。

静電誘導電界効果トランジスタ(SIT)は、埋め込みゲートを備えた短チャネルデバイスです。 (上の図)これは、小信号デバイスではなく、パワーデバイスです。ゲート抵抗が低く、ゲートからソースへの容量が小さいため、高速スイッチングデバイスになります。 SITは、数百アンペアと数千ボルトの能力があります。そして、10gHzの信じられないほどの周波数が可能であると言われています。

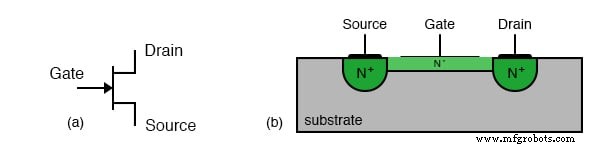

金属半導体電界効果トランジスタ(MESFET):( a)概略記号、(b)断面図。

MESFET

金属半導体電界効果トランジスタ(MESFET) ゲートが接合ダイオードではなくショットキーダイオードであることを除けば、JFETに似ています。 ショットキーダイオード より一般的なオーミック接触と比較した、半導体への金属整流接触です。上の図では、ソースとドレインが高濃度にドープされています(N +)。チャネルは低濃度にドープされています(N-)。 MESFETはJFETよりも高速です。 MESFETは、JFETのように、通常はオンになっている空乏モードデバイスです。 30gHzまでのマイクロ波パワーアンプとして使用されます。 MESFETは、シリコン、ガリウムヒ素、リン化インジウム、炭化ケイ素、および炭素のダイヤモンドアロトロープから製造できます。

レビュー:

- ユニポーラ接合型電界効果トランジスタ(FETまたはJFET)は、チャネル内の伝導が1つのタイプのキャリアに起因するため、このように呼ばれます。

- JFETのソース、ゲート、およびドレインは、それぞれBJTのエミッタ、ベース、およびコレクタに対応します。

- ゲートに逆バイアスをかけると、ゲートダイオードの空乏領域が拡大してチャネル抵抗が変化します。

関連するワークシート:

- 接合型電界効果トランジスタ(JFET)ワークシート

産業技術