ソース接点とドレイン接点の距離がわずか2nmの高性能長方形ゲートUチャネルFET

要約

この論文では、ソース接点とドレイン接点の間の極端な積分距離のための新しい高性能長方形ゲートUチャネルFET(RGUC FET)を提案します。 RGUC FETは、ソース/ドレイン(S / D)接点間の距離が2 nmに減少するまで、ほぼ理想的なしきい値以下の特性を示します。他の凹型またはU字型チャネルベースのFETとは異なり、ゲート接点は凹型領域に形成する必要はありませんが、Uチャネルの両側の2つの垂直部分間の絶縁のためにスペーサーの層にのみ形成する必要があります。その構造上の利点により、ソース接点とドレイン接点の間の極端な集積距離のためのより高い集積度を備えた集積回路の製造に適用することが可能になります。 RGUC FETの電気的特性は、S / D接点間の水平距離、S / D領域の延長高さ、ゲート酸化物層の厚さと材料などの設計パラメータの影響を調査することによって綿密に調査されました。 RGUC FETの電気的特性は、量子シミュレーションによって検証されます。他の非プランナーチャネルマルチゲートFETと比較して、新しいRGUCFETはより高度な統合に適しています。

はじめに

ナノスケール集積回路(IC)で使用される最も有望なデバイスの1つとして、従来の接合ベースの金属酸化膜半導体(MOS)FETに加えて、優れた電気的特性を示す接合なし電界効果トランジスタ(JL FET)その製造の単純さは、近年深く研究されてきました[1,2,3,4]。ゲート電圧を上げるとチャネル内に蓄積領域が形成され、オン電流が大きくなります[5]が、マルチゲート(MG)FETの導入により、ゲート電圧からのソースからドレインへの電流の制御性が強化されました。デバイスのはるかに優れたサブスレッショルドプロパティに。ジャンクションレスマルチゲート(JL MG)FETも、長年にわたって広く研究されてきました[6、7、8]。垂直チャネルゲートオールアラウンドMOSFETは、ほぼ理想的な I を示していますが - V 半径がわずか数ナノメートルの性能では、その垂直チャネルがソースとドレインの接触を同じ層で製造できなかったため、ICのレイアウトがプランナーテクノロジーと互換性がなくなりました。さらに、半導体製造はチャネル長を10 nm未満に縮小することを余儀なくされているため、MGFETは再び短チャネル効果に直面します[9、10、11]。短チャネル効果を克服するために、埋め込みチャネルMOSFETは近年ホットな話題になっています[12、13、14、15、16]。凹型チャネルMOSFETのモデリングとシミュレーション作業も包括的に実行されます[17、18、19、20]。凹型チャネルMOSFETには、ソース接点とドレイン接点の両方の下にプランナー垂直チャネル部品と水平平面チャネル部品の両方があります。実際には、水平平面チャネルのみを備えた従来のMOSFETと比較して、実効チャネル長が長くなりました。ソース接点とドレイン接点の距離が同じであるデバイスの場合、平面チャネルを備えた従来のMOSFETと比較して、短チャネル効果の影響を受けにくくなります。ただし、実験データは、リセスチャネルを備えたMOSFETのサブスレッショルドスイングでは、実効チャネル長が100nm未満の理想的なサブスレッショルドスイングを実現できないことを示しています。これは、チャネル長は長くなりますが、MGFETのようにゲート制御性が向上しないためです。チャネル長ではなく、積分の記述に関連する新しい主要な幾何学的パラメータを定義する方がよいことに注意してください。ナノスケールデバイスの設計の最終目標は、限られた特定のチップ領域で最高のパフォーマンスを実現することであり、実際のデバイスサイズはチャネル幅に関連しているため、ソース接点とドレイン接点の間の距離はより現実的かつ効果的です。ソース接点とドレイン接点の間の距離。 MG FETと埋め込みチャネルMOSFETの両方の利点を組み合わせるために、以前の研究では、U字型チャネルを備えた鞍型ゲートFETを提案しました[21、22、23]。これにより、水平方向へのゲート制御性が向上します。平面シングルゲートタイプから3Dトリプルゲートタイプへの凹型チャネルのチャネル部分。その後、水平チャネル部分だけでなく、両方の垂直チャネル部分で形成されたこの3Dトリプルゲート機能をアップグレードします。このデバイスはHゲートUチャネルFETと呼ばれ、凹型チャネルもそれに応じて3DU字型チューブチャネルにアップグレードされます[24]。上記のように、ナノスケールデバイスの設計の最終的な目標は、最適化を通じて、限られた特定のチップ領域で最高のパフォーマンスを実現することです。最適化された高性能デバイスを実現するには、ゲート構造と対応するチャネル構造の両方を十分に検討して設計する必要があります。また、製造の複雑さも十分に考慮する必要があります。凹型チャネルデバイス、以前に提案されたサドルFET、およびHGUC FETなどの上記のデバイスは共通のグラウンドを持っており、ゲート酸化物/ゲート/ゲート酸化物のサンドイッチ構造が小さな凹んだ領域にうまく形成されるべきである。この構造的特徴は、統合のさらなる促進を制限します。統合を促進する良い方法は、凹んだ領域の構造的特徴を単純化し、U字型チャネルの垂直チャネル部分と水平チャネル部分へのゲート制御能力を同時に維持することであると思われます。これらのデバイスの特徴と機能を実現するために、本論文では、ソース接点とドレイン接点の間の極端な統合距離のための新しい長方形ゲートUチャネルFET(RGUC FET)を提案しました。それは、ソースとドレインの接点間の距離を増やすことなく、エフェクトチャネルの長さを延長できるU字型のチャネルを備えています。他のU字型チャネルFETと比較して、RGUC FETは、U字型チャネルのくぼんだ領域でより単純な内部構造を備えています。その後、くぼんだ領域の内部でより簡単な製造を実現し、ソースとドレインの接点間の距離を短くすることができます(より高い統合)。提案された構造は、より高い I を伴う、より優れたゲート制御性とより小さな逆リーク電流を備えています。 オン / 私 オフ 比。ソース接点とドレイン接点の間の距離は、2nm未満に縮小できます。全体の電気的特性は、量子シミュレーションによって分析されます。

メソッド

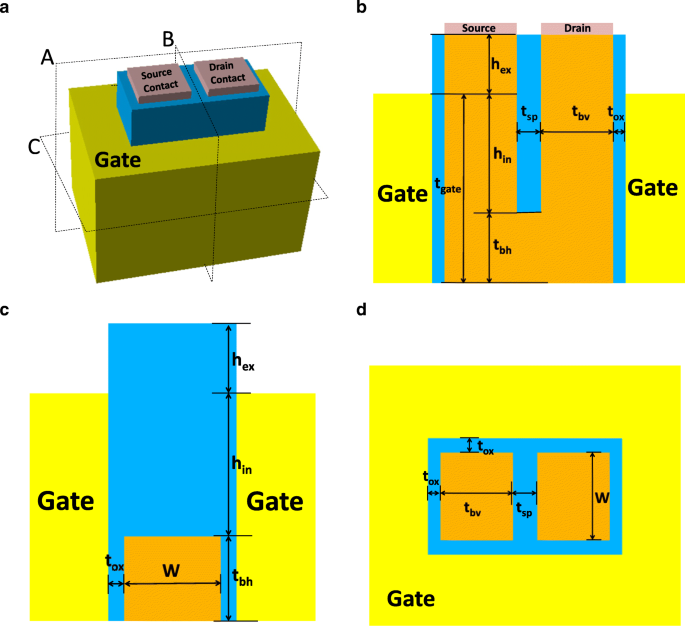

図1aはRGUCFETの3D概略図を示し、図1bからdは、図1aに示されている平面A、B、C、およびDを切断したデバイスのプロファイルです。 W はシリコンの本体幅、 t b はシリコンの本体の厚さ、 h in は、くぼんだ領域のスペーサーの内側の高さ、 h ex は拡張ソース/ドレイン領域の高さ、 t ox はシリコン本体の周りのゲート酸化物の厚さであり、 t sp は、U字型チャネルのくぼみ領域に堆積された絶縁体層のスペーサーの厚さであり、ソース接点とドレイン接点の間の距離に等しくなります。

a RGUCFETの3D概略図。 b a の平面Aを切断したデバイスのプロファイル 。 c a の平面Bを切断したデバイスのプロファイル 。 d a の平面Cを切断したデバイスのプロファイル

シリコン本体の厚さは6nm未満であるため、より正確なシミュレーション結果を得るために、従来のシミュレーションの代わりに量子シミュレーションをこの論文で紹介します。すべてのシミュレーションは、SILVACO Atlas 3DデバイスシミュレーションのTCADを使用して、濃度依存モビリティモデル、濃度依存Shockley-Read-Hallモデル、Auger再結合モデル、バンドギャップナローイングモデル、標準のバンド間トンネリングモデルを使用して実行されます。ボーム量子ポテンシャルモデル[25]。シミュレーションパラメータを表1に示します。2つの垂直ボディパーツは実際には4つの側面を持つ立方体であり、その上面はソースまたはドレイン領域で覆われ、下面は両方とも水平ボディパーツに接続されています。垂直ボディパーツの外側の三重の側面は、ゲート酸化物と長方形のゲート接点で囲まれ、もう一方の内側は、くぼんだ領域で内側のスペーサーに接続されています。水平ボディの4つの側面はすべて、ゲート酸化物と長方形のゲート接点で囲まれています。上記の構造上の特徴により、長方形のゲートは、水平体と2つの垂直部分の両方に対して強力な電界効果制御能力を持っていると推測できます。また、内部スペーサーは、シリコンのソース接点とドレイン接点の間の最短経路の距離を実際に延長しました。これにより、平面チャネル機能を備えたマルチゲートデバイスでは避けられない短チャネル効果を排除できます。他の3Dチャネルデバイス[21、22、23、24]と比較して、提案された構造は凹領域にゲートを形成する必要がないため、凹領域の内部構造の複雑さが大幅に軽減されます。

<図>結果と考察

ボーム量子ポテンシャル(BQP)モデルは、量子力学のボーム解釈から導出された補助方程式を使用して、位置に依存するポテンシャルエネルギー項を計算します。このモデルは純粋な物理学から派生しており、モデルがさまざまなクラスのデバイスやさまざまな材料の量子挙動を近似できるようにします。 I を含むデバイス性能に対する量子閉じ込めの影響 - V 特性は、適切な近似値に計算されます。以前の研究では、酸化物の厚さが0.5 nmを超える場合、ゲートリーク電流は無視できることが示されています[7、26]。

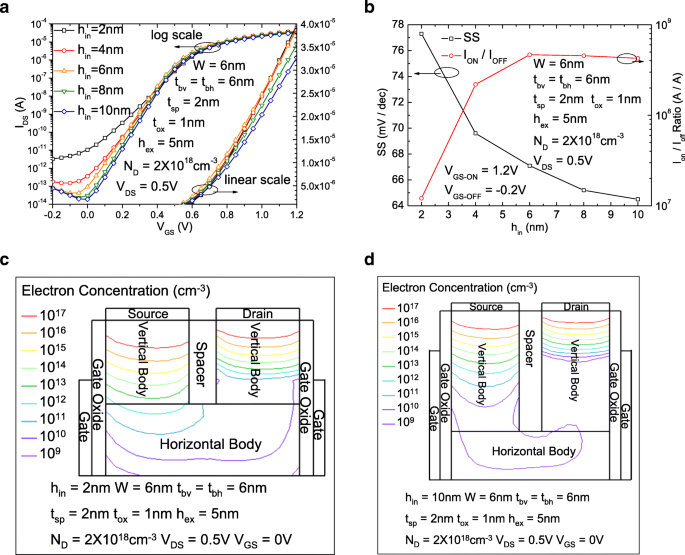

図2aは、ドレイン-ソース間電流ゲート-ソース間電圧( I )の比較を示しています。 DS - V GS )異なる h のRGUCFETの特性 in ■対数目盛と線形目盛の両方。図2bは、サブスレッショルドスイング(SS)と I の比較を示しています。 オン / 私 オフ h が異なるRGUCFETの比率 in s。 h の増加に伴い in 、ソースからドレインまでのチャネル全体の垂直経路が連続的に増加し、次に最短有効チャネル長が徐々に増加し、短チャネル効果が徐々に弱まり、最終的に排除されます。 SSは、 h に対して65mV / decのほぼ理想的な値を実現できます。 in 10nmに達します。 私 オン / 私 オフ h の比率も約35倍になります in SSが継続的に減少するため、2から10nmに増加します。長時間の h in ソースからドレインまでの最短経路の距離が6から22nmに増加します。これは、2 h に相当します。 in + t sp 提案された構造の実効チャネル長に相当します。図2cおよびdは、2nmおよび10nm h のデバイスのオフ状態でのシリコン本体の2次元電子濃度分布を示しています。 in 、 それぞれ。 2 nmの場合、体の水平領域での最高電子濃度は約10 12 です。 cm -3 ソース/ドレイン接点と水平ボディ領域の間の距離は非常に短いです。その後、ソース/ドレインバイアスは水平体領域の電子分布に深刻な影響を及ぼします。解決策は、ソース/ドレインを水平ボディ領域から遠ざける垂直チャネルを延長することです。 10 nmの場合、図2dでは、水平体領域の最高電子濃度が10 9 まで減少していることがわかります。 cm -3 、そしてそれはオフ状態にとってより理想的な完全空乏領域を作り、それははるかに低いレベルの漏れ電流をもたらします。

a I の比較 DS - V GS h が異なるRGUCFETの特性 in ■対数目盛と線形目盛の両方。 b サブスレッショルドスイング(SS)と I の比較 オン / 私 オフ h が異なるRGUCFETの比率 in s。 c 2 nm h のデバイスのオフ状態のシリコン本体の2次元電子濃度分布 in 。 d 10 nm h のデバイスのオフ状態のシリコン本体の2次元電子濃度分布 in

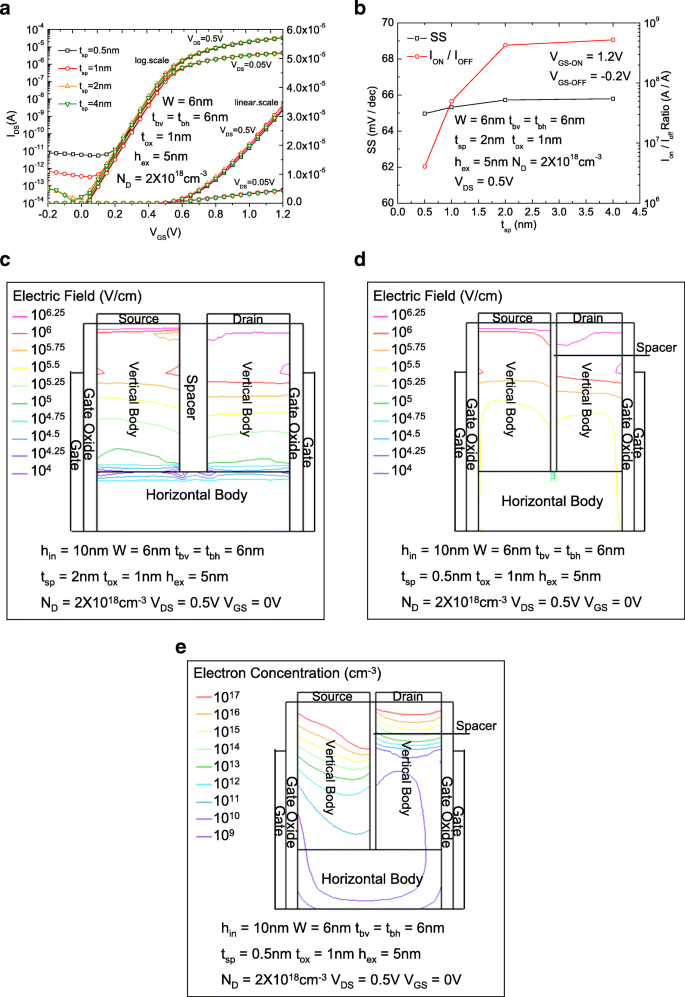

図3aは、 I の比較を示しています DS - V GS t が異なるRGUCFETの特性 sp ■対数目盛と線形目盛の両方。図3bは、サブスレッショルドスイング(SS)と I の比較を示しています。 オン / 私 オフ t が異なるRGUCFETの比率 sp s。 t の減少に伴い sp 、ソース接点とドレイン接点の間の距離も継続的に減少します。漏れ電流は主にバンド間トンネル電流によって引き起こされます。トンネリング確率はバンドベンディングに比例し、特定のポイントでの電界強度に相当します。総トンネル電流は、身体領域の各ポイントで生成されたトンネル電流の合計です。

a I の比較 DS - V GS t が異なるRGUCFETの特性 sp ■対数目盛と線形目盛の両方。 b サブスレッショルドスイング(SS)と I の比較 オン / I オフ t が異なるRGUCFETの比率 sp s。 c 2 nm t のデバイスのオフ状態のシリコン本体の2次元電界分布 sp 。 d 0.5 nm t のデバイスのオフ状態のシリコン本体の2次元電界分布 sp 。 e 0.5 nm t のデバイスのオフ状態のシリコン本体の2次元電子濃度分布 sp

図3cと図2dは、2nmと0.5nm t のデバイスのオフ状態でのシリコン本体の2次元電界分布を示しています。 sp 、 それぞれ。スペーサーの厚さが大きい場合、またはドレイン-ソース間電圧( V )が小さい場合 DS )バイアス、凹んだ領域のスペーサー間の界面の電界強度は、大量の漏れ電流を生成するのに十分な強さではありません。最も強い電界強度は、ゲート酸化物と垂直体部分の間の界面の近くに現れます。これは、 V によって決定されます。 GD 。ただし、ソースからドレインまでの距離が1 nm未満(ゲート酸化物の厚さ未満)に減少すると、最も強い電界強度が、凹んだ領域のスペーサーと2つの垂直な身体部分との間の界面近くに現れます。 t のとき sp V が大きい場合は、1nm未満です。 DS (たとえば0.5 V)、リーク電流はゲートバイアスとほとんど無関係であり、主に V によって決定されます。 DS 。 SSは t とほぼ独立しています sp h の間65mV / decのほぼ理想的な値を維持します in =10nmの場合 t まで sp 2nm未満です。 私 オン / 私 オフ 比率は10 8 を維持します t まで sp =2 nmであり、 t の間深刻に劣化します sp 強い電界によって引き起こされる漏れ電流の増加による2nm未満は、凹んだ領域のスペーサーと2つの垂直な身体部分との間の界面の近くに現れます。ボディ領域のシリコンボディの電界強度は、0.5 nm t で包括的に強化されます。 sp 場合。図3eは、0.5 nm t のデバイスのオフ状態でのシリコン本体の2次元電子濃度分布を示しています。 sp 。図2dと比較すると、体の水平領域の電子濃度が10 9 から拡大していることがはっきりとわかります。 〜10 10 cm -3 。また、スペーサーの厚さが0.5 nmの寸法は単一分子層に非常に近いため、スペーサー層の絶縁性がある程度損なわれる可能性があります。上記の理由により、 t sp 高積分および低リークの低消費電力設計では、2nmにすることをお勧めします。

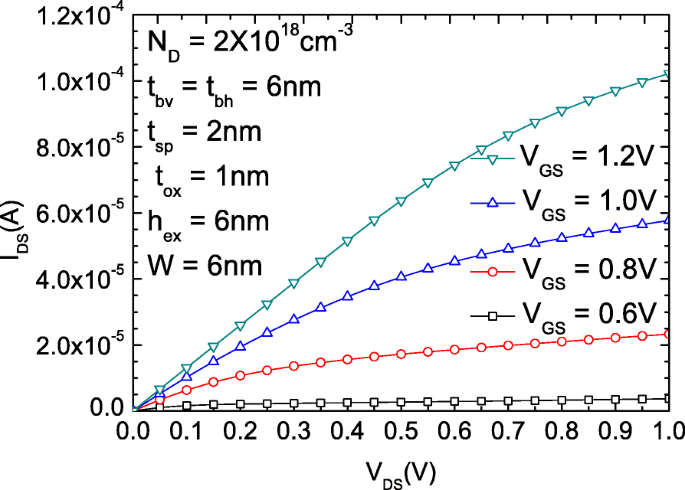

図4は、 I を示しています DS - V DS 異なる下で最適化された構造を持つ提案されたRGUCFETの例。

私 DS - V DS 最適化されたデバイスパラメータを備えた提案されたRGUCFETの特性

V GS 値、SSは約63 mV / dec、および I オン/ 私 オフは10 9 〜10 10 。飽和電流は V として増加します GS 増加します。

結論

この論文では、高い積分と高性能を備えた新しいRGUC FETを提案します。これは、低いサブスレッショルドスイングと高い I を示します。 オン / 私 オフ 比。ソース/ドレイン(S / D)接点間の距離は2 nmに短縮でき、SS、逆リーク電流、 I などのほぼ理想的な特性を備えています。 オン / 私 オフ 比。より正確な結果を保証するために、すべての電気的特性が量子モデルでシミュレートされます。

略語

- BQP:

-

ボーム量子ポテンシャル

- FET:

-

電界効果トランジスタ

- h ex :

-

S / D領域間のスペーサーの延長高さ

- h in :

-

凹んだ領域のスペーサーの内側の高さ

- I オフ :

-

オフ電流

- I オン :

-

現在

- JL:

-

ジャンクションレス

- MOS:

-

金属酸化物半導体

- N D :

-

ドーピング濃度

- RGUC:

-

長方形ゲートUチャネル

- S / D:

-

ソース/ドレイン

- SS:

-

サブスレッショルドスイング

- t bh :

-

水平方向の体の厚さ

- t bv :

-

縦の体の厚さ

- t ゲート :

-

ゲートの垂直方向の長さ

- t ox :

-

ゲート酸化物層の厚さ

- t sp :

-

S / D領域間のスペーサーの厚さ

- V DS :

-

ドレイン-ソース間電圧

- V GS :

-

ゲート-ソース間電圧

- W:

-

体幅

ナノマテリアル

- 構造体とクラスの違い:C++ の例で説明

- while と do-while の違い:例で説明

- 高度な農薬活性を備えたスマートナノマテリアルおよびナノコンポジット

- 低抵抗Auオーミックコンタクトを備えた多層SnSeナノフレーク電界効果トランジスタ

- アスペクト比が異なり、高性能で柔軟な透明電極として使用される銀ナノワイヤーの容易な合成

- 電気抵抗率の低いUV硬化インクジェット印刷された銀ゲート電極

- アルゴンプラズマ処理によるZnOの挿入による金属とn-Ge間の接触抵抗の低減

- V溝キャビティを備えたチャネルプラズモンナノワイヤレーザー

- マトリックスとフィラー間の界面接触レベルが満たされているグラフェン支援熱界面材料

- リチウムイオン電池用のカーボンナノチューブとグラフェンで修飾されたFeF3・0.33H2Oの高性能カソード材料

- 2DEGチャネルとパターン化基板を備えた新しいGaNナノピラー垂直電界効果トランジスタ(FET)のバリガの性能指数(BFOM)強化について