強化されたデュアルゲートと部分的なP埋め込み層を備えた超低比オン抵抗横方向二重拡散金属酸化物半導体トランジスタ

要約

超低比オン抵抗( R on、sp )強化されたデュアルゲートと部分的なP埋め込み層を備えた横方向二重拡散金属酸化物半導体トランジスタ(LDMOS)を提案し、この論文で調査した。提案されたLDMOSのオン抵抗解析モデルは、ドリフト領域の抵抗とチャネル領域の抵抗の関係についての詳細な洞察を提供するために構築されています。 N埋め込み層は、Pウェルの下に導入され、低抵抗の伝導経路を提供し、チャネル領域の抵抗を大幅に低減します。強化されたデュアルゲート構造は、オフ状態での垂直パンチスルー破壊を回避しながら、N埋め込み層によって形成されます。最適化された長さの部分的なP埋設層がNドリフト領域の下に採用され、垂直空乏領域を拡張し、オフ状態での電界ピークを緩和します。これにより、ドリフト領域の抵抗が低く、絶縁破壊電圧(BV)が向上します。強化されたデュアルゲートおよび部分的なP埋め込み層を備えたLDMOSの場合、結果は R on、sp は8.5mΩ・mm 2 BVは43Vです。

背景

アナログパワーICのより複雑で高速なロジック機能に対する需要の高まりに伴い、横方向の二重拡散金属酸化物半導体トランジスタ(LDMOS)の性能を改善し、特に特定のオン抵抗を最小限に抑えることが重要です( R on、sp )およびオフ状態のブレークダウン電圧(BV)を最大化する[1,2,3,4,5,6,7,8,9]。ほとんどの開発された技術は、 R のトレードオフを改善するためのドリフト領域の最適化に焦点を合わせています on、sp 対LDMOSデバイスのBV [10、11、12、13、14、15、16、17、18、19、20]。以前の研究では、超シャロートレンチアイソレーション(USTI)を備えたLDMOSが提案されました[21]。 USTIの深さとコーナーエンジェルは、クラス最高のパフォーマンスを達成するために最適化されました。ただし、低電圧LDMOSの場合、ドリフト領域は R で支配を失っています。 on、sp チャネル領域の寄与は無視できません。

メソッド

この作業では、強化されたデュアルゲートと部分的なP埋め込み層を備えた新しい超低比オン抵抗LDMOSを調査します。数値シミュレーションでは、物理モデルIMPACT.I、BGN、CONMOB、FLDMOB、SRH、およびSRFMOBが使用されます。ドリフト領域の抵抗とチャネル領域の抵抗の関係についての詳細な洞察を提供するために、オン抵抗分析モデルが提案されています。モデルに基づいて、N埋め込み層と部分P埋め込み層が最適化され、 R が低くなります。 on、sp と高いBV。

結果と考察

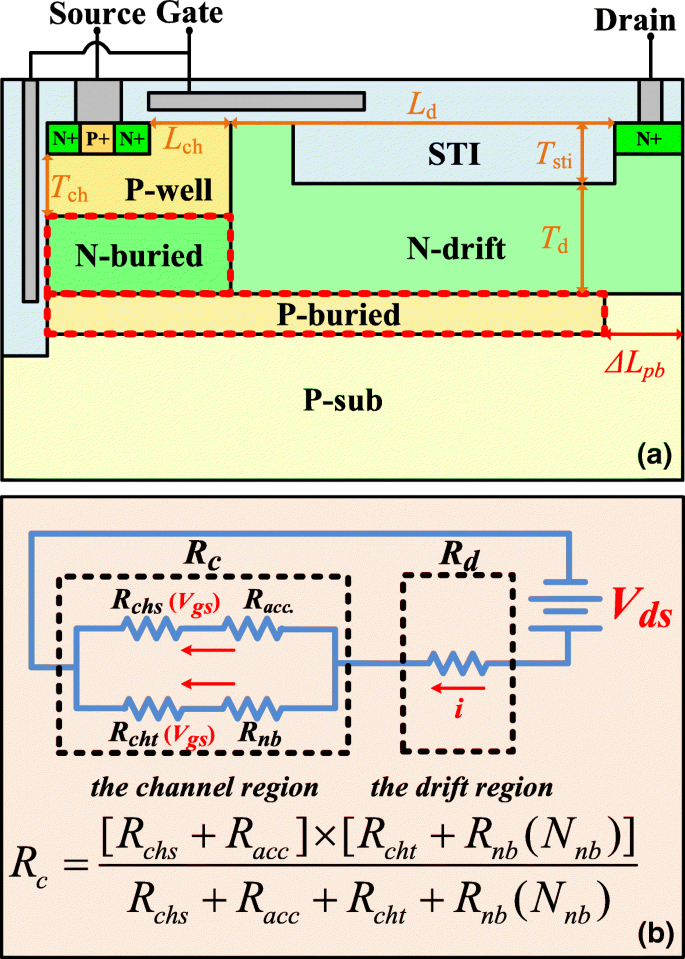

図1aは、強化されたデュアルゲートおよび部分的なP埋め込み層を備えた超低比オン抵抗LDMOSの概略断面図を示しています。 LDMOSは、N埋め込み層と部分的なP埋め込み層を備えたデュアルゲートを備えており、 R の削減に貢献します。 on、sp それぞれBVを強化します。チャネル領域では、強化されたデュアルゲートはトレンチゲートと高濃度にドープされたN埋め込み層によって形成されます。従来のデュアルゲート構造と比較して、N埋め込み層は、オン状態のPウェルの下に低いオン抵抗伝導経路を提供することにより、チャネル領域の抵抗を大幅に低減します。ドリフト領域では、ドーピング濃度の高い部分的なP埋め込み層が、Nドリフト領域の下に導入され、低い R を維持しながらBVを向上させます。 on、sp 。部分的なP埋め込み層は、ドリフト領域の電荷バランスを崩すことなく、オフ状態の垂直電界を低減するのに役立ちます。新しいデバイスのキーサイズを表1に示します。

a 強化されたデュアルゲートおよび部分的なP埋め込み層を備えた超低比オン抵抗LDMOSの概略断面図。 b 提案されたLDMOSの概略等価オン抵抗

図1bは、提案されたLDMOSの概略的な等価オン抵抗モデルを示しています。総オン抵抗は、ドリフト領域の抵抗( R )と見なされます。 d )およびチャネル領域の抵抗( R c ) シリーズで。チャネル領域では、表面チャネル伝導経路はトレンチチャネル伝導経路と平行です。したがって、 R c ( R に等しい chs + R acc )//( R cht + R nb )、ここで R chs 、 R acc 、 R cht 、および R nb は、それぞれ表面ゲートチャネル、蓄積領域、トレンチゲートチャネル、およびN埋め込み層の抵抗です。提案されたオン抵抗モデルに基づいて、 R の削減 c R を減らすことで達成できます nb 他の抵抗は主にプロセス技術、動作電圧、およびしきい値電圧によって決定されるため、他の性能に影響を与えることはありません。 R d 以前の作業で表面フィールドの削減(RESURF)効果を強化するために、Nドリフト領域の下にP埋め込み層を導入することにより、削減されました。この作業では、部分的なP埋め込み層を採用して、低い R を維持しながらBVを改善します。 d 。

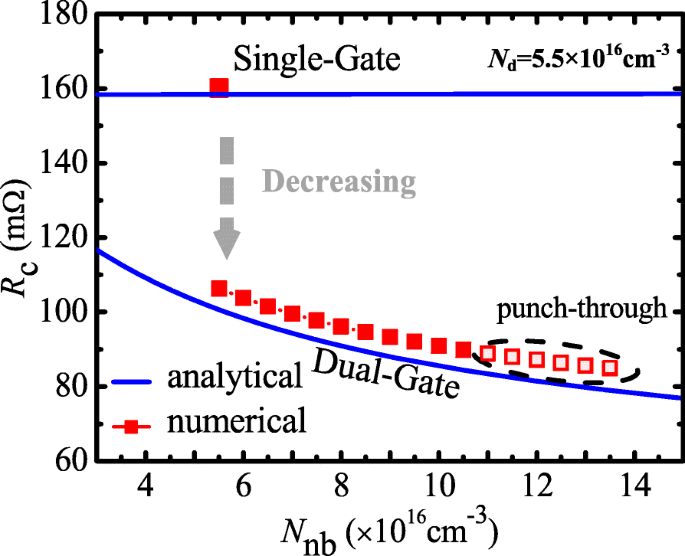

R の削減を目指す c 、高ドーピング濃度のN-埋没層がPウェルの下に導入されます。図2は、数値および分析の R を示しています。 c N埋め込み層のドーピング濃度の関数として( N nb )シングルゲートとデュアルゲート付き。デュアルゲート構造が R の低減に役立つことが示されています c シングルゲートと比較して。 N の場合 nb = N d =5.5×10 16 cm -3 、 R c 110mΩです。オン抵抗モデルによると、 R nb R の主な貢献者です c 。そして、 R nb R を小さくするために減少させることが望ましい c 。図2aに示すように、 R c N で削減されます nb 増加しています。 N の場合 nb =1.35×10 17 cm -3 、 R c 85mΩに減少します。ただし、図2は、 N も示しています。 nb パンチスルーの故障によって制限されます。トレンチゲートを追加したため、 R c N で最初に34%減少します nb = N d =5.5×10 16 cm -3 。 N として nb 増加、 R c 継続的に減少します。最適化された N nb =1.05×10 17 cm -3 、 R c ついに45%減少しました。 N の場合 nb > 1.05×10 17 cm -3 、パンチスルーブレークダウンはPウェルで発生します。 R の分析結果 on、sp 図2に示すように、提案されたモデルは数値シミュレーション結果との良好な適合を提供します。したがって、モデルは最適化設計を導くために信頼できます。

数値的および分析的 R c N の関数として nb シングルゲートとデュアルゲート( Z =1 cm)。 N d はNドリフト領域のドーピング濃度です

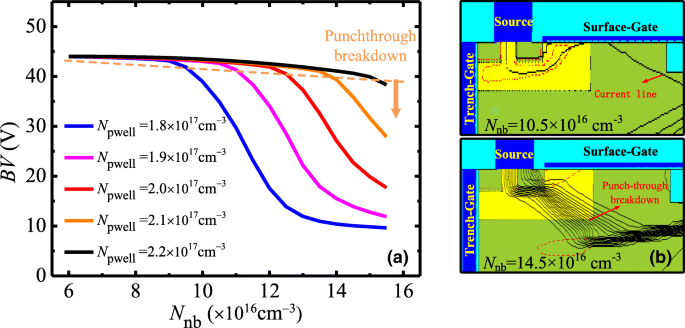

図3aは、 N の関数としての数値BVを示しています。 nb Pウェルのドーピング濃度が異なる場合( N pwell )。 N nb R だけでなく効果もあります c 、だけでなく、BV。特定の N に対して pwell 、BVは小さい N で変化しません nb 、その後、 N で減少します nb 増加しています。 N の場合 nb 1.2×10 17 に増加します cm -3 、BVは N で低下し始めます pwell =2×10 17 cm -3 。 BVの低下は、図3bに示すように、Pウェル領域でのパンチスルー破壊に起因します。ドレイン電圧が上昇すると、Pウェルの空乏領域がソースまで広がります。空乏領域がN + / Pウェル接合部を攻撃すると、パンチスルーブレークダウンが発生します。大きな N の場合 pwell 、枯渇は主にドリフト領域にまで及び、BVを低下させることなくパンチスルー破壊を回避します。高ドーピング濃度のPウェルは、パンチスルーブレークダウンを回避するのに役立ちますが、しきい値電圧が向上します。したがって、 N pwell 2×10 17 cm -3 しきい値電圧とBVと R の間のトレードオフを考慮して選択されます on、sp 。

a N の関数としての数値BV nb 異なる N pwell 。 b N の電流密度プロファイル nb =10.5×10 16 cm -3 および14.5×10 16 cm -3 N pwell =2×10 17 cm -3 故障時

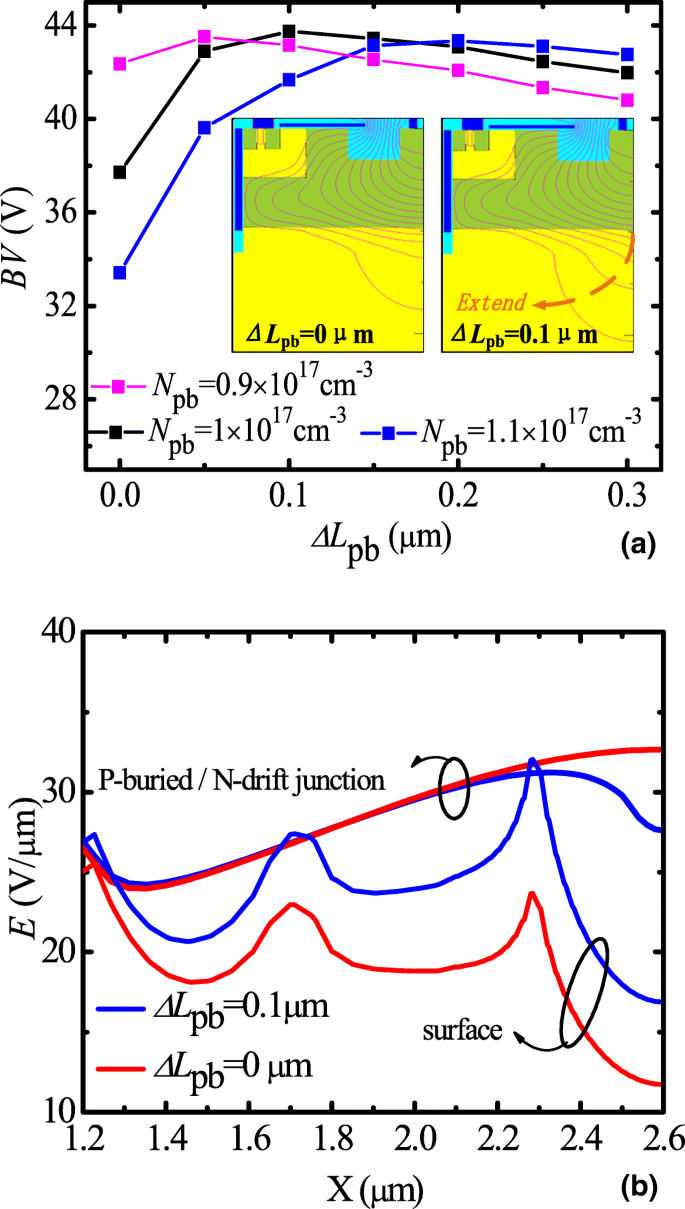

低い R を達成するために d そして、高BVの部分的なP埋没層がNドリフト領域の下に導入されます。図4aは、Δ L の関数としてのBVを示しています。 pb 異なる N pb 。特定の N に対して pb 、Δ L として pb 増加すると、BVが増加し、その後わずかに減少します。 Δ L の場合 pb =0.1μm、 N pb =1×10 17 cm -3 、BVは最大値43 Vに達します。インサートは、 N の等電位コンタープロファイルを示しています。 pb =1×10 17 cm -3 。部分的なP埋没層構造の等高線は、完全なP埋没層と比較して基板まで伸びていることが示されています。図4bは、表面とP埋没/ Nドリフト接合界面での電界分布を示しています。最適化された従来のLDMOSの場合、ブレークダウンは通常、Nドリフト/ P埋め込みインターフェイスで発生します。提案されたLDMOSの場合、N-drift / P-subの接合部がN-drift / P-buriedの接合部に置き換わり、垂直電界を緩和して空乏領域を拡張します。これにより、低い Rを維持しながらBVが高くなります。 d 。

a ΔLの関数としてのBV pb 異なる N pb 。インサートは、 N の等電位コンタープロファイルです。 pb =1×10 17 cm -3 。 b 表面およびP-埋め込み/ N-ドリフト接合界面での電界分布

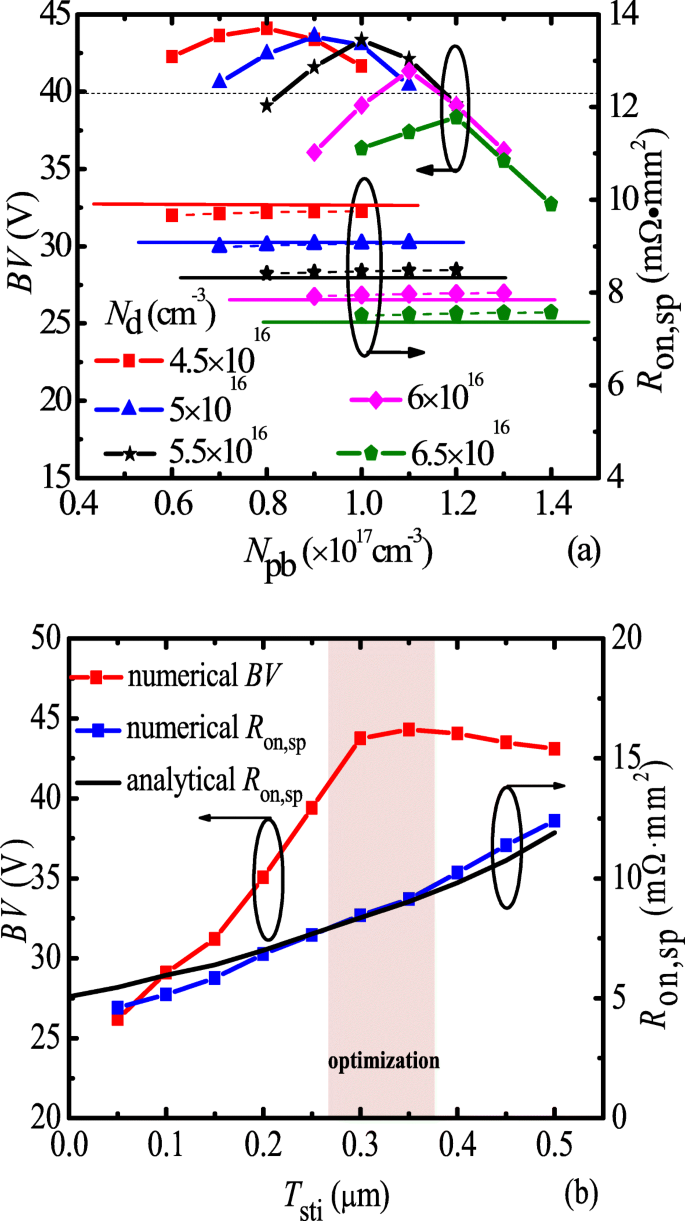

高いBVを達成するには、Nドリフトと部分的なP埋め込み層の間の電荷バランスが必要です。図5aは、数値および分析BVと R を示しています。 on、sp P-埋没物のドーピング濃度の関数として( N pb )さまざまな N d 。特定の N に対して d 、BVは、さまざまな N で最大値を持ちます pb 、および最大 BV N の減少とともに増加します d 。ただし、 R on、sp N として増やすことができます d 減少します。 BV による 40 Vより高い必要がある、 N d =5.5×10 16 cm -3 および N pb =1×10 17 cm -3 が選択されます。図5bは、数値および分析のBVと R を示しています。 on、sp STI層の厚さの関数として( T sti )。 T sti BVと R に強い影響を与えます on、sp 、そしてそれは私たちの以前の仕事[21]と同様に注意深く設計され、最適化されるべきです。 T の場合 sti <0.3μm、ポリフィールドプレートのエッジの下のブレークダウンポイントは、高い電界ピークを持っています。 T として sti 増加すると、電界のピークが緩和され、 BV 増加します。 T の場合 sti =0.3μm、43VのBVが得られます。 T の場合 sti ≥0.3μmの場合、ポリフィールドプレートのエッジの下の電界ピークは十分に低く、その結果、ブレークダウンポイントはドレイン側の下のP / N接合に移動します。 T として sti 増加すると、BVが増加し、その後飽和します。

a 数値(点線)および分析(実線)BVおよび R on、sp N の関数として pb さまざまな N d 。 b 数値(点線)および分析(実線)BVおよび R on、sp T の関数として sti

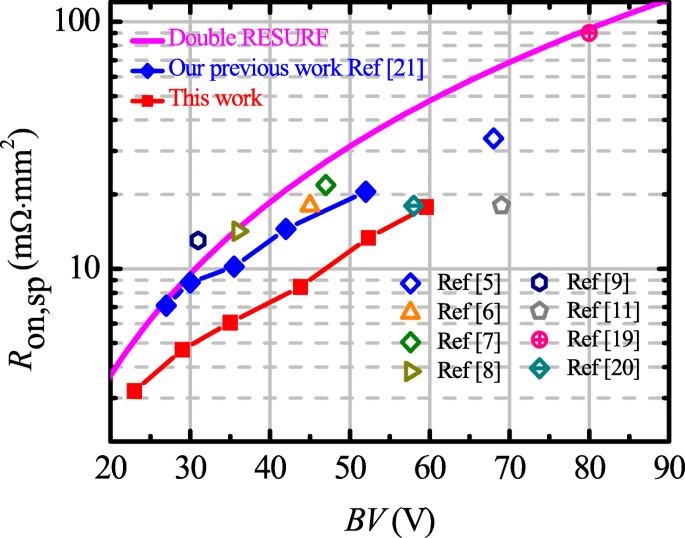

図6は、既存のBipolar-CMOS-DMOS(BCD)テクノロジーと提案されたLDMOSのベンチマークを示しています。明らかに、提案されたLDMOSのプロセス技術は、LDMOSのクラス最高のパフォーマンスを達成した当社が開発したBCD技術と互換性があります。提案されたLDMOSの製造プロセスでは、N埋め込み層はPウェルと同じマスクを共有できます。提案されたLDMOSの場合、 R on、sp は8.5mΩ・mm 2 一方、BV =43 Vは、以前の作業と比較して約37%削減されています。

既存のBCDテクノロジーと提案されたLDMOSのベンチマーク

結論

強化されたデュアルゲートと部分的なP埋め込み層を備えた新しい超低比オン抵抗LDMOSを提案し、この論文の数値シミュレーションによって調査した。ドーピング濃度の高いN埋め込み層を利用して、 R を低減しながらデュアルゲートを強化します。 c 。 BV を強化するために、部分的なP埋め込み層がNドリフト領域の下に導入されます。 充電バランスを保ちながら。この作業でのLDMOSの製造プロセスは、前の作業で報告された既存のBCDテクノロジと互換性があります。結果は、 R が on、sp 提案されたLDMOSの割合は、以前の作業と比較して、43 VのBVで37%減少します。半導体処理技術がナノメートルレベルに達すると、 R on、sp チャネル長が減少するとさらに減少する可能性があります。

略語

- BCD:

-

バイポーラ-CMOS-DMOS

- BV:

-

絶縁破壊電圧

- LDMOS:

-

横方向二重拡散金属酸化物半導体トランジスタ

- RESURF:

-

表面フィールドを減らす

- R on、sp :

-

特定のオン抵抗

- USTI:

-

超シャロートレンチアイソレーション

ナノマテリアル

- ドラッグデリバリーを強化するためのナノファイバーとフィラメント

- プラズマ化学原子層堆積によるその場で形成されたSiO2中間層を有するHfO2 / Geスタックの界面、電気、およびバンド整列特性

- 光触媒性能が向上した新規Bi4Ti3O12 / Ag3PO4ヘテロ接合光触媒

- 垂直に整列した単層カーボンナノチューブの成長に及ぼすアルミナ支持層の強化された熱安定性の効果とナノ濾過膜におけるそれらの応用

- ペロブスカイト太陽電池の変換効率に及ぼすTiO2コンパクト層に埋め込まれた異なるサイズと濃度のAgナノ粒子の影響

- トランスフェリン受容体による細胞内在化が増強されたパクリタキセルベースの標的脂質ナノ粒子の抗増殖およびアポトーシス誘発能—白血病細胞での研究

- 局所電場が大幅に増強された可視領域におけるボイドプラズモン効果による全方向性吸収体

- 高いオン/オフ比と極性切り替え可能な光伝導性を備えたSnSe2電界効果トランジスタ

- 静電容量が強化されたスーパーキャパシタ電極用の原子層堆積によって製造されたTiO2ナノメンブレン

- 太陽照射下での電荷分離と高い光触媒活性を強化するための部分的な表面改質を備えたZnO多孔質ナノシート

- 2段階のポストアニーリングを備えた原子層堆積酸化アルミニウムによる強化されたSiパッシベーションとPERC太陽電池効率