理想的な原子層堆積Al2O3トンネルスイッチ層によるMgドープLiNbO3膜の強誘電性能の改善

要約

5%のMgドープLiNbO 3 で構成される二重層構造 単結晶膜と極薄Al 2 O 3 原子層堆積法と組み合わせたイオンスライス技術を使用して、2〜6nmの厚さの層が製造されています。過渡領域スイッチング電流の測定結果から、 P-V ヒステリシスループはタイプIIモードで対称であり、サイクルごとに単一の電圧パルスがあります。これは、非対称電極によって形成される組み込み電界と内部インプリント電界の補償に起因する可能性があります。その上、象眼細工のAl 2 O 3 は、理想的なトンネルスイッチ層として、強誘電体スイッチング中にオンになりますが、印加されたパルス電圧の下でのポストスイッチングまたは非スイッチング中に閉じます。 Al 2 O 3 層は、電極による電荷注入などの悪影響をブロックし、MgをドープしたLiNbO 3 の疲労耐久性を向上させます。 強誘電体コンデンサ。この研究は、不揮発性メモリアプリケーションにおける強誘電体デバイスの信頼性特性を改善するための可能な方法を提供します。

背景

ニオブ酸リチウム(LN)単結晶膜は、その優れた物理的特性により、弾性表面波発振器、電気光学変調器、およびに基づくデータストレージで広く使用されています。ドメインの切り替え。最近、電気光学、音響光学、およびデータストレージデバイスの高密度集積回路に大きな可能性を秘めているウェーハスケールのニオブ酸リチウムオンインシュレータ(LNOI)は、イオン注入およびウェーハボンディング技術によって製造されています。 。この技術により、LN、シリコン、さらにはCMOS回路などのさまざまな基板が可能になります[3、7、8、9]。ただし、電極による電荷注入によるLNフィルムの優先配向と疲労耐久性の低さに起因するインプリントヒステリシスループは、分極反転の保持を不安定にし、不揮発性メモリデバイスでのアプリケーションを制限します[10、11、12 、13]。強誘電体層と電極の間に形成された界面不動態層に関連する好ましい配向は、分極の反対方向に強い脱分極場を誘発する可能性がある。印加電圧を除去した後、またはその後のパルスストレスの断続的な時間の間に、注入された電荷を追い出すことができます[11、12]。一方、界面不動態層が存在するため、強誘電体スイッチング後の電極による電荷注入をブロックすることにより、LN膜の疲労耐久性が向上します。ただし、適用されるパルス周期の時間が0.5秒未満に短縮されると、疲労プロセスが加速します。これは、特定の周波数での累積空間電荷の界面受動層の寄与によって説明されます[11]。象眼細工のAl 2 O 3 誘電体膜は、誘電体/強誘電体二重層コンデンサ、たとえばAl 2 のトンネルスイッチとして機能します。 O 3 / Pb(Zr、Ti)O 3 、およびAl 2 O 3 / MnドープBiFeO 3 二分子膜構造[14、15、16]。 Al 2 O 3 トンネルスイッチは、分極スイッチング中に導体としてオンになりますが、分極スイッチングが完了した後、またはスイッチング操作がない場合、電極による電荷注入をブロックするために絶縁体としてオフになります[14]。したがって、不要な注入電荷と分極バックスイッチングを防ぎ、誘電体/強誘電体二重層コンデンサの信頼性を向上させることができます。

この論文では、厚さ200 nmのZカット5%Mgドープ合同LN単結晶薄膜を作製し、次に極薄Al 2 を堆積しました。 O 3 LN上にさまざまな厚さ(2〜6 nm)の層を形成して、2層コンデンサ構造を形成します。 Al 2 O 3 トンネルスイッチ層としてのフィルムは、疲労耐久性を向上させることができます。非対称電極(Au / Pt電極)は、界面不動態層によって誘発される脱分極場に対してビルトイン電場を形成するように設計されています。電気的結果は、ドメインスイッチング電流トランジェントから時間とともに伝達されるヒステリシスループの対称性を示しています。一方、象眼細工のAl 2 O 3 レイヤーはトンネルスイッチレイヤーとして機能し、強誘電体スイッチング中にターンアップし、分極スイッチングが完了した後、またはスイッチング操作がない場合に閉じることができます。

メソッド

Zカット5%Mgドープ合同LiNbO 3 (LN)単結晶薄膜は、他の場所で説明されているように、イオン注入およびウェーハボンディング技術を使用してバルク結晶から剥離されました[10、11、17、18]。詳細には、LNバルク結晶の表面層に、注入エネルギーと注入イオンのドーズ量を制御することにより、最初に必要な深さでHeイオンを注入し、次に5nmのCr付着層と100nmのPt下部電極層をDCで堆積します。スパッタリング(KJレスカーPVD-75)。表面層は、厚さ1μmのSiO 2 で覆われた別のLN基板に結合されました。 バッファ層とスライスオフ。 LN膜の厚さは、化学機械研磨によって約200nmに制御されます。続いて、極薄のAl 2 O 3 厚さのあるフィルム( d )2〜6 nmがALD(TFS-200、Beneq、フィンランド)によって寄託されました。詳細には、前駆体ガスはジエチル亜鉛と脱イオン水です。それらは50msのパルス時間で反応チャンバーに交互にパルスされ、200°Cの反応温度で2秒間アルゴンを使用してパージステップによって分離されました[19]。最後に、面積が1.0×10 -4 の上部Au正方形電極 cm 2 金属の浅いマスクを通して堆積されました。

Al 2 の厚さ O 3 コントラストとしてSiウェーハ上に堆積された層は、分光エリプソメトリーシステム(GES-5E、SOPRA、Courbevoie、フランス)によって測定されました。フィルム構造は、Cu K を使用したθ-2θスキャンモードでのX線回折(XRD)(Bruker D8 Advance)によって分析されました。 α 放射線および断面走査型電子顕微鏡(SEM、Sigma HD、Zeiss)。ドメインスイッチングのダイナミクスを研究するために、立ち上がり時間が10ナノ秒のいくつかの方形パルスを、下部電極が接地されたシングルチャネルのAgilent8114Aパルスジェネレータを使用して上部電極に適用しました。回路では、ドメインスイッチング電流( I sw )LeCroy HDO6054オシロスコープを使用して、すべての機器の直列内部抵抗器全体を全抵抗で監視しました。パルス発生器の両方の出力抵抗の値 R W オシロスコープの入力抵抗 R O それぞれ50Ωです。

結果と考察

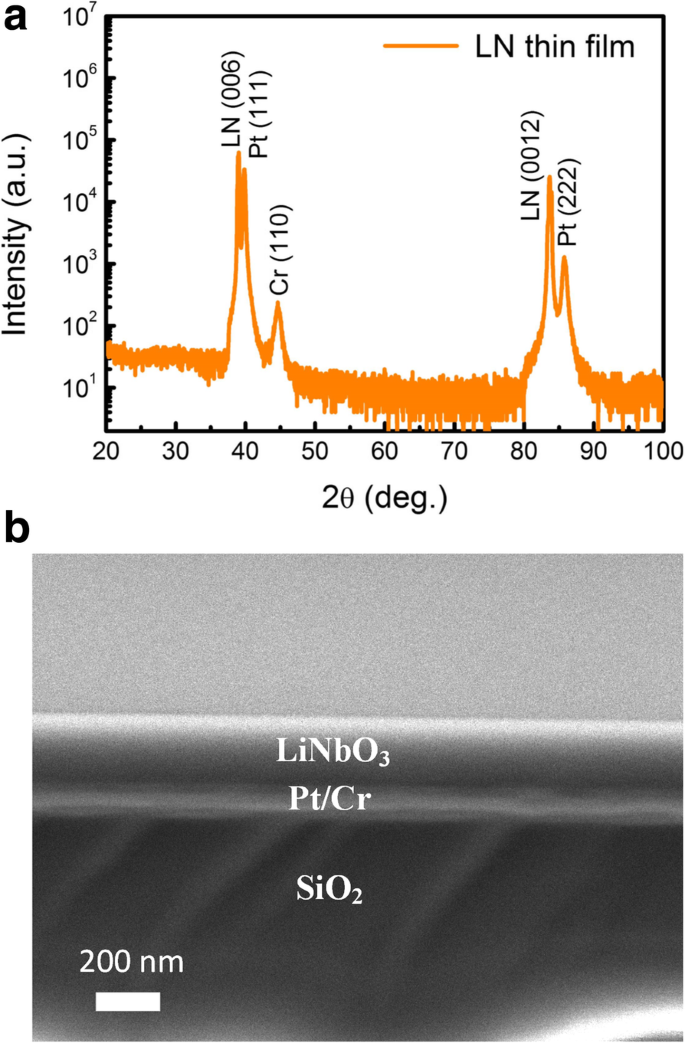

図1aは、Pt / Cr / SiO 2 上のLN薄膜のXRD結果を示しています。 / LN基板。フィルムは強い(00 l )菱面体晶位相対称でインデックス付けされた反射。さらに、図1aにマークされているPtおよびCr膜の回折ピークもいくつかあります。他のピークがないことは、相不純物のないLN膜の高い結晶化度を確認します。図1bに示すサンプルの断面SEM画像は、LN、Pt、Cr、およびSiO 2 との明確な界面構造を示しています。 スタッキングレイヤー。

a XRDパターンと b Zカット200nm厚のLN / Pt / Cr / SiO 2 の断面SEM画像 / LNフィルム

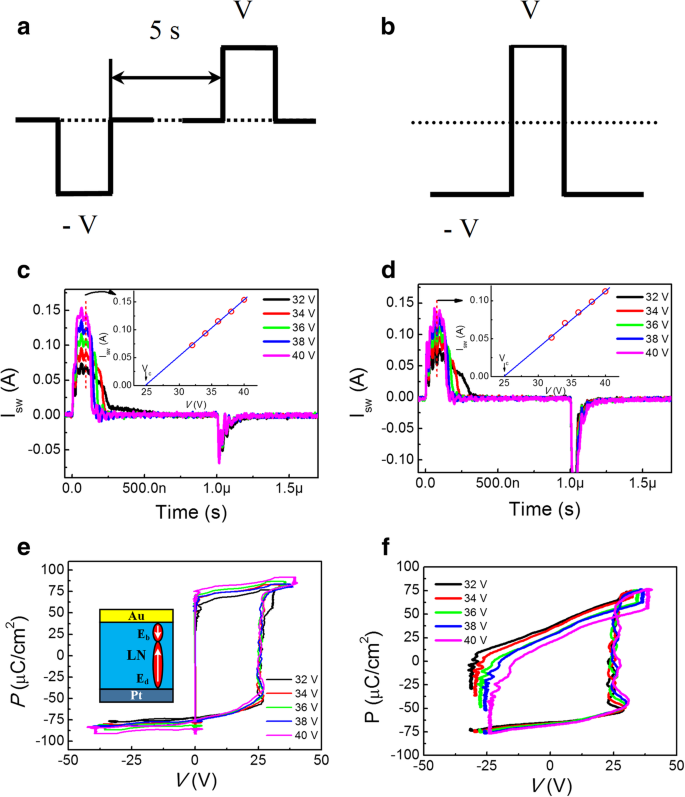

ドメインスイッチングの速度論的メカニズムを研究するために、図2aおよびbに明確に示されているように2種類のパルス電圧モードが設計されています[11]。タイプIは、5秒の時間間隔で反対の極性のダブルパルスとして構成されます。最初のパルスは、上部電極を指す上向きの分極状態を切り替えるために適用され、2番目のパルスは下向きの分極を切り替えることができます。ただし、単一チャネルパルス生成のプログラミング時間によって制限されるため、最小時間間隔が長すぎて、優先ドメイン方向のために、2番目のパルスによって呼び出されるドメインスイッチング電流トランジェントをキャッチできません。ドメインスイッチング電流トランジェントをキャッチするために、負のベースラインDCバイアスとオーバーラップする単一パルスがタイプIIで提案されます。この場合、初期の負のDCバイアスは上向きの分極状態を切り替え、正のパルスはドメインを下向きに設定します。ここでは、2つのタイプのパルスの幅を1μsに設定しています。

a を使用した2つのシーケンスパルス電圧モードのスケッチ タイプI(2つの反対の極性のダブルパルス)および b タイプII(負のDCバイアスとオーバーラップする単一のスイッチングパルス)。異なる V でのドメインスイッチング電流トランジェント c の未使用のサンプルに適用 タイプIと d タイプIIモード。挿入図は、ドメインスイッチング電流のプラトーの V への依存性の線形フィットを示しています。 。 P - V 異なる V でのヒステリシスループ e のドメインスイッチング電流トランジェントから転送 タイプIと f タイプII。 Au / LN / Pt構造とビルトイン電界の方向の概略図 E b および脱分極場 E d e の挿入図

図2cとdは、ドメインスイッチングの過渡電流と時間の関係を示しています( t )さまざまな印加電圧( V )下でのAu / LN / Pt構造サンプルの )それぞれタイプIおよびタイプIIモード。ドメインスイッチング電流トランジェントのプラトーは、幅は狭くなりますが、 V とともに高さが増加することが観察されます。 30nsでの最初のコンデンサ充電電流の後に増加します。 2つのモードのプラトーの高さは、どちらも V の増加と線形の関係を示しています。 結果は、データの実線フィッティングによって挿入図に要約されています[11、13]。強制電圧( V c )2つのモードの値は、電圧軸とのライン遮断から約24.7Vに導き出すことができます。スイッチングパルスの終了後、コンデンサの放電電流は1μs後に発生します。これは、優先ドメイン配向が上部電極を指す上向きの分極状態であることを示唆しています。

P - V 2つのタイプモードの異なる印加電圧でのヒステリシスループは、図2cおよびdの対応するドメインスイッチング電流トランジェントから直接転送でき、結果はそれぞれ図2eおよびfに示されています[11、20]。 V で不変の約25Vの決定された順方向強制電圧 2種類のパルスで得られます。強制電圧は V に近づきます c 線形 I から抽出 sw - V 図2cとdの挿入図にプロットします。ドープされていないLNフィルムとは異なり、 V c は可変であり、値は最大印加電圧に等しくなります[10]。 5%のMgドープLNの場合、定義された V c V では不変です 、図2eおよびfに示すように。これは、MgドーピングがLiサイトの金属空孔と酸素空孔関連の欠陥を生成する可能性があるためです[21、22、23]。これにより、空間電荷がトラップされ、膜と上下の界面層全体の抵抗劣化時間が効果的に短縮されます。電極[11]。したがって、ドメインスイッチング電流は、明確な V でドメインスイッチング速度を加速する際のコンデンサ充電電流とオーバーラップします。 c 、図2cおよびdに示すように。ただし、パルスジェネレータによって制限されるため、タイプIIモードの出力ベースライン電圧は、印加パルス電圧を32 V以上に上げると対称的にシフトできません。図2eの正の電圧軸に沿ったインプリントループと比較すると、ループの対称性は次のようになります。 Pt / LiNbO 3 の電圧軸とは異なり、図2fの電圧軸に沿って達成されます。 / Pt構造で、 P - V タイプIまたはタイプIIのヒステリシスループは、正の電圧に向かって刻印されています[11]。対称的な P の理由 - V 図2fのループは、設計された非対称電極(ここではAu / Pt)に起因している可能性があります。 Au電極の仕事関数は5.1eVであり、Ptの仕事関数(5.65 eV)よりもわずかに小さい[24]。ビルトイン電界( E )が誘導されます b )図2eの挿入図に示すように、上部電極から下部電極に向かう方向を使用します。脱分極場( E d )界面不動態層によって誘発されるのは、 E とは反対の方向です。 b 。 E d 対称電極(Pt / Pt)のタイプIIのスイッチングパルスの終了後、非常に短時間で分極を元に戻すことができます[11]。私たちの実験では、 E b E を部分的にスクリーニングできます d 内部インプリントフィールドを補償するために注入された電荷を蓄積し[16]、バックスイッチング時間を遅くする可能性があります。したがって、スイッチドドメインは維持でき、バックスイッチング電流トランジェントはタイプIIパルスによってキャプチャされます。ただし、タイプIモードで極性が反対の2つのパルスの時間間隔が長すぎます。最初のパルスの後、トラップされた注入電荷は E b E によって徐々に映画から追い出されます d タイプIの2番目のパルスが到着する前[11]。ループの対称性に対するビルトイン電界の帰属を証明するために、Pt / LiNbO 3 / Pt対称構造サンプルを準備し、正の電圧軸に沿って刻印されたループを、追加ファイル1の対応するドメインスイッチング電流トランジェントから直接転送しました。図S1aは、電圧/幅が30〜40 V / 500nsの正のパルスで示されています。追加ファイル1:図S1b。

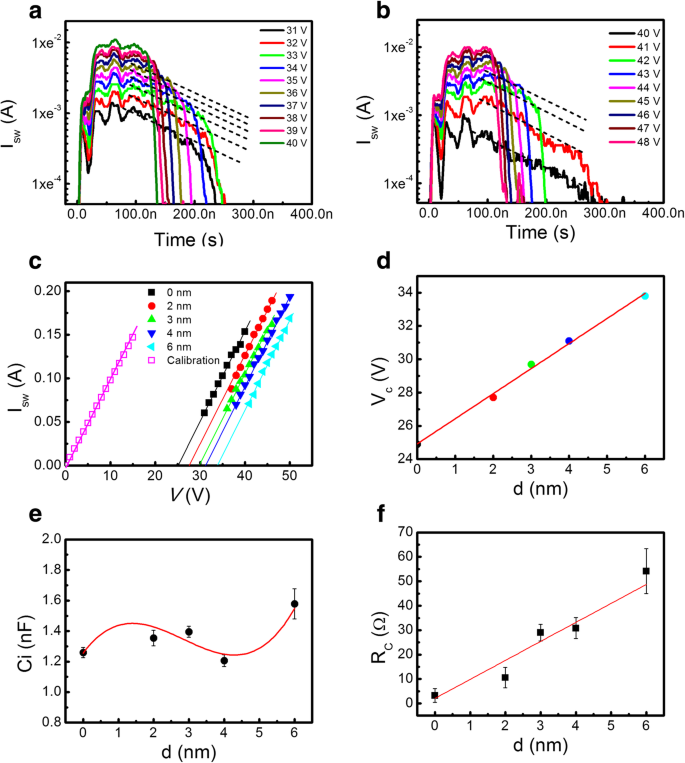

図3aおよびbは、ドメインスイッチング電流( I )を示しています。 sw )トランジェント対時間( t )LNとAl 2 の O 3 (6 nm)/ LNサンプル、異なる印加電圧( V )タイプIモード。ドメインスイッチングのプラトーの後、スイッチング電流 I sw 崩壊し、次の式で与えられます:[13]

$$ {I} _ {\ mathrm {sw}} ={I _ {\ mathrm {sw}}} ^ 0 \ exp \ left(-\ frac {t- {t} _0} {R _ {\ mathrm {L} } {C} _ {\ mathrm {i}}} \ right)\ \ left({t} _0 \ le t \ le {t} _ {\ mathrm {sw}} \ right)$$(1)ここで t 0 、 t sw 、 R L 、および C i は、ドメインスイッチングの開始時間、ドメインスイッチングの完了時間、回路内のすべての直列抵抗の合計抵抗、および界面の非強誘電体容量です。これは、理想的な強誘電体層と直列の界面不動態層としてモデル化できる電荷トラップ効果について説明しています。 私 sw 0 スイッチング電流として定義され、次の式で与えられます。

$$ {I _ {\ mathrm {sw}}} ^ 0 =\ frac {V- {V} _ {\ mathrm {fc}}} {R _ {\ mathrm {L}}} $$(2)<図>

a 、 b 私 sw - t 異なる V でのタイプIの依存関係 Al 2 に適用 O 3 / LN二重層とAl 2 O 3 厚さ d =0および6nm、それぞれ、一連の平行な点線で式(1)に適合します。 (1)。 c 異なるAl 2 での印加電圧の関数としてのドメインスイッチング電流のプラトー O 3 層の厚さ。実線は、データが式(1)に最もよく適合していることを示しています。 (2)。 d Al 2 O 3 -層の厚さ d 強制電圧の依存性( V c ) c から抽出 。 e 、 f 抽出された界面容量 C i および接触抵抗 R C Al 2 の関数として O 3 層の厚さ d

ドメインスイッチング中、強誘電体層に印加される電圧は、強制電圧 V に固定されます。 fc 、および追加の電圧( V - V fc )は R に適用されます L 。 R L 回路の寄生抵抗( R )も含まれています P )および接触抵抗( R C )フィルムと電極の間;したがって、 R L = R O + R W + R P + R C 。時間に対するスイッチング電流過渡の減衰部分は、式(1)で近似できます。 (1)。時定数 R L C i 適合線の傾きから推定できます。図3cは、 I を示しています sw 0 - V 異なるAl 2 のプロット O 3 厚さ。 R L および V C 勾配と X から推定されました -線形フィットラインの軸切片。 V C Al 2 の増加に伴って直線的に増加します O 3 厚さ d 、図3dに示すように。ここで、 C i 値は、各 V での誤差範囲として推定されました。 図3e [13]。結果は、 C i Al 2 の増加に伴い、値はほぼ一定(1.4±0.2)nFに保たれました。 O 3 層の厚さは0〜6nmです。

R を計算するため C 、上部電極と下部電極が短絡しているため、 R を取得できます。 P (〜2Ω)異なる印加電圧で、図3cの白抜きの記号で回路校正として示されています。したがって、 R C d に対応 が計算され、その結果が図3fに示されています。 R C d で3±2.5Ωから直線的に増加します =0〜55±10Ω( d ) =6nm。ほぼ d -独立した大きな C i 値は、Al 2 O 3 層は、ドメインスイッチング中に直列抵抗として機能します。これは、Al 2 が O 3 FE切り替え中にトンネルスイッチがオンになりました。

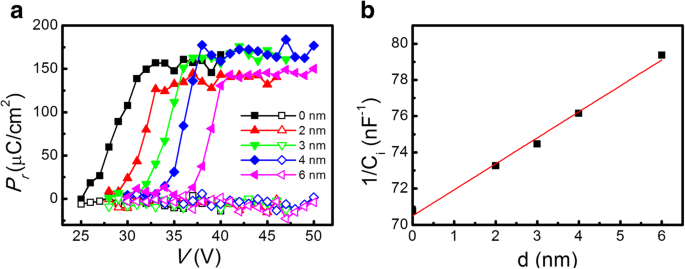

FE非スイッチング中の二重層の総静電容量を取得するために、スイッチング( P sw )および非スイッチング( P nsw )偏光ベサス V d で タイプIモードのパルスで0から6nmに増加が測定され、結果が図4aに示されています。タイプIパルスを選択する目的は、 P の曲線を取得することです。 nsw - V 印加電圧の方向が分極方向と一致している場合、そこから総静電容量( C tot )の二重層は、 C の関係から計算できます。 tot = S ・ dP nsw / dV 、ここで S は電極面積です。タイプIパルスモードでのFEスイッチングによる電荷効果を完全に排除できますが、タイプIIモードを使用しても、電荷注入に伴う分極を元に戻すことができる負のスイッチング分極ではこの効果を達成できません。 P の違い sw および P nsw 図4aに示すように、は2Prです。 d で少し変化があります P に対して、0〜6nm nsw (白抜きの記号)信号は弱すぎてオシロスコープで監視できません。 Al 2 を証明するため O 3 誘電体コンデンサとして機能するトンネルスイッチ層、直接 C tot 追加のDCバイアスを使用せずに100kHzで低周波インピーダンスアナライザを使用して測定を実行し、その結果を図4bに示します。 (3):

$$ \ frac {1} {C _ {\ mathrm {tot}}} =\ frac {1} {C _ {\ mathrm {f}}} + \ frac {d} {\ varepsilon_0 {\ varepsilon} _ {\ mathrm {Al}} S} $$(3)ここで、ε Al Al 2 の誘電率です O 3 レイヤーとε 0 は自由空間の真空誘電率です。 C f および S 強誘電体層の静電容量と電極面積をそれぞれ表します。図4bは、線形1 / C を示しています。 tot 対 d プロット。これは、Al 2 O 3 層は、非スイッチング状態またはポストスイッチング下で高絶縁誘電体膜になります。 C f ≈14pFおよびε Al 式から≈7.9 (3)。したがって、挿入された薄いAl 2 O 3 層は誘電体コンデンサとして証明されています。 FE非切り替え中およびFE切り替え後、Al 2 O 3 トンネルスイッチは絶縁体として閉じます。

a 切り替え( P sw )および非スイッチング( P nsw )分極対 V d で タイプIモードのパルスで0から6nmに増加しました。 b Al 2 O 3 -層の厚さ d 1 / C の依存性 tot 100kHzでインピーダンスアナライザによって測定

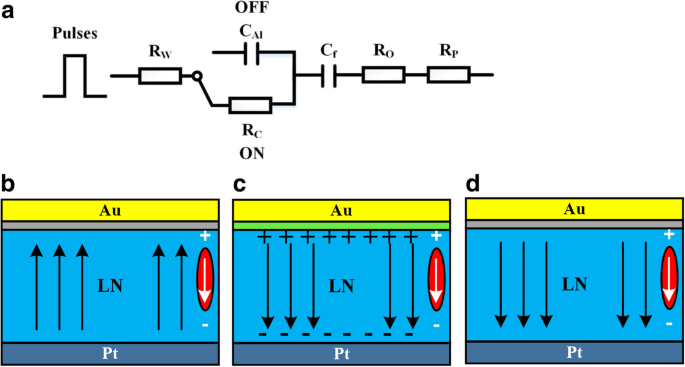

図5に、Al 2 の概略図を示します。 O 3 / LN二重層構造がタイプIまたはタイプIIモードで切り替えられました。図5aは、Al 2 の直列抵抗とコンデンサの等価オンオフ回路を示しています。 O 3 トンネルスイッチ。初期状態では、図5bに示すように、好ましい分極方向は、上部電極を指す上向きの分極状態です。非対称電極によって誘導されるビルトイン電界は、Au電極からPt電極に向けられます。分極電圧を印加すると、FEスイッチングが発生します。電圧は回路の静電容量に反比例して印加されることが理解されます。 Al 2 で O 3 / LN二重層構造、FEスイッチング中、LN層は大きな静電容量を持ちます。したがって、外部印加電圧のほとんどはAl 2 に印加されます。 O 3 層。極薄Al 2 O 3 層は電極電荷によって注入されます。印加電圧がAl 2 を超えると、抵抗としてオンになります。 O 3 図5cに示すように、トンネリングのしきい値。 FEスイッチングの完了後、または非スイッチング状態の場合、LN層の静電容量は非常に小さく、Al 2 に印加される電圧は非常に小さくなります。 O 3 トンネリングしきい値電圧よりも低く減少します。現時点では、Al 2 O 3 図5dに示すように、レイヤーは絶縁体として機能し、スイッチがオフになります。

Al 2 の概略図 O 3 / LN二重層構造がタイプIまたはタイプIIで切り替えられました。 a Al 2 の直列抵抗とコンデンサの等価オンオフ回路のスケッチ O 3 トンネルスイッチ。 b 初期の優先分極配向とビルトイン電界。 c Al 2 O 3 トンネルスイッチのオンとドメインの切り替え。 d Al 2 O 3 トンネルスイッチがオフになり、偏波が維持されます

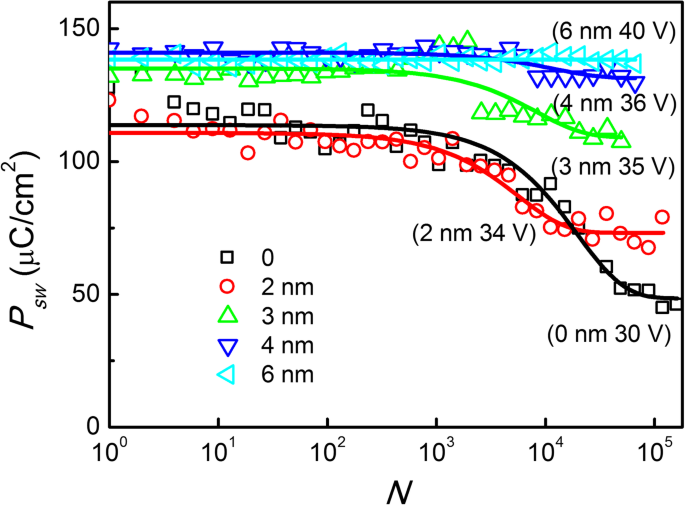

図6は、Al 2 の切り替えられた分極のサイクル数依存性を示しています。 O 3 Al 2 の厚さの/ LN二重層構造 O 3 タイプIモードでは0〜6nmの範囲です。パルスの幅は1000nsで、周期は0.5sです。 Al 2 の疲労耐久性がはっきりとわかります。 O 3 / LN二重層構造は、Al 2 の増加とともに徐々に改善されます。 O 3 10 4 を超える厚さ パルスストレスのサイクル。タイプIIモードの疲労特性は、追加ファイル1:サポート情報の図S2に示されているタイプIモードの結果と同様です。残念ながら、タイプIIモードでは、10 4 近くの長時間のDC電圧が印加された後、絶縁破壊が発生しやすくなります。 パルスストレスのサイクル。データは、疲労物理学が電極による電荷注入に起因する図6の実線で示されているように、各サイクル内での磁壁のピン止めとピン止め解除の共存モデルを使用して適合させることができます[13]。 Al 2 の場合 O 3 Au電極とLN層の間に挿入された層は、電極による注入電荷経路を遮断し、疲労耐久性を向上させることができます。ただし、二重層構造では、いくつかの問題をさらに検討する必要があります。たとえば、Al 2 の厚さを増やすと O 3 0から6nmに、強制電圧は25から34 V近くに拡大しました。これは、Al 2 の品質を改善することで減らすことができます。 O 3 層。実際、Al 2 のいくつかの原子層 O 3 高品質または欠陥の少ないものは、電極によって注入された電荷を効果的にブロックできます。これは、原子層堆積処理条件(温度や時間など)を最適化することで他の場所で確認されています[25]。

Al 2 における切り替えられた分極の循環数依存性 O 3 Al 2 の厚さの/ LN二重層構造 O 3 10 4 未満で0〜6nmの範囲 パルスストレスのサイクル。パルスの幅は、0.5sの周期で1000nsです

最近、消去可能な導電性帯電磁壁と分極状態の非破壊電気的読み出しに基づく強誘電性磁壁メモリが、以下の研究で提案されました[26、27]。ニオブ酸リチウム単結晶の帯電した磁壁の大きな導電率は、磁壁の切り替え後に得られます[28、29]。したがって、シリコン基板上のより薄いニオブ酸リチウム単結晶薄膜は、統合された強誘電性磁壁メモリの有望な材料であり、その保持および疲労耐久性は、Al 2 の設計によって改善することができます。 O 3 /ニオブ酸リチウム二重層。

結論

200ナノメートルのLiNbO 3 バルクLN単結晶から表面層をイオンスライスし、次に極薄のAl 2 を使用して、Mgを5%ドープした単結晶膜を作成しました。 O 3 トンネルスイッチ層として2〜6 nmの厚さの膜を、5%のMgドープLN膜上に堆積させ、原子層堆積によって二層構造を形成しました。対称化された P-V 電圧軸に沿ったヒステリシスループは、タイプIIモードで印加されたパルス電圧の下で観察されます。これは、Au / LiNbO 3 の非対称電極によって誘導されたビルトイン電界に起因する可能性があります。 / Ptおよび内部インプリントフィールドの補正。ドメインスイッチング電流( I sw )トランジェントとその転送された P-V ヒステリシスループは、極薄のAl 2 O 3 レイヤーはアイデアトンネルスイッチとして機能します。 FEスイッチング中はオンになりますが、非スイッチング中またはFEスイッチング後に閉じ、FEスイッチングへの悪影響を最小限に抑えます。さらに、FEコンデンサの疲労耐久性は、トンネルスイッチ層の厚さが2nmから6nmに増加するにつれて徐々に改善されます。 Al 2 O 3 / LN二重層構造は、電極電荷注入による疲労の問題を軽減する堅牢な強誘電体デバイスを設計するための道を開きます。

略語

- ALD:

-

原子層堆積

- CMOS:

-

相補型金属酸化膜半導体

- FE:

-

強誘電体

- LN:

-

ニオブ酸リチウム

- SEM:

-

走査型電子顕微鏡

- XRD:

-

X線回折

ナノマテリアル

- マイクロLEDおよびVCSEL用の高度な原子層堆積技術

- 原子層堆積によって製造されたPtおよびTiNコーティング基板上のHfO2 / TiO2 / HfO2三層構造RRAMデバイスのバイポーラ抵抗スイッチング特性

- プラズマ化学原子層堆積によって調製されたCo3O4被覆TiO2粉末の光触媒特性

- 界面層の設計によるZnO膜の表面形態と特性の調整

- 超循環原子層堆積によるZnO膜のフェルミ準位調整

- 光触媒性能を改善するための階層的ZnO @ NiOコア-シェルヘテロ構造の製造

- c面GaN上に堆積した原子層AlNの界面および電気的性質への厚さ依存性

- Ge / Siチャネル形成とデバイス性能に及ぼすエッチング変動の影響

- T型ゲートデュアルソーストンネル電界効果トランジスタのアナログ/ RF性能

- c軸配向エピタキシャルBaドープBiCuSeO薄膜の熱電性能の向上

- 二酸化炭素を使用したSiO2の低温プラズマ強化原子層堆積