p-GaAsナノワイヤへのオーミック接触の最適化

要約

半導体ナノワイヤ(NW)に適用されるオーミックコンタクトの性能は、電子またはオプトエレクトロニクスデバイスでの使用を可能にするための重要な側面です。 NWの寸法が小さく、比表面積が大きいため、平面ヘテロ構造用に広く開発されている標準的な処理技術を直接適用することはできません。ここでは、分子線エピタキシーによって成長したp型GaAsナノワイヤのPt / Ti / Pt / Auオーミックコンタクトの製造と最適化について報告します。デバイスは、電流-電圧(IV)測定によって特徴づけられました。個々のナノワイヤのIV特性曲線の直線性は、接触金属層のレイアウト、金属蒸着前の表面処理、および後処理熱アニーリングを調整することによって最適化されました。我々の結果は、p型平面GaAsに使用される従来のTi / Pt / Au多層レイアウトの前にPt層がGaAsナノワイヤ上に堆積されると、接触抵抗が著しく減少することを明らかにしています。これらの発見は、金属-GaAs界面の品質の向上によって説明されます。これは、GaAs(110)基板上に堆積された同様の金属薄膜のかすめ入射X線回折測定によって証明されました。特に、TiはGaAs(110)表面に堆積したときに結晶化度が低く、NWデバイスの接触抵抗に直接影響することを示しています。 Ti / Pt / Auの前にNWに薄いPt層を堆積すると、BeドープGaAs NWの総電気抵抗が95%減少します。これは、直接堆積した場合のTiよりもPtの結晶化度が高いことに関連しています。 GaAs(110)上。

はじめに

半導体電子およびオプトエレクトロニクスデバイスの製造における重要なステップは、金属-半導体界面で高品質で信頼性の高いオーミック接触を実現することです。この目的のために、GaAsは、レーザーデバイス、太陽電池、光検出器などの技術アプリケーションで広く使用されている重要な材料です。したがって、p型およびn型をドープしたGaAs層へのオーミック接触の作製は、多くの調査の対象となっています[1]。一般的に言えば、半導体材料へのオーミック接触の製造には、(1)表面の自然酸化物の除去、(2)半導体-金属界面での表面状態の不動態化、(3)として機能する金属層の堆積の4つのステップが含まれます。電気接点、および(4)熱アニーリング[2、3]。低い接触抵抗と優れた熱安定性を提供する金属の選択から始めて、Auベースの合金が広く利用されてきました。特にAu / Zn / Au [1、3、4]およびTi /の形のp型GaAsに利用されています。 Pt / Au [1、5]層。一方、半導体III-Vナノワイヤ(NW)は、LED [6、7]、太陽電池[8、9]、および光検出器[10]としての用途向けの新しいクラスの有望なナノスケール材料として登場し、これらがトリガーされました。デバイス処理に関する特定の開発。

オーミック接触製造に関する文献で報告されている技術の大部分は、GaAs(100)薄膜およびバルク構造用に開発されましたが、GaAs NWの自己触媒成長により、側壁で(110)表面配向が得られます[11、12、13、 14,15]。表面の向きが異なれば、電子状態も異なり[16]、界面特性とショットキー障壁の高さに影響します[17、18、19]。さらに、表面配向は、堆積された金属膜の結晶化ダイナミクスに影響を与える可能性があります。 p-GaAs NWへの良好なオーミック接触は以前に報告されており[20、21、22、23、24、25、26、27、28]、さまざまな化学処理を使用して、自然酸化物、表面パッシベーション、およびさまざまな金属多層を除去します。 NWに預けられます。次に、p型GaAs薄膜にPt / Ti / Pt / Au電気接点を使用すると、Pt / GaAsのショットキー障壁の高さが低いため、中程度のドーパント濃度でもオーミック接触抵抗率が低くなることが報告されています[29]。さらに、Ptは、300〜500°Cの範囲の温度での熱処理に対して、GaAsへの反応速度が小さく熱的に安定していることがわかりました[29、30、31]。 Pt / Ti / Pt / Au金属多層膜が最も頻繁に報告されています[20、23、25、26、28] p-GaAsNWへのオーミック接触。ただし、オーミック接触形成の金属特性をより包括的に理解することは、ナノスケールデバイスの電気的接触品質をさらに向上させるための鍵です。最近報告されたp-GaAsNWの広範囲のNW成長技術とドーパント濃度のために、それらが利用可能である場合、接触抵抗の比較を行うことは実行不可能です。代わりに、同じNWサンプルのセットでのさまざまな接点製造ルートの包括的な調査が、NWプロパティの影響を除外するのに適しています。

ここでは、金属蒸着前のさまざまなPtおよびTiベースの電気接点と表面処理が、Si基板上に成長した自己触媒BeドープGaAs NWの全体的な電流-電圧(IV)特性に及ぼす影響について説明します[11、32 ]。 GaAs(110)基板上に堆積したTi、Pt、Pt / Ti薄膜のX線回折による構造調査に基づいて、NWチャネルの全抵抗の変化を分析します。高い接触抵抗は、GaAs(110)に直接堆積した場合、Tiの結晶化度が低いことに関連しているのに対し、Pt / Ti / Pt / Auの電気的接触は、接触抵抗の著しい減少をもたらします。 GaAs(110)表面に堆積した最初のPt / Ti層で観察された金属層の品質の改善。

材料と方法

Nanowire Growth

自己触媒BeドープGaAsNWは、液滴エピタキシーと自発酸化によってp-Si(111)基板上に作製されたリソグラフィーフリー酸化物パターン上で固体分子線エピタキシー(MBE)によって成長しました[32]。高温計で測定したNW成長温度は640°Cであり、GaAs(100)上での平面0.3μm/ h成長速度に対応するGaフラックスを使用しました。 60 s Gaの濡れは、As 2 を提供することによって開始された北西の成長に先行しました。 V / IIIビーム当量圧力比は9で、Beフラックスは2.0×10 19 に対応します。 cm -3 p型ドーピング濃度;これは、室温ホール測定による平面BeドープGaAs(100)キャリブレーションサンプルの成長から決定されました。成長時間は60分でした。ドープされていないNWとBeドープされたNWの成長方法と構造特性の詳細については、参考文献を参照してください。 [11、32、33]。要するに、NWは純粋な閃亜鉛鉱型GaAsで構成されており、いくつかの双晶面が形成されています[33]。 NWは六角形で、側壁は(110)配向ファセットのみで構成されています。これは、BeドープNWの構造解析から以前に決定され[33]、同様の条件下で成長した非ドープGaAsNWでさらに確認されたためです[12]。

連絡先の作成と特性評価

NWは、200 nmの厚さのSiO 2 で覆われたp-GaAs(100)基板に機械的に転写されました。 輸送特性評価のために、フォトリソグラフィーとTi / Auパッドの電子ビーム蒸着によって事前にパターン化された層。基板上の転送されたワイヤの位置は、低倍率の走査型電子顕微鏡(SEM)イメージングによって識別されました。正の電子ビームレジストを基板上にスピンコーティングし、電気接触領域上で電子ビームで露光した。表1に示すように、レジストは電子ビーム露光後にMIBK:IPA溶液で開発され、酸素プラズマ処理によって北西側壁の残留レジストが除去される可能性があります。デバイスの性能に対する酸素プラズマ処理の影響は次のようになります。後でテキストで説明します。接触層の金属蒸着の前に、本文で後述するように、サンプルを化学的に処理して自然酸化物を除去し、露出した北西側壁を不動態化しました。リフトオフは、サンプルを加熱したアセトンに浸し、IPAでリンスし、窒素でブロー乾燥することによって行われました。

<図>露出した北西側壁のさまざまな表面処理と、電気接点として使用されるさまざまな金属多層を組み合わせた5つの異なるプロセスを開発しました。これにより、p型GaAs NWに適用した場合に、結果として生じる接触抵抗における各パラメータの個々の寄与を決定することができました。表面の自然酸化物の除去には、2.8%NH 4 のいずれかを使用しました。 H 2 で希釈したOHまたは3.7%HCl Oの後にH 2 すすぎ。表面の不動態化には、(NH 4 の15%溶液を使用しました。 ) 2 S x H 2 で希釈 O(45°Cで加熱)に続いてH 2 すすぎ。金属多層は、電子ビーム蒸着を使用して堆積され、Ti / Pt / Au(20/20/200 nm)またはPt / Ti / Pt / Au(5/10/10/200 nm)のいずれかでした。 Pt / Ti / Pt / Au多層膜には、400°Cで30秒間の急速熱アニーリング(RTA)を使用しました。各サンプルに使用されたプロセスを表1に示します。各サンプルについて、4つの等間隔の電気接点がNW軸に沿って製造されました。この作業では、IV分析を北西の中央領域にある接触ペアに限定します。 IVデータは、Keysightプローブステーションを使用して室温で取得されました。

かすめ入射X線回折による構造調査

NW上の電気接点の構造特性を調査するために、かすめ入射X線回折(GIXRD)パターンを、ドープされていないGaAs(110)基板上に蒸着された参照Ti、Pt、およびPt / Ti薄膜から測定しました。 HClによる自然酸化物の除去を使用して表2に記載されている薄膜サンプルを準備しました:H 2 Oおよび(NH 4 による表面パッシベーション ) 2 S x NWデバイスの場合と同じように。 GIXRDで使用されるX線の入射角が小さいため、侵入深さが浅いため、NW接点で使用されるのと同じ厚さの金属膜を分析できます。 GIXRDパターンは、波長1.54Å、入射角ωのCuKα放射線を使用して測定されました。 =サンプル表面に対して0.75°。回折ピーク位置は、六角形最密充填(HCP)Tiおよび面心立方(FCC)PtのICDDファイル#00-044-1294および#00-004-0802に従ってインデックス付けされ、参考文献に記載されているGIXRD実験におけるX線の屈折の影響。 [34]。

<図>結果と考察

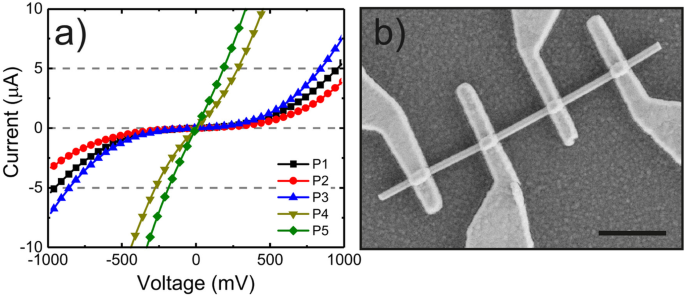

図1aはサンプルP1からP5のIV特性を示し、図1bは輸送特性評価に使用される電気接点を備えたBeドープGaAsNWのSEM画像を示しています。図1aのP1からP4のIVのほぼ対称な非線形形状は、接点がショットキータイプであり、各接点のバリア高が同じであることを示しています[35]。サンプルP1のIVの非線形性は、P1のような標準的なp-GaAsプロセスでは、GaAs平面薄膜の場合のようにオーミック接触が生じないことを明らかに示しています。通常、ドープされたGaAs NWでは、HCl酸化物の除去が使用され、その後に(NH 4 ) 2 S x NH 4 の代わりにオーミック接触形成[20、21、36、37]のための金属蒸発前の表面パッシベーション ああ。さらに、露出したNW表面の酸素プラズマ処理は、NW側壁から残留レジストを除去するために以前に使用されてきた[36、38]。ただし、副作用として、このプロセスはAs空孔などのGaAsの表面欠陥を引き起こし、キャリア補償の原因となるドナーのようなトラップを生じ、空乏層の幅を広げる可能性があります[5]。

a 表1に記載されているプロセスP1〜P5を使用して製造された電気接点を備えたBeドープGaAsNWからのIV。 b 4つの等間隔の電気接点を備えた代表的なBeドープGaAsNWのSEM画像。スケールバーは1μm

p-GaAs NWの接触抵抗に対する酸素プラズマ処理の影響を評価するために、HClおよび(NH 4 ) 2 S x 図1a。 P2は、すべてのサンプルで最悪のIV性能(同じ印加電圧に対する電流値として定義)をもたらしますが、サンプルP3は、標準のp-GaAsプロセスP1および酸素プラズマ洗浄P2よりも優れたIV性能を示します。これは、2つの重要な結果を意味します。(i)酸素プラズマ処理の効果は接触抵抗に悪影響を及ぼします。(ii)(NH 4 と組み合わせたHCl酸化物除去を伴うP3) ) 2 S x 表面の不動態化により、P1と比較して金属-半導体界面のショットキー障壁の高さが低くなります。

図1aからわかるように、Ti / Pt / Au多層膜の下に5nmのPt層を追加することにより、P3と比較してP4ではIV性能とオーミック特性(IV直線性によって定性的に評価)が大幅に向上しました。接触抵抗は、400°CでRTA 30秒後にP5でさらに減少し、P4と比較して線形IV動作を実現し、IVパフォーマンスを向上させます。

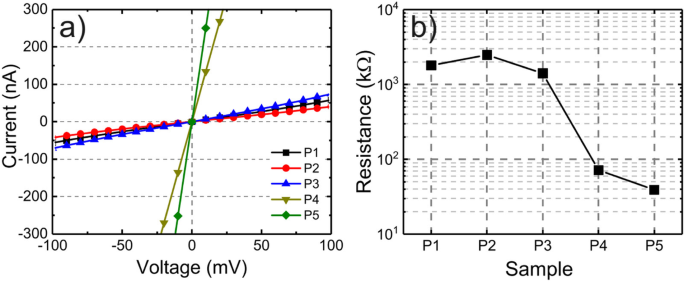

サンプルP1〜P5(化学処理、金属多層膜)の接触抵抗に対する処理パラメータの影響を定量化するために、より小さなバイアス範囲を使用したP1〜P5のIVを図2aに示します。この場合、IVは線形動作を示し、主に接触抵抗によって制御されます[35]。図2aの100mV範囲のチャネル(接点+ NW)からの総抵抗は、IV特性曲線の線形フィットから計算され、結果が図2bに示されています。以前に報告したように[33]、調査したすべてのNWの直径は類似しており、ドーパント濃度のワイヤ間の変動はわずかであるため、総抵抗の変化は接触抵抗によるものでした。 P1およびP3と比較してP2の抵抗が高いことは、図1aのIVの定性分析から、酸素プラズマ処理の有害な影響を確認しています。注目すべき結果は、P3の1400kΩからP4の72kΩへの総抵抗の減少と、P5のRTA後の40kΩへのさらなる減少です。これは、サンプルP1〜P3。

a 100mVの印加電圧範囲でのP1からP5までのIV。 b a のIVの線形フィットから得られたP1〜P5の合計チャネル抵抗

サンプルP1〜P5で観察された接触抵抗の変化の相関関係を確立するには、接触製造後の金属-半導体界面の微細構造をより包括的に理解する必要があります。 GaAsへのオーミック接触製造におけるTiおよびPtの使用は以前に報告されており[39、40]、GaAs(100)表面に蒸着されたTiおよびPt薄膜の構造特性[41]およびアモルファスガラス基板[42、43 ]も分析されています。しかし、GaAs(110)表面については、そのような詳細な研究は見つかりませんでした。異なる表面配向は、TiおよびPt薄膜の結晶化ダイナミクスに影響を与えると予想されます。さらに、(NH 4 ) 2 S x 結果として生じる薄膜にさらに影響を与える可能性があります。構造特性の情報を得るために、ドープされていないGaAs(110)基板上に堆積されたPt(5 nm)、Ti(20 nm)、およびPt / Ti(5/20 nm)薄膜の結晶化の程度がGIXRDによって調査されました。 P1〜P5のNWに接触している最初の金属層の。金属を蒸着する前に、GaAs(110)基板は、HCl:H 2 による自然酸化物の除去を受けました。 Oと(NH 4 ) 2 S x NWサンプルP3〜P5としての表面パッシベーションステップ。 GaAs(110)基板上に蒸着された表面処理と金属薄膜の詳細を表2にまとめています。

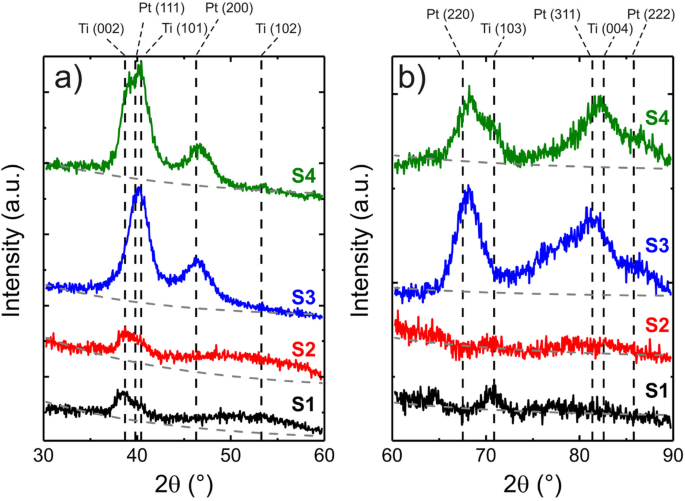

サンプルS1〜S4のGIXRDパターンは、図3aでは30〜60°の回折角範囲で、図3bでは60〜90°の範囲で示されています。図3の回折パターンは、垂直方向にシフトされ、2つの回折角度範囲で分離されているため、視覚化のためのスケーリングが向上しています。まず、(NH 4 ) 2 S x サンプルS1とS2を比較することにより、GaAs(110)基板上に蒸着されたTi膜の結晶化度に関する表面パッシベーション。図3aでは、S1とS2の両方で、それぞれ38.4°と40.2°を中心とする低強度のTi(002)とTi(101)のピークが重なっていることがわかります。さらに、53.0°を中心とする非常に広いTi(102)ピークも両方のサンプルで観察され、これはアモルファス特性を示唆しています。図3bの70.6°を中心とするTi(103)ピークは、サンプル間の唯一の有意な差異であるS1でのみ観察されます。一般に、S1とS2の低強度と広いピークは、(NH 4 の使用に関係なく、HCl酸化物除去後にGaAs(110)表面に堆積した場合のTi膜の結晶化度が低いことを示します。 ) 2 S x 不動態化。 S2と同じ表面処理でPtがGaAs(110)基板上に堆積されたS3の場合、はるかに顕著なPt(111)、Pt(200)、Pt(220)、Pt(311)、およびPt(222)回折ピークは、それぞれ39.8°、46.3°、67.5°、81.3°、および85.7°を中心としています。これは、S3のPt膜がTiサンプルと比較してより高い結晶化度を示すことを示しています。同じことがS4にも当てはまり、図3a、bのS3と同様のPt回折シグネチャを示します。 Ti(002)-Ti(101)-Pt(111)、Ti( 103)-Pt(220)、およびTi(004)-Pt(311)-Pt(222)回折ピーク。 S2、S3、およびS4のGIXRDパターンの定性的な比較は、S4のTiの結晶化度が少なくともS1と同じレベルであることを意味します。 70.6°のTi(103)ピークは、図3bのPt(220)ピークの明確なショルダーとして観察され、図3aの53.0°のTi(102)ピークは、強度は低いがS4の線幅は狭くなっています。一方、S1とS2には、非常に幅の広いアモルファスのようなピークが見られます。この結果は、GaAs(110)表面の代わりにPt上に堆積した場合のTiの結晶化度の改善を示唆しています。 1と2。

a のサンプルS1〜S4のGIXRDパターン 30〜60°の回折角範囲および( b )60〜90°の範囲。灰色の破線は、拡散X線散乱に起因する指数関数的減衰のベースラインを表しています。垂直の黒い破線は、 a の上部にラベルが付けられた、TiとPtのさまざまな回折面に対応しています。 および b

S1〜S4の金属層のGIXRD分析により、GaAs(110)基板上に堆積したTiおよびPtの結晶化度と、図2bのP1〜P5の合計抵抗結果を相関させることができます。この作業では、主にS1〜S4から取得したGIXRDデータに基づいて、P1〜P5の総抵抗の変化の相関関係に基づいていることを強調することが重要です。 NWの側壁の六角形の形状による金属-NW界面の品質などの他の要因は、P1〜P5で観察される総抵抗変化にほとんど寄与しないと想定しています。 (NH 4 ) 2 S x 表面パッシベーションは、サンプルP1とP3のIV抵抗と全抵抗を比較するとわかるように、GaAs-金属界面の特性に有益な効果をもたらしますが、GaAs(110)表面に直接堆積した場合のTi膜の結晶化度は低くなります。 、S1およびS2で観察されるように。これは、硫黄と生い茂ったTiとの反応の結果である可能性があります。さらに、Tiは金属堆積中に蒸発チャンバー内の残りの不純物と非常に反応性が高く[41]、金属/ GaAs間に追加の層を形成し、したがって接触抵抗を増加させることが報告されています[5]。前に説明したように、P2の接触抵抗の増加は、酸素プラズマ洗浄によって引き起こされる可能性のある表面損傷に起因していました。 S4のようにTiとGaAs(110)表面の間に薄いPt層を追加すると、S1とS2と比較してTi膜の結晶化度が高くなります。この結果は、接触抵抗の減少に関連する、P3の1400kΩからP4の72kΩへの総チャネル抵抗の減少と相関する可能性があります。 RTAは、図2aに示すIVのオーミック特性の増加に加えて、P5の合計チャネル抵抗をさらに40kΩに減少させます。この結果は、使用したアニーリング温度と時間において、PtとGaAs表面の間に有害な反応が発生しないことを示しています[29、30、31]。

結論

金属蒸発前の表面化学処理とBeドープ自己触媒GaAsNWへのオーミック接触の形成の影響を、単一NWの輸送特性と、上に堆積したTi、Pt、およびPt / Ti薄膜の構造分析を相関させることによって調査しました。 GaAs基板:GaAs(110)表面に堆積した場合、Tiは結晶性が低く、NWデバイスの接触抵抗に直接影響することを示しています。 Ti / Pt / Auの前にNWに薄いPt層を堆積すると、BeドープGaAs NWの総電気抵抗が95%減少します。これは、直接堆積した場合のTiよりもPtの結晶化度が高いことに関連しています。 GaAs(110)上。さらに、金属層の熱アニーリングが接触抵抗をさらに低下させることを示します。これらの調査結果は、GaAs NWベースのデバイスへのオーミックコンタクトを設計する際に技術的に重要であり、NWデバイスの総抵抗とオーミック特性における各処理ステップの個々の寄与を示しています(表1を参照)。デバイスのパフォーマンスをさらに向上させるには、個々のステップのパラメータを体系的に最適化する必要があります。特に、NW側壁の金属-半導体界面がデバイスの性能に大きな役割を果たし、III-V半導体材料のさまざまな表面配向に堆積した金属薄膜の結晶化プロセスのさらなる調査への道を開くことを示します。

データと資料の可用性

この調査の結論を裏付けるデータセットは、記事に含まれています。

略語

- FCC:

-

面心立方

- GIXRD:

-

斜入射X線回折

- HCP:

-

六角形-クローズドパック

- IV:

-

電流-電圧

- NW:

-

ナノワイヤー

- RTA:

-

ラピッドサーマルアニーリング

- SEM:

-

走査型電子顕微鏡

ナノマテリアル